高保持电压双极结器件

文献发布时间:2024-04-18 19:44:28

技术领域

本发明涉及双极结器件,尤其是具有高保持电压的双极结器件。

背景技术

在某些技术中,由于保持电压和/或故障电流有限,双极结器件不适合用作静电放电(ESD)器件。提供一种有利的双极结器件,所述双极结器件被配置为具有高保持电压,使得所述器件可以用作ESD器件,所述ESD器件适合用作I/O钳位器(I/O clamp)并且也适合于电源焊盘保护。

发明内容

本文公开了一种结构的实施例。所述结构可包括具有第一表面和与第一表面相对的第二表面的半导体衬底。所述结构还可包括器件(例如,双极结器件)。所述器件可包括半导体衬底内的基极(base)阱区和在半导体衬底的第二表面处与基极阱区相邻的基极接触区。基极阱区和基极接触区可以具有第一类型导电性。所述器件还可包括与半导体衬底的第二表面处的基极阱区相邻但通过隔离区与基极接触区分离的发射极(emitter)接触区。所述发射极接触区可以具有不同于第一类型导电性的第二类型导电性。所述器件还可包括辅助发射极区,其在半导体衬底的第二表面处与基极阱区相邻,并直接与发射极接触区相邻,并具有第一类型导电性。

在结构的一些公开实施例中,发射极接触区和辅助发射极区都可以被分段。具体地,所述结构的一些实施例可包括具有第一表面和与第一表面相对的第二表面的半导体衬底。所述结构还可包括器件(例如,双极结器件)。所述器件可包括半导体衬底内的基极阱区和在半导体衬底的第二表面处与基极阱区相邻的基极接触区。基极阱区和基极接触区都可以具有第一类型导电性。所述器件还可包括与半导体衬底的第二表面处的基极阱区相邻但通过隔离区与基极接触区分离的发射极接触区。发射极接触区可以由分立的发射极接触区段构成,其具有不同于第一类型导电性的第二类型导电性。所述器件还可包括在半导体衬底的第二表面处与基极阱区相邻并且也通过隔离区与基极接触区分离的辅助发射极区。辅助发射极区可以由具有第一类型导电性的分立的辅助发射极区段构成,并且发射极接触区段和辅助接触区段可跨器件的宽度交替。

在一些公开的实施例中,辅助发射极区可以基本上是梳状的。具体地,所述结构的一些实施例可包括具有第一表面和与第一表面相对的第二表面的半导体衬底。所述结构还可包括器件(例如,双极结器件)。所述器件可包括半导体衬底内的基极阱区和在半导体衬底的第二表面处与基极阱区相邻的基极接触区。基极阱区和基极接触区可以具有第一类型导电性。所述器件还可包括与半导体衬底的第二表面处的基极阱区相邻但通过隔离区与基极接触区分开的发射极接触区。发射极接触区可具有不同于第一类型导电性的第二类型导电性。所述器件还可包括辅助发射极区,其与半导体衬底的第二表面处的基极阱区相邻,并具有第一类型导电性。辅助发射极区可具体地基本上是梳状的。也就是说,其可包括横向延伸穿过器件宽度的辅助发射极区主体,以及基本上垂直于辅助发射极区主体定向的辅助发射极区延伸部,所述辅助发射极区延伸部横向朝向发射极接触区延伸并紧邻发射极接触区。

附图说明

通过参考附图的以下详细描述,可以更好地理解本发明,附图不一定按比例绘制,其中:

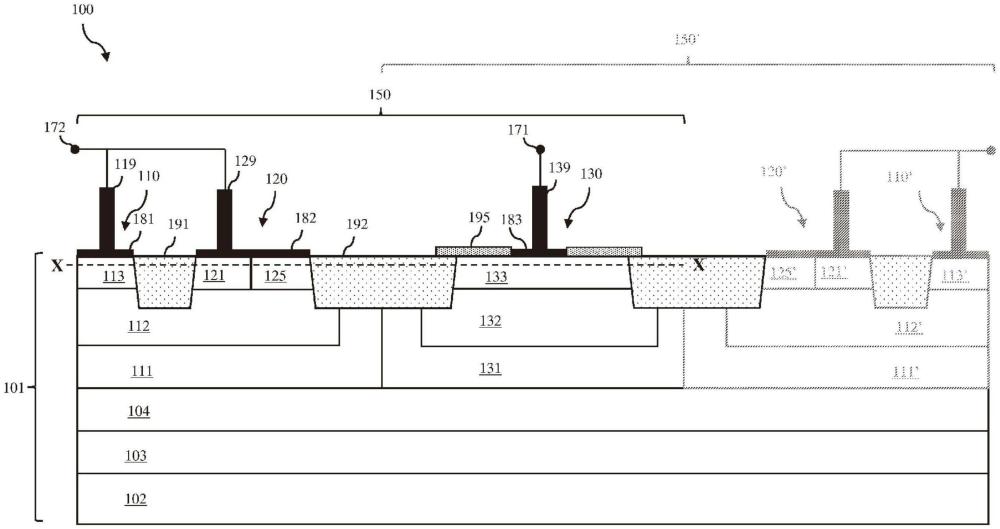

图1A和图1B为包括被配置为具有高保持电压的双极结器件的半导体结构的实施例的不同截面图;

图1C为图1A中所示器件的替代配置的截面图;

图2A和图2B为包括被配置为具有高保持电压的双极结器件的半导体结构的实施例的不同截面图;

图3A和图3B为包括被配置为具有高保持电压的双极结器件的半导体结构的实施例的不同截面图;

图4A和图4B为包括被配置为具有高保持电压的双极结器件的半导体结构的实施例的不同截面图;

图5A和图5B为包括被配置为具有高保持电压的双极结器件的半导体结构的实施例的不同截面图;

图5C为图5A中所示器件的替代配置的截面图;

图6A和图6B为包括被配置为具有高保持电压的双极结器件的半导体结构的实施例的不同截面图;

图7A和图7B为包括被配置为具有高保持电压的双极结器件的半导体结构的实施例的不同截面图;以及

图8A和图8B为包括被配置为具有高保持电压的双极结器件的半导体结构的实施例的不同截面图。

具体实施方式

如上所述,在某些技术中,由于保持电压和/或故障电流有限,双极结器件不适合用作静电放电(ESD)器件。

鉴于上述情况,本文公开了包括双极结器件的半导体结构的实施例,所述双极结器件被配置为具有高保持电压,从而可以用作静电放电(ESD)器件,所述静电放电(ESD)器件适合用作I/O钳位器,也适用于电源焊盘保护。双极结器件由各种衬底内掺杂区和,可选的,形成基极、集电极(collector)和发射极端子的半导体层组成(如下面更详细讨论的)。由于独特配置的发射极端子,实现了高保持电压。具体地,所述器件可包括具有第一类型导电性的基极阱区。发射极端子可以包括邻近基极阱区(例如,在基极阱区内和/或之上)的发射极接触区和辅助发射极区,所述发射极接触区具有第二类型导电性,所述辅助发射极区邻接所述发射极接触区并具有比基极阱区高的导电性水平的第一类型导电性。实施例可以根据发射极接触区和辅助发射极区的形状而变化。例如,在一些实施例中,它们都可以在器件的整个宽度上延伸。在其他实施例中,它们都可以用具有不同类型导电性的段分段,这些段可横跨器件的宽度交替。在又一些实施例中,辅助发射极区是梳状的,其主体部分延伸穿过器件的宽度,并且延伸部分垂直于主体部分,并且在分段发射极接触区的离散段之间延伸或者在梳状发射极接触区的延伸部分之间延伸。实施例还可以根据用于将集电极端子与发射极端子隔离的结构以及根据硅化物层覆盖的区域而变化。

更具体地,参考图1A至图1B、图2A至图2B、图3A至图3B、图4A至图4B、图5A至图5B、图6A至图6B、图7A至图7B和图8A至图8B,本文分别公开了半导体结构100、200、300、400、500、600、700和800的实施例,包括双极结器件150、250、350、450、550、650、750、850,双极结器件被配置为具有高保持电压,使得其可以用作静电放电(ESD)器件,其适合用作I/O钳位器并且也适合于电源焊盘保护。

双极结器件150、250、350、450、550、650、750、850可以是NPN器件。或者,双极结器件150、250、350、450、550、650、750、850可以是PNP器件。在下面的讨论中,参考掺杂的半导体区和/或层,以具有第一类型导电性或不同于第一类型导电性的第二类型导电性。应当理解,根据双极结器件是NPN器件还是PNP器件,第一类型导电性和第二类型导电性分别是P型导电性和N型导电性,或者分别是N型导电性和P型导电性。具体地,如果双极结器件是NPN器件,则第一类型导电性是指P型导电性,而第二类型导电性指N型导电性。然而,如果双极结器件是PNP器件,则第一类型导电性指N型导电性,而第二类型导电性则指P型导电性。参见下文关于可用于半导体材料以实现P型导电性或N型导电性的不同掺杂剂的详细讨论。

半导体结构100、200、300、400、500、600、700、800可包括单晶半导体衬底101、201、301、401、501、601、701、801。所述单晶半导体衬底可以是例如具有底表面(本文中称为第一表面)和与底表面相对的顶表面(本文称为第二表面)的块体硅衬底(如图所示)。

半导体衬底101、201、301、401、501、601、701、801可具有与底表面相邻的下部102、202、302、402、502、602、702、802,并进行掺杂,从而在相对较低的导电性水平下具有第一类型导电性。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,下部102、202、302、402、502、602、702、802可以具有P导电性。

半导体衬底101、201、301、401、501、601、701、801可进一步包括衬底内的第一掩埋阱区103、203、303、403、503、603、703、803,位于下部102、202、302、402、502、602、702、802的上方,与半导体衬底的顶表面物理分离,并且被掺杂以具有相对低的导电性水平下的第二类型导电性。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,第一掩埋阱区103、203、303、403、503、603、703、803可以是N掩埋阱区(也称为HVDNW)。

半导体衬底101、201、301、401、501、601、701、801还可以包括衬底内的第二掩埋阱区104、204、304、404、504、604、704、804,位于第一掩埋阱区103、203、303、403、503、603、703、803的上方,与半导体衬底的顶表面物理分离,并且被掺杂以在相对低的导电性水平下但在比衬底的下部102、202、302、402、502、602、702、802更高的导电性水平上,具有第一类型导电性。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,第二掩埋阱区104、204、304、404、504、604、704、804可以是P掩埋阱区(也称为PWHV)。

半导体结构100、200、300、400、500、600、700、800还可以包括双极结器件150、250、350、450、550、650、750、850。器件150、250、350、450、550、650、750、850可以是三端子装置,包括:基极端子110、210、310、410、510、610、710、810、集电极端子130、230、330、430、530、630、730、830和发射极端子120、220、320、420、520、620、720、820。

基极端子110、210、310、410、510、610、710、810可包括基极阱区111、211、311、411、511、611、711、811,其位于衬底内,从衬底的顶表面延伸至第二掩埋阱区104、204、304、404、504、604、704、804,并且其具有比第二掩埋阱区104、204、304、404、504、604、704、804更高的导电性水平的第一类型导电性。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,基极阱区111、211、311、411、511、611、711、811可以是P阱区(也称为HVPDDD D)。

可选地,基极端子110、210、310、410、510、610、710、810可包括额外的基极阱区112、212、312、412、512、612、712、812,其位于衬底内,特别是在基极阱区111、211、311、411、511、611、711、811内,并且比基极阱区111、211、311、411、511、611、711、811浅。也就是说,附加基极阱区112、212、312、412、512、612、712、812可以从衬底的顶表面延伸到高于第二掩埋阱区104、204、304、404、504、604、704、804的顶部水平的某个深度,使得附加基极阱区的底部高于基极阱区的底部水平。附加基极阱区112、212、312、412、512、612、712、812也可以比基极阱区111、211、311、411、511、611、711、811窄。也就是说,附加基极阱区112、212、312、412、512、612、712、812可以位于基极阱区111、211、311、411、511、611、711、811内,使得附加基极阱区的侧边与基极阱区的侧边隔开一定距离。在任何情况下,附加基极阱区112、212、312、412、512、612、712、812可以具有比基极阱区111、211、311、411、511、611、711、811高的导电性水平的第一类型导电性。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,附加基极阱区112、212、312、412、512、612、712、812可以像基极阱区一样是P阱区(也称为MVPSD),但处于更高的P型导电性水平。

基极端子110、210、310、410、510、610、710、810还可包括基极接触区113、213、313、413、513、613、713、813,其与衬底的顶表面的基极阱区111、211、311、411、511、611、711、811(以及如果适用于其中的附加基极阱区112、212、312、412、512、612、712、812)相邻。例如,基极接触区113、213、313、413、513、613、713、813可以是衬底内顶表面处的浅掺杂注入区。替代地,基极接触区113、213、313、413、513、613、713,813可以是直接邻近半导体衬底的顶表面的掺杂单晶半导体层(例如,原位掺杂外延硅层或某些其他合适的半导体材料的原位掺杂外延层),所述半导体衬底的顶表面在基极阱区上方对准并与之接触(如果适用,在附加基极阱区上方对准并与之接触)。在任何情况下,基极接触区113、213、313、413、513、613、713、813可具有处于比所述可选的附加基极阱区更高的第一类型导电性水平的第一类型导电性。因此,第一类型导电性水平是渐变的(graded),尤其是,从第二掩埋阱区通过基极阱区和附加基极阱区(如果适用)增加到基极接触区。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,基极接触区113、213、313、413、513、613、713、813可以是P+基极接触区,并且P型导电性水平可以是渐变的,特别是可以从掩埋的P阱,通过基极P阱和附加基极P阱(如果适用)增加到P+基极接触区。

发射极端子120、220、320、420、520、620、720、820可包括发射极接触区121、221、321、421、521、621、721、821,其与衬底的第二表面处的基极阱区111、211、311、411、511、611、711、811(或其中的附加基极阱区112、212、312、412、512、612、712、812,如果适用)相邻(例如,在其内或其上)。例如,发射极接触区121、221、321、421、521、621、721、821可以是衬底内的顶表面处的浅掺杂注入区。替代地,发射极接触区121、221、321、421、521、621、721,821可以是直接邻接半导体衬底的顶表面的掺杂单晶半导体层(例如,原位掺杂外延硅层或某些其他合适的半导体材料的原位掺杂外延层),所述半导体衬底的顶表面在基极阱区上方对准并与之接触(并且如果适用的话,在附加基极阱区的上方对准并与之接触)。在任何情况下,发射极接触区121、221、321、421、521、621、721、821可以在相对高的第一类型导电性水平,特别是在比第一掩埋阱区103、203、303、403、503、603、703、803更高的第二类型导电性水平下,具有第二类型导电性。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,发射极接触区121、221、321、421、521、621、721、821可以是N+发射极接触区。

应注意,隔离区191、291、391、491、591、691、791、891可位于基极阱区111、211、311、411、511、611、711、811(或如果适用的话,其中的附加基极阱区112、212、312、412、512、612、712、812)内,其横向位于基极接触区113、213、313、413、513、613、713、813和发射极接触区121、221、321、421、521、621、721、821之间并与之邻接。隔离区191、291、391、491、591、691、791、891例如可以是浅沟槽隔离(shallow trench isolation;STI)区,如图所示,或者替代地,是硅的局部氧化(local oxidation of silicon;LOCOS)区。在任何情况下,隔离区可例如延伸到衬底中低于基极接触区113、213、313、413、513、613、713、813和发射极接触区121、221、321、421、521、621、721、821的底部水平,并且高于基极阱区(以及如果适用的话,附加基极阱区)的底部水平的深度。

发射极端子120、220、320、420、520、620、720、820还可包括辅助发射极区125、225、325、425、525、625、725、825,其与衬底的第二表面处的基极阱区111、211、311、411、511、611、711、811(或者如果适用,其中的附加基极阱区112、212、312、412、512、612、712、812)相邻(例如,在其内或其上)。例如,辅助发射极区125、225、325、425、525、625、725、825可以是衬底内的顶表面处的浅掺杂注入区。替代地,辅助发射极区125、225、325、425、525、625、725、825可以是紧邻半导体衬底的顶表面的掺杂单晶半导体层(例如,原位掺杂外延硅层或某些其他合适的半导体材料的原位掺杂外延层),所述半导体衬底的顶表面在基极阱区上方对准并与之接触(如果适用,在附加基极阱区上方对准并与之接触)。在任何情况下,辅助发射极区125、225、325、425、525、625、725、825可以在相对高的第一类型导电性水平(例如,在与基极接触区113、213、313、413、513、613、713、813相同的水平上,并且在比附加基极阱区(如果适用)和基极阱区更高的水平上)具有第一类型导电性,并且可以紧邻发射极接触区121、221、321、421、521、621、721、821。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,辅助发射极区125、225、325、425、525、625、725、825可以是紧邻N+发射极接触区的P+辅助发射极区。

集电极端子130、230、330、430、530、630、730、830可包括集电极阱区131、231、331、431、531、631、731、831,其位于衬底内,并横向紧邻基极阱区111、211、311、411、511、611、711、811,所述基极阱区从衬底的顶表面延伸至第二掩埋阱区104、204、304、404、504、604、704、804,并具有比第一掩埋阱区103、203、303、403、503、603、703、803更高的导电性水平的第二类型导电性。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,集电极阱区131、231、331、431、531、631、731、831可以是N阱区(也称为HVNDDD)。

可选地,集电极端子130、230、330、430、530、630、730、830可以包括附加集电极阱区132、232、332、432、532、632、732、832,其位于衬底内,特别是集电极阱区131、231、331、431、531、631、731、831内,并且比集电极阱区131、231,331、431,531、731、831浅。也就是说,附加集电极阱区132、232、332、432、532、632、732、832可以从衬底的顶表面延伸到高于第二掩埋阱区104、204、304、404、504、604、704、804的顶部水平的某个深度,使得附加集电极阱区的底部高于集电极阱区的底部水平。附加集电极阱区132、232、332、432、532、632、732、832也可以比集电极阱区131、231、331、431、531、631、731、831窄。也就是说,附加集电极阱区132、232、332、432、532、632、732、832可以位于集电极阱区131、231、331、431、531、631、731、831内,使得附加集电极阱区的侧部与集电极阱区的侧部隔开一定距离。在任何情况下,附加集电极阱区132、232、332、432、532、632、732、832可以具有比集电极阱区131、231、331、431、531、631、731、831更高的导电性水平的第二类型导电性。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,附加集电极阱区132、232、332、432、532、632、732、832可以像集电极阱区一样是N阱区(也称为NW),但处于更高的N型导电性水平。

集电极端子130、230、330、430、530、630、730、830还可以包括集电极接触区133、233、333、433、533、633、733、833,其邻近衬底的顶表面处的集电极阱区131、231、331、431、531、631、731、831(如果适用,其中的附加集电极阱区132、232、332、432、532、632、732、832)。例如,集电极接触区133、233、333、433、533、633、733、833可以是衬底内的顶表面处的浅掺杂注入区。替代地,集电极接触区133、233、333、433、533、633、733,833可以是紧邻半导体衬底的顶表面的掺杂单晶半导体层(例如,原位掺杂外延硅层或某些其他合适半导体材料的原位掺杂外延层),所述半导体衬底的顶表面在集电极阱区上方对准并与之接触(并且如果适用的话,在附加集电极阱区上方对准并与之接触)。在任何情况下,集电极接触区133、233、333、433、533、633、733、833可以在比可选的附加集电极阱区更高的第二类型导电性水平下具有第二类型导电性。因此,第二类型导电性水平是渐变的,特别是,从集电极阱区并通过附加集电极阱区(如果适用)增加到集电极接触区。例如,当双极结器件150、250、350、450、550、650、750、850是NPN器件时,集电极接触区133、233、333、433、533、633、733、833可以是N+集电极接触区,并且N型导电性水平可以是渐变的,特别是,可以从集电极N阱通过附加集电极N阱(如果适用)增加到N+集电极接触区。

上述半导体结构实施例可根据发射极接触区121、221、321、421、521、621、721、821和辅助发射极区125、225、325、425、525、625、725、825的形状和相对位置而变化。

例如,在图1A至图1B的半导体结构100的双极结器件150和图5A至图5B的半导体结构500的双极结器件550中,发射极接触区121、521和辅助发射极区125、525可以是基本上平行的矩形区域,其延伸穿过器件150、550的整个宽度。在这些实施例中,如图1B和图5B所示,发射极接触区121、521可以平行并紧邻隔离区191、591,辅助发射极区125、525可以平行并紧邻发射极接触区121、521。因此,隔离区191、591被横向定位在基极接触区113、513和发射极接触区121、521之间并与之平行,且发射极接触层121、521被横向地设置在隔离区191、591与辅助发射极区125、525之间并与之平行。

在图2A至图2B的半导体结构200的双极结器件250和图6A至图6B的半导体结构600的双极结器件650中,发射极接触区221、621可以被分段并且辅助发射极区225、625可以基本上是梳状的。具体地,发射极接触区221、621可以包括分立的发射极接触区段224、624。发射极接触区段224、624可以在器件的宽度上以一条直线定向并且彼此物理分离。每个发射极接触区段224、624可以具有紧邻隔离区291、691的第一端和与第一端相对的第二端,使得每个发射极接触区段224、624基本上垂直于隔离区291、691定向,并且进一步使得每个发射极接触区段224、624通过隔离区291、691与基极接触区213、613分离。如上所述,辅助发射极区225、625可以基本上是梳状的。也就是说,辅助发射极区225、625可以包括辅助发射极区主体226、626,其延伸穿过器件的宽度。辅助发射极区225、625还可以包括辅助发射极区延伸部227、627。辅助发射极区延伸部227、627可以从辅助发射极区主体226、626横向延伸到隔离区291、691(即,辅助发射极区延伸部227、627可以基本上垂直于辅助发射极区主体226、626和隔离区291、691并在其之间横向延伸),使得它们通过隔离区291、691与基极接触区213、613分离。此外,辅助发射极区延伸部227、627可以位于任一侧并紧邻发射极接触区段224、624,使得辅助发射极区延伸部和发射极接触区段可横跨器件的宽度交替。

在图3A至图3B的半导体结构300的双极结器件350和图7A至图7B的半导体结构700的双极结器件750中,发射极接触区321、721和辅助发射极区325、725都可以被分段。具体地,发射极接触区321、721可以包括分立的发射极接触区段324、724。发射极接触区段324、724可以在器件的宽度上以一条直线定向并且彼此物理分离。每个发射极接触区段324、724可以具有紧邻隔离区391、791的第一端和与第一端相对的第二端,使得每个发射极接触区段324、724基本上垂直于隔离区391、791定向,并且进一步使得每个发射极接触区段324、724通过隔离区391、791与基极接触区313、713分离。辅助发射极区325、725可以包括分立的辅助发射极区段328、728。辅助发射极区段328、728可以与发射极接触区段在同一直线上定向,并且不同的段可横跨器件的宽度交替(例如,每个辅助发射极区段可以横向定位在一对发射极接触区段之间并与之紧邻)。每个辅助发射极区段328、728可具有紧邻隔离区391、791的第一端和与第一端相对的第二端,使得辅助发射极区段328、728垂直于隔离区391、791,且通过隔离区391、791与基极接触区313、713进一步分离。

在图4A至图4B的半导体结构400的双极结器件450和图8A至图8B的半导体结构800的双极结器件850中,发射极接触区421、821和辅助发射极区425、825可具有相互咬合(interlocking)的梳状形状。具体地,发射极接触区421、821可以基本上是梳状的。也就是说,发射极接触区421、821可包括发射极接触区主体422、822,其延伸穿过器件的宽度,平行于隔离区491、891,并且具有紧邻隔离区491、891的第一侧和与第一侧相对的第二侧。发射极接触区421、821还可包括从发射极接触区主体422、822的第二侧横向延伸且彼此物理分离的发射极接触区延伸部423、823。辅助发射极区425、825可以类似地基本上是梳状的,但面向相反的方向,使得两个区域交错。也就是说,辅助发射极区425、825可以包括辅助发射极区主体426、826,其延伸穿过器件的宽度,平行于发射极接触区主体422、822,并且具有与发射极接触区相邻的第一侧和与第一侧相对的第二侧。辅助发射极区425、825还可以包括辅助发射极区延伸部427、827,其从辅助发射极区主体426、826的第一侧横向延伸到位于发射极接触区延伸部423、823之间的发射极接触区主体422、822,使得它们紧邻发射极接触区延伸部423、823并位于发射极接触区延伸部423、823之间。

半导体结构100、200、300、400、500、600、700、800可以进一步包括金属硅化物层。金属硅化物层可包括:基极接触区113、213、313、413、513、613、713、813上的基极硅化物层181、281、381、481、581、681、781、881;发射极接触区121、221、321、421、521、621、721、821上的发射极硅化物层182、282、382、482、582、682、782、882,以及集电极接触区133、233、333、433、533、633、733、833上的集电极硅化物层183、283、383、483、583、683、783、883。应当注意,发射极硅化物层182也可以部分或完全延伸到辅助发射极区125、225、325、425、525、625、725、825上方,如图1A、图2A、图3A、图4A、图5A、图6A、图7A和图8A所示。然而,可替代地,辅助发射极区可以是无硅化的,因此是浮置的(floating)。例如,参见图1C,其示出了器件150的替代配置,其中,发射极硅化物层182不在发射极接触区121和辅助发射极区125之间的结上横向延伸,使得辅助发射极区125保持浮置。参见图5C,其示出了器件550的替代配置,其中,发射极硅化物层582不在发射极接触区521和辅助发射极区525之间的结上横向延伸,使得辅助发射极区525保持浮置。可选地,尽管未示出,辅助发射极区225、325、425、625、725、825可以类似地是无硅化的,因此是浮置的。在任何情况下,这些金属硅化物层可以是例如钴硅化物(CoSi)、镍硅化物(NiSi)、钨硅化物(WSi)、钛硅化物(TiSi)或任何其他合适的金属硅化物材料的层。这三个金属硅化物层(即,基极硅化物层、发射极硅化物层和集电极硅化物层)是分立的层,并且彼此物理分离。也就是说,这三个层中的任何一个都不与其他层连续,以防止基极端子110、210、310、410、510、610、710、810、发射极端子120、320、420、520、620、720、820(包括发射极接触区和辅助发射极区),和/或集电极端子130、230、330、430、530、630、730、830(包括集电极阱区131、231、331、431、531、631、731、831、附加集电极阱区132、232、332、432、532、632、732、832(如果适用)和集电极接触区133、233、333、433、533、633、733、833中的任何一个)的耦合,特别是通过金属硅化物的耦合。

在每个半导体结构实施例中,隔离区191、291、391、491、591、691、791、891确保基极硅化物层181、281、381、481、581、681、781、881和发射极硅化物182、282、382、482、582、682、782、882不是连续的层(即确保基极端子和发射极端子没有特别地通过金属硅化物短路在一起)。然而,这些实施例在特定的结构配置方面有所不同,所述特定的结构配置确保发射极硅化物层182、282、382、482、582、682、782、882和集电极硅化物层183、283、383、483、583、683、783、883也不是连续层(即,确保发射极端子和集电极端子没有特别地通过金属硅化物短路在一起)。

例如,在一些实施例中,附加隔离区192、292、392、492可以确保发射极硅化物层182、282、382、482和集电极硅化物层183、283、383、483不是连续的层(即,确保发射极端子和集电极端子没有特别地通过金属硅化物短路在一起)(例如,分别参见图1A至图1B、图2A至图2B、图3A至图3B、图4A至图4B的半导体结构100、200、300、400)。此附加隔离区192、292、392、492可以是例如如图所示的附加STI区,或者替代地是附加LOCOS区。在任何情况下,附加隔离区192、292、392、492可以横越基极阱区111、211、311、411和集电极阱区131、231、331、431之间的结,从顶表面延伸到衬底中的一个深度,此深度低于发射极接触区121、221、321、421、辅助发射极区125、225、325、425、集电极接触区133、233、333、433的底部水平,并高于集电极和基极阱区的底部水平(并且如果适用的话,高于附加基极和附加集电极阱区的底部水平)。附加隔离区192、292、392、492可以在一个方向上横向延伸到辅助发射极区125、225、325、425(例如,在基极阱区111、211、311、411和附加基极阱区112、212、312、412之间的垂直界面的上方,如果存在的话),并且在与集电极接触区133、233、333、433相反的方向上横向地延伸(例如,在集电极阱区131、231、331、431和附加集电极阱区132、232、332、432之间的垂直界面的上方,如果存在的话)。应当注意,给定图3A至图3B的半导体结构300中的发射极端子的配置,在此实施例中,附加隔离区392接触每个发射极接触区段324和每个辅助发射极区段328的一端。在任何情况下,在这些实施例中,发射极端子120、220、320、420的发射极接触区121、221、321、421和辅助发射极区125、225、325、425可以在其上具有发射极硅化物层182、282、382、482。此外,在这些实施例中,集电极端子130、230、330、430的集电极接触区133、233、333、433可以基本上被集电极硅化物层183、283、383、483(未示出)完全覆盖。可替代地,介电层195、295、395、495,特别是相对薄的硅化物阻挡(SAB)层(例如,薄氮化硅层或适合于在处理期间阻挡金属硅化物层形成的一些其他合适介电层的薄层)可以覆盖紧邻附加隔离区192、292、392、492的集电极接触区133、233、333、433的边缘部分,使其在附加隔离区192、292、392、492和集电极硅化物层183、283、383、483之间横向延伸。可选地,如图1C所示,介电层195(即,SAB层)可以进一步被图案化,以便完全覆盖辅助发射极区125,以防止在其上形成发射极硅化物层182,从而确保辅助发射极区保持未硅化和浮置。虽然未示出,但是可以执行图2A、图3A、图4A的介电层295、395、495(即,SAB层)的更复杂的图案化,以完全覆盖辅助发射极区225、325、425,因此发射极硅化物层282、382、482仅形成在发射极接触区221、321、421上,使得辅助发射极区225、325、425保持未硅化和浮置。

在其他实施例中,介电层596、696、796、896可以确保发射极硅化物层582、682、782、882和集电极硅化物层583、683、783、883不是连续层(即,确保发射极端子和集电极端子没有特别地通过金属硅化物短路在一起)(例如,分别参见图5A至图5B、图6A至图6B、图7A至图7B、图8A至图8B的半导体结构500、600、700、800)。介电层596、696、796、896可以是相对薄的硅化物阻挡(SAB)层(例如,薄的氮化硅层或适合于在处理期间阻挡金属硅化物层形成的一些其他合适介电层的薄层)。介电层596、696、796、896可以被图案化,使其横越基极阱区511、611、711、811和集电极阱区531、631、731、831之间的结,使其在一个方向上横向延伸到辅助发射极区525、625、725,825(例如,在基极阱区511、611、711、811和附加基极阱区512、612、712、812之间的垂直界面的上方,如果存在的话),并且在与集电极接触区533、633、733、833相反的方向上(例如,在集电极阱区531、631、731、831和附加集电极阱区532、632、732、832之间的垂直界面的上方,如果存在的话)。应当注意,取决于发射极端子的配置,介电层596、696、796、896可以部分地或可选地完全覆盖辅助发射极区525、625、725、825。例如,在半导体结构500中,介电层596可以被图案化,使其横向延伸到辅助发射极区525而不完全覆盖辅助发射极区525,使得发射极硅化物层582形成在发射极接触区521和辅助发射极区525两者上(如图5A所示)。可替代地,在半导体结构500中,介电层596可以被图案化,使其完全覆盖辅助发射极区525,因此,只有发射极接触区521被发射极硅化物层582覆盖,并且使得辅助发射极区525保持未硅化和浮置(如图5C所示)。在图6A至图6B的半导体结构600中,介电层696可以被图案化,使其横向延伸到梳状辅助发射极区625上,并且可选地使其完全覆盖辅助发射极区主体626,从而使得辅助发射极区625的分立发射极接触区624和辅助发射极区延伸部627被发射极硅化物层682覆盖(如图所示)。在图7A至图7B的半导体结构700中,介电层796可以被图案化,使其仅横向延伸到发射极接触区段724和辅助发射极区段728的相邻端上(如图所示)。在图8A至图8B的半导体结构800中,介电层896可以被图案化,使其横向延伸到梳状辅助发射极区825上,并且可选地使其完全覆盖辅助发射极区主体826,使得整个发射极接触区821和辅助发射极区825的辅助发射极区延伸部827被发射极硅化物层882覆盖(如图所示)。应当理解,虽然未示出,但可执行图6A、图7A、图8A的介电层696、796、896(即,SAB层)的更复杂的图案化,以完全覆盖辅助发射极区625、725、825,因此发射极硅化物层682、782、882仅位于发射极接触区621、721、821上,使得辅助发射极区保持未硅化和浮置。

可选地,半导体结构100、200、300、400、500、600、700、800可包括附加双极结器件150’、250’、350’、450’、550’、650’、750’、850’,如图所示。双极结器件150、250、350、450、550、650、750、850和附加双极结器件150'、250’、350’、450’、550’、650’、750’、850’可以是基本相同的,但在共享集电极端子的任一侧上是镜像/对称结构,如图所示。

在任何情况下,端子接触件都可以在金属硅化物层上着陆(land),以接触各个接触区。即,至少一个基极端子接触件119、219、319、419、519、619、719、819可着陆在基极接触区113、213、313、413、513、613、713、813(或其上的基极硅化物层)上,至少一个发射极端子接触件129、229、329、429、529、629、729、829可以着陆在发射极接触区121、221、321、421、521、621、721、821(或其上的发射极硅化物层)上,至少一个集电极端子接触件139、239、339、439、539、639、739、839可以着陆在集电极接触区133、233、333、433、533、633、733、833(或其上的集电极硅化物层)上。应当理解,辅助发射极区可以在器件操作期间保持浮置(例如,当其未通过其上的硅化物层电性连接到发射极接触区并且其上没有接触焊盘时)。

应注意,由于第一掩埋阱区103、203、303、403、503、603、703、803和第二掩埋阱区104、204、304、504、604、704、804的组合,双极结器件150、250、350、450、650、750、850、850与半导体衬底101、201、301、401、501、601、701、801的下部102、202、302、402、502、602、702、802基本上完全垂直隔离。

因此,上述双极结器件150、250、350、450、550、650、750、850可以用作静电放电(ESD)器件。例如,在用作ESD器件的NPN型双极结器件的情况下,集电极端子接触件139、239、339、439、539、639、739、839可以耦合到第一焊盘171、271、371、471、571、671、771、871(例如,输入/输出(I/O)焊盘,其例如便于芯片和芯片封装的外部引脚之间的输入和/或输出信号传输;电源焊盘,其例如将芯片连接到电源线(例如,Vdd或Vss)等),其还耦合到由ESD器件保护的器件或电路。基极端子接触件119、219、319、419、519、619、719、819和发射极端子接触件129、229、329、429、529、629、729、829可以耦合到接地的第二焊盘172、272、372、472、572、672、772、872。在这种情况下,当第一焊盘171、271、371、471、571、671、771、871上的电压电平高到足以对被保护的器件或电路造成损坏时,NPN型双极结器件将导通并分流电流离开被保护的器件或电路。

应注意,在双极结器件150、250、350、450、550、650、750、850中,辅助发射极区125、225、325、425、525、625、725、825(如上所述,其邻接并具有与发射极接触区121、221、321、421、521、621、721、821不同的导电类型)用于增加器件的保持,而不会导致器件面积的任何显著相应增加。在设计期间,可以选择性地调整(例如,基于模拟结果)发射极接触区121、221、321、421、521、621、721、821和辅助发射极区125、225、325、425、525、625、725、825(包括但不限于,发射极接触区与辅助发射极区的面积比率、发射极接触区和辅助发射极区延伸部/段的数量、发射极接触区和辅助发射极区的相互咬合形状、发射极接触区或其段/延伸部上的接触件数量等)的具体配置,以调节寄生横向双极增益(parasitic lateralbipolar gain),提高锁存抗扰度(latch-up immunity),调节快速回跳机制(snapbackmechanism),调节保持电压,从而优化ESD性能。

本领域技术人员将认识到,包括双极结器件150、250、350、450、550、650、750、850的上述半导体结构100、200、300、400、500、600、700、800,可以使用前段工艺(FEOL)处理(可能包括但不限于浅沟槽隔离(STI)或LOCOS区形成,掺杂剂注入以形成掩埋阱、阱和其他掺杂注入区,可选的原位掺杂外延半导体沉积以形成附加掺杂区,硅化物阻挡(SAB)层形成和图案化,硅化物层形成等),中段工艺(MOL)处理(可能包括但不限于层间介电质沉积和接触件形成),以及后段工艺(BEOL)处理(可能包括但不限于将接触件连接到焊盘/其他器件的互连形成)。然而,这种FEOL、MOL和BEOL处理可以以新颖的方式(例如,使用特定配置的掩模/图案化步骤等)执行,所述新颖的方式已被建立以确保双极结器件150、250、350、450、550、650、750、850具有以上详细描述的各种特征,包括但不限于:(1)发射极端子120、220、320、420、520、620、720、820包括:在具有第一类型导电性的基极阱区内的具有第二类型导电性的发射极接触区121、221、321、421、521、621、721、821,以及邻接发射极接触区121、221、321、421、521、621、721、821并具有第一类型导电性的辅助发射极区125、225、325、425、525、625、725、825;(2)所述第一类型导电性水平从第二掩埋阱区104、204、304、504、604、704、804(其例如具有比衬底的下部102、202、302、402、502、602、702、802更高的第一类型导电性水平),到基极阱区111、211、311、411、511、611、711、811,到附加基极阱区112、212、312、412、512、612、712、812(如果存在),最后到基极接触区113、213、313、413、513、613、713、813向上渐变(例如,逐步增加);(3)所述第二类型导电性水平也从集电极阱区131、231、331、431、531、631、731、831(其例如具有比第一掩埋阱区103、203、303、403、503、603、703、803更高的第二类型导电性水平),到附加集电极阱区132、232、332、432、532、632、732、832(如果存在),再到集电极接触区133、233、333、433、533、633、733、833向上渐变(例如,逐步增加);以及(4)由于第一阱区和第二阱区,与半导体衬底101、201、301、401、501、601、701、801的下部102、202、302、402、502、602、720、802基本上完全垂直隔离。

应理解,在上述结构和方法中,半导体材料是指其导电性能可通过掺杂杂质而改变的材料。示例性半导体材料包括例如硅基半导体材料(例如,硅、硅锗、碳化硅锗、碳化硅等)和III-V族化合物半导体(即,通过将III族元素如铝(Al)、镓(Ga)或铟(In)与V族元素如氮(N)、磷(P)、砷(as)或锑(Sb)组合而获得的化合物)(例如,GaN、InP、GaAs或GaP)。纯半导体材料,更具体地,为了增加导电性而未掺杂杂质的半导体材料(即,未掺杂的半导体材料)在本领域中被称为本征半导体。为了提高导电性而掺杂有杂质的半导体材料(即,掺杂半导体材料)在本领域中被称为非本征半导体,并且将比由相同基材制成的本征半导体更具导电性。也就是说,非本征硅将比本征硅更具导电性;非本征硅锗将比本征硅锗更具导电性,等等。此外,应当理解,可以使用不同的杂质(即,不同的掺杂剂)来实现不同的导电类型(例如,P型导电性和N型导电性),并且掺杂剂可以根据所使用的不同半导体材料而变化。例如,硅基半导体材料(例如,硅、硅锗等)通常掺杂有III族掺杂剂(例如硼(B)或铟(In)),以实现P型导电性,而硅基半导体半导体材料通常掺杂有V族掺杂剂(例如砷(as)、磷(P)或锑(Sb)),以实现N型导电性。氮化镓(GaN)基半导体材料通常掺杂有镁(Mg)以实现P型导电性,并掺杂有硅(Si)或氧以实现N型导电性。本领域技术人员还将认识到,不同的导电性水平将取决于给定半导体区域中掺杂剂的相对浓度水平。此外,当一个半导体区或层被描述为处于比另一个半导体区或层更高的导电性水平时,它比另一半导体区或半导体层更导电(电阻更小);然而,当一个半导体区或层被描述为处于比另一个半导体区或层更低的导电性水平时,其导电性(电阻)比其他半导体区或半导体层低。

此外,上述方法用于制造集成电路芯片。由此产生的集成电路芯片可由制造商以原始晶片形式(即,作为具有多个未封装芯片的单个晶片)、裸管芯或封装形式进行分配。在后一种情况下,芯片安装在单个芯片封装(例如塑料载体,带有固定到主板或其他更高级别载体的引线)或多芯片封装(如陶瓷载体,具有表面互连或掩埋互连之一或两者)中。在任何情况下,芯片然后与其他芯片、分立电路元件和/或其他信号处理设备集成,作为(a)中间产品(例如主板)或(b)最终产品的一部分。最终产品可以是包括集成电路芯片的任何产品,从玩具和其他低端应用到具有显示器、键盘或其他输入设备和中央处理器的高级计算机产品。

应当理解,此处使用的术语是为了描述所公开的结构和方法,而不是限制性的。例如,如本文所用,单数形式“一”、“一个”和“所述”也包括复数形式,除非上下文另有明确说明。此外,如本文所用,术语“包括”和/或“包含”指定了所述特征、整数、步骤、操作、元素和/或组件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元素、组件和/或其组的存在或添加。此外,如本文所用,术语“右”、“左”、“垂直”、“水平”、“顶部”、“底部”、“上部”、“下部”、“下方”、“下层”、“上方”、“上覆”、“平行”、“竖直”等旨在描述图中所示的相对位置(除非另有说明),术语“碰触”、“直接接触”、“邻接”、“直接相邻”、“紧邻”等旨在表示至少一个元件与另一个元件物理接触(没有其他元件分隔所述元件)。术语“横向”在本文中用于描述元件的相对位置,更具体地,用于指示元件位于另一元件的侧面,而不是位于另一个元件的上方或下方,如这些元件在附图中被定向和示出的。例如,横向邻近另一元件定位的元件将在另一元件旁边,横向紧邻另一元件设置的元件将直接在另一个元件旁边,而横向围绕另一元件的元件将与另一元件外部侧壁相邻并与之接壤。以下权利要求中的所有手段或步骤功能元件的对应结构、材料、动作和等效物旨在包括用于与具体要求保护的其他权利要求元件组合执行功能的任何结构、材料或动作。

本发明的各种实施例的描述是出于说明的目的而给出的,但并不旨在穷尽或限制于所公开的实施例。在不脱离所描述的实施例的范围和精神的情况下,许多修改和变化对于本领域普通技术人员来说是显而易见的。本文使用的术语被选择为最好地解释实施例的原理、对市场上发现的技术的实际应用或技术改进,或者使本领域普通技术人员能够理解这里公开的实施例。