一种双环路亚采样锁相环结构

文献发布时间:2024-04-18 19:48:15

技术领域

本发明属于通信技术领域,具体涉及一种双环路亚采样锁相环结构。

背景技术

锁相环电路作为时钟产生电路,是集成电路中最重要的模块之一。随着技术的发展,被广泛应用于电子通信、测量、控制、信号处理等领域。它可以用于频率合成、时钟恢复、调制解调、相位控制等任务。具有高精度、高稳定性、快速响应和良好的抗干扰性能等优点。但是随着工艺水平的不断提高,锁相环的工作电压越来越低,压控振荡器的输出频率越来越高,导致了亚采样电荷泵输出电压范围变小,VCO的非线性问题越来越严重,降低了锁相环的稳定性,恶化了锁相环整体的相位噪声性能。

解决VCO非线性最具有代表性的是通过引入一个额外的VCO控制路径,将原始VCO控制电压重新集中到其振荡曲线的中间位置。这种方式在额外的VCO控制路径中包含着与环路滤波器串联的低增益积分器,从而形成一个额外的控制环路。但使用低增益积分器的方法依然存在着缺点,以这种方式构建的锁相环环路容易受到电荷泄露效应的影响,导致环路增益发生变化,造成锁相环环路功能的紊乱。

发明内容

为了解决现有技术中存在的上述问题,本发明提供了一种双环路亚采样锁相环结构。本发明要解决的技术问题通过以下技术方案实现:

一种双环路亚采样锁相环结构,包括:亚采样鉴相器SSPD、脉冲发生器PG、比例路径模块P-Path、积分路径模块I-Path、压控振荡器VCO、缓冲器BUFFER、鉴频鉴相器PFD、电荷泵CP和分频器Div;其中,

所述亚采样鉴相器SSPD用于将参考时钟信号Fref与所述缓冲器BUFFER输出的信号在过零点位置的相位误差转换为所述亚采样鉴相器SSPD输出的控制电压信号;

所述脉冲发生器PG用于根据所述参考时钟信号Fref输出控制所述比例路径模块P-Path中的亚采样电荷泵P-SSCP和所述积分路径模块I-Path中亚采样电荷泵I-SSCP开启与关闭的开关信号;

所述比例路径模块P-Path用于将所述控制电压信号转换成电流信号,并将所述电流信号和所述电荷泵CP输出的充放电电流经过处理后,输出调节所述压控振荡器VCO频率和相位的调节信号;

所述积分路径模块I-Path用于将所述控制电压信号转换成电流信号再处理后输出补偿所述压控振荡器VCO相位的补偿信号;

所述压控振荡器VCO用于根据所述调节信号和所述补偿信号输出振荡信号;

所述缓冲器BUFFER用于将所述振荡信号整形并输出给所述亚采样鉴相器SSPD和所述分频器Div;

所述鉴频鉴相器PFD用于利用D触发器判断所述参考时钟信号Fref与DIV信号上升沿的相位差,从而输出宽度不同的脉冲信号,控制所述电荷泵CP充放电开关的开启与关闭;

所述电荷泵CP用于根据所述鉴频鉴相器PFD输出的脉冲信号将电压转化为充放电电流,并输出给所述比例路径模块P-Path中的滤波模块;

所述分频器Div用于对所述缓冲器BUFFER输出的信号根据分频比输出分频后的DIV信号。

在本发明的一个实施例中,比例路径模块P-Path,包括:

所述亚采样电荷泵P-SSCP、纹波电容器C1和电阻器R

所述亚采样电荷泵P-SSCP的第一输入端接所述亚采样鉴相器SSPD的第一输出端,所述亚采样电荷泵P-SSCP的第二输入端接所述亚采样鉴相器SSPD的第二输出端,所述亚采样电荷泵P-SSCP的第三输入端接所述脉冲发生器PG的输出端,所述亚采样电荷泵P-SSCP的输出端与所述纹波电容器C1的一个极板相接于第一节点;

所述第一节点接所述电荷泵CP的输出端;

所述纹波电容器C1的另一个极板接地;

所述电阻器R

在本发明的一个实施例中,积分路径模块I-Path,包括:

所述亚采样电荷泵I-SSCP和环路电容器C

所述亚采样电荷泵I-SSCP的第一输入端接所述亚采样鉴相器SSPD的第一输出端,所述亚采样电荷泵I-SSCP的第二输入端接所述亚采样鉴相器SSPD的第二输出端,所述亚采样电荷泵I-SSCP的第三输入端接所述脉冲发生器PG的输出端,所述亚采样电荷泵I-SSCP的输出端与所述环路电容器C

所述环路电容器C

在本发明的一个实施例中,亚采样鉴相器SSPD、所述脉冲发生器PG、所述比例路径模块P-Path、所述积分路径模块I-Path、所述压控振荡器VCO和所述缓冲器BUFFER构成核心环路;其中,

所述亚采样鉴相器SSPD的第一输入端接入所述参考时钟信号Fref,所述亚采样鉴相器SSPD的第二输入端和第三输入端分别接所述缓冲器BUFFER的第一输出端和第二输出端;

所述脉冲发生器PG的输入端接入所述参考时钟信号Fref;

所述压控振荡器VCO的第一输入端接所述比例路径模块P-Path中的第一节点,所述压控振荡器VCO的第二输入端接所述积分路径模块I-Path的第二节点,所述压控振荡器VCO的第一输出端和第二输出端分别接所述缓冲器BUFFER的第一输入端和第二输入端;

所述压控振荡器VCO的第一输出端还接所述分频器Div的输入端。

在本发明的一个实施例中,

在本发明的一个实施例中,比例路径模块P-Path中的亚采样电荷泵P-SSCP或所述积分路径模块I-Path中亚采样电荷泵I-SSCP,包括:

MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

所述MOS管M

在本发明的一个实施例中,比例路径模块P-Path中的亚采样电荷泵P-SSCP或所述积分路径模块I-Path中亚采样电荷泵I-SSCP的增益由所述MOS管M

在本发明的一个实施例中,MOS管M

在本发明的一个实施例中,比例路径模块P-Path的工作方式包括:

所述比例路径模块P-Path将所述控制电压信号转换成电流信号并放大,再通过所述纹波电容器C1处理输出所述调节信号,影响所述压控振荡器VCO的控制电压进而实现对所述压控振荡器VCO频率和相位的调节。

在本发明的一个实施例中,比例路径模块P-Path的工作方式还包括:

当双环路亚采样锁相环实现锁定后,所述比例路径模块P-Path开始围绕所述偏置电压V

在本发明的一个实施例中,鉴频鉴相器PFD、电荷泵CP和分频器Div构成锁频环路;其中,

所述鉴频鉴相器PFD的第一输入端接入所述参考时钟信号Fref,所述鉴频鉴相器PFD的第二输入端接所述分频器Div的输出端,所述鉴频鉴相器PFD的第一输出端和第二输出端分别接所述电荷泵CP的第一输入端和第二输入端;

所述电荷泵CP的输出端接所述比例路径模块P-Path中的第一节点;

所述分频器Div的输入端接所述缓冲器BUFFER的第一输出端。

本发明的有益效果:

本发明实施例所提供的方案中,采用了比例路径模块P-Path使得压控振荡器VCO的非线性敏感度显著降低,也使得电荷泵CP所需要的线性电压范围更小,比例路径负责相位跟踪,具有高线性度和低噪声;还采用了积分路径模块I-Path减小了电荷泄露效应对锁相环的影响,并且可以产生宽的控制电压调谐范围来覆盖期望的频率锁定范围,提高了锁相环的稳定性。比例路径可以快速响应外部扰动和变化,积分路径可以消除持续的干扰,从而实现更稳定的锁定状态。

附图说明

图1为传统的一种CPPLL电荷泵锁相环的结构示意图;

图2为传统的一种SSPLL亚采样锁相环的结构示意图;

图3为传统的一种带VCO控制路径的亚采样锁相环的结构示意图;

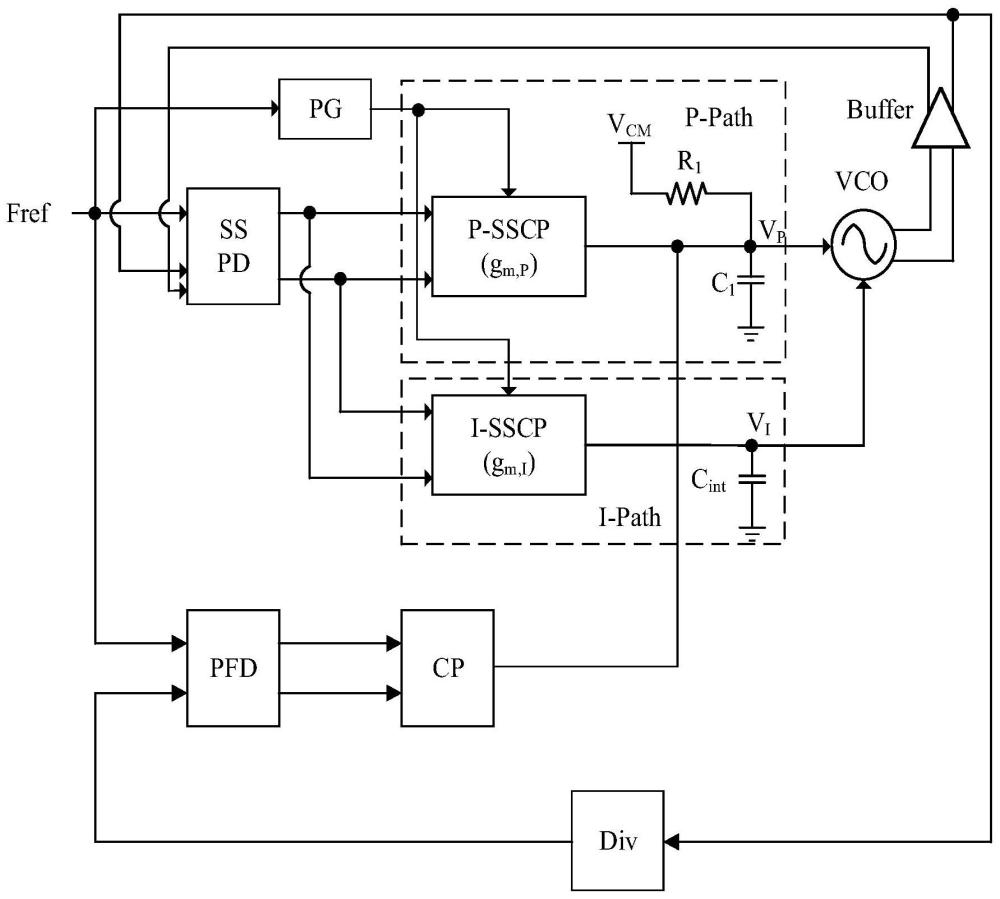

图4为本发明实施例所提供的一种双路径亚采样锁相环结构的示意图;

图5为本发明实施例所提供的一种亚采样电荷泵的结构示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

为了便于理解本发明实施例,下面首先对相关的现有技术进行介绍。

锁相环电路作为时钟产生电路,是集成电路中最重要的模块之一。随着技术的发展,被广泛应用于电子通信、测量、控制、信号处理等领域。它可以用于频率合成、时钟恢复、调制解调、相位控制等任务。具有高精度、高稳定性、快速响应和良好的抗干扰性能等优点。

锁相环按电路结构可以分为两类:CPPLL和SSPLL。CPPLL通常需要一个低频参考时钟作为输入,图1为传统的一种CPPLL电荷泵锁相环的结构示意图,包括:鉴频鉴相器(PFD,Phase-Frequency Detector)、电荷泵(CP,Charge Pump)、环路滤波器(LF,Loop Filter)、压控振荡器(VCO,Voltage Controlled Oscillator)和分频器;通过PFD比较输入信号和分频后信号的频率及相位,输出脉冲信号控制电荷泵对滤波器进行充放电,调节压控振荡器的输出频率,直到输出信号能够锁定到输入参考信号的倍频上。

SSPLL与CPPLL的主要区别在于SSPLL由核心环路Core Loop和锁频环路FLL组成,SSPLL的结构示意图如图2所示。

亚采样锁相环刚开始工作时,核心环路与锁频环路同时开始工作。对于核心环路的SSPD,是利用低频的参考时钟信号Fref对高频的VCO输出信号进行采样,将参考信号Fref的上升沿位置与VCO输出信号直流点位置的相位差转换为SSPD的输出信号,亚采样电荷泵再将电压转化为充放电电流,脉冲发生器用来控制SSCP的开启和关闭时间。

对于锁频环路的PFD,是利用D触发器判断Fref与DIV信号上升沿的相位差,从而产生宽度不同的脉冲信号,控制锁频环中电荷泵充放电开关的开启与关闭,从而产生充放电电流。

核心环路中的亚采样电荷泵SSCP和锁频环路中的电荷泵CP输出的电流共同注入低通滤波器中,低通滤波器输出一个电压来调整压控振荡器的输出信号频率。当压控振荡器输出频率逐渐提高,分频器输出信号DIV与参考信号Fref频率接近或者相等,相位差位于锁频环死区范围之外时,锁频环路累计相位,当信号Fref和DIV相位差逐步缩小到死区范围之内,锁频环路PFD的输出信号恒为零,电荷泵CP输出电流为0,锁频环停止工作。核心环路继续进行相位积累,直到参考信号Fref的边沿与VCO输出信号直流点位置对齐,此时亚采样电荷泵充放电维持稳定,压控振荡器电压维持恒定,亚采样锁相环系统处于锁定状态。与传统CPPLL相比,锁定时环路中没有分频器的存在,因此,SSPLL中的SPPD与SSCP的噪声传递函数的分支中去除了N

现有技术中解决VCO非线性最具有代表性的是通过引入一个额外的VCO控制路径,将原始VCO控制电压重新集中到其振荡曲线的中间位置。如图3所示。

这种方式在额外的VCO控制路径中包含着与环路滤波器串联的低增益积分器,从而形成一个额外的控制环路。在额外的控制路径被加入后,压控振荡器的输入控制电压被强制锁定在其调谐范围的中心,与其具体的输出频率无关,以此保证锁相环环路的小信号增益对压控振荡器和电容器的非线性不敏感。此外,由于图中的主路径不再需要承担一个比较宽的频率调谐范围,因此可以适当减小该路径的VCO增益。并且为了保持环路带宽不发生变化,电荷泵电流应成比例地增大,以改善相位噪声性能。但是使用低增益积分器的方法依然存在着缺点,以这种方式构建的锁相环环路容易受到电荷泄露效应的影响,导致环路增益发生变化,造成锁相环环路功能的紊乱。

针对上述结构所存在的局限性,本发明实施例提出了一种双环路亚采样锁相环结构,如图4所示,包括:亚采样鉴相器SSPD、脉冲发生器PG、比例路径模块P-Path、积分路径模块I-Path、压控振荡器VCO、缓冲器BUFFER、鉴频鉴相器PFD、电荷泵CP和分频器Div;其中,

亚采样鉴相器SSPD用于将参考时钟信号Fref与缓冲器BUFFER输出的信号在过零点位置的相位误差转换为亚采样鉴相器SSPD输出的控制电压信号;

脉冲发生器PG用于根据参考时钟信号Fref输出控制比例路径模块P-Path中的亚采样电荷泵P-SSCP和积分路径模块I-Path中亚采样电荷泵I-SSCP开启与关闭的开关信号;

比例路径模块P-Path用于将控制电压信号转换成电流信号,并将电流信号和电荷泵CP输出的充放电电流经过处理后,输出调节压控振荡器VCO频率和相位的调节信号;

积分路径模块I-Path用于将控制电压信号转换成电流信号再处理后输出补偿压控振荡器VCO相位的补偿信号;

压控振荡器VCO用于根据调节信号和补偿信号输出振荡信号;

缓冲器BUFFER用于将振荡信号整形并输出给亚采样鉴相器SSPD和分频器Div;

鉴频鉴相器PFD用于利用D触发器判断参考时钟信号Fref与DIV信号上升沿的相位差,从而输出宽度不同的脉冲信号,控制电荷泵CP充放电开关的开启与关闭;

电荷泵CP用于根据鉴频鉴相器PFD输出的脉冲信号将电压转化为充放电电流,并输出给比例路径模块P-Path中的滤波模块;

分频器Div用于对缓冲器BUFFER输出的信号根据分频比输出分频后的DIV信号。

和传统亚采样锁相环核心环路相比,本发明实施例拥有两个亚采样电荷泵,并且将二阶低通滤波器拆开,分配到了两个亚采样电荷泵的输出端。比例路径模块P-Path(P路径)负责相位跟踪,具有高线性度和低噪声;积分路径模块I-Path(I路径)用于稳定电路,并且可以产生宽的控制电压调谐范围来覆盖期望的频率锁定范围。比例路径可以快速响应外部扰动和变化,积分路径可以消除持续的干扰,从而实现更稳定的锁定状态。

可选地,比例路径模块P-Path,包括:

亚采样电荷泵P-SSCP、纹波电容器C1和电阻器R

亚采样电荷泵P-SSCP的第一输入端接亚采样鉴相器SSPD的第一输出端,亚采样电荷泵P-SSCP的第二输入端接亚采样鉴相器SSPD的第二输出端,亚采样电荷泵P-SSCP的第三输入端接脉冲发生器PG的输出端,亚采样电荷泵P-SSCP的输出端与纹波电容器C1的一个极板相接于第一节点;

第一节点接电荷泵CP的输出端;

纹波电容器C1的另一个极板接地;

电阻器R

在比例路径模块P-Path中,相位检测器SSPD测量输入信号和参考信号之间的相位差,并输出一个与相位差成比例的信号,这个比例增益信号经过亚采样电荷泵P-SSCP放大之后直接影响振荡器的频率和相位,从而实现对相位的调节,所以需要一个大的增益来实现快速跟踪和调节相位的作用。

可选地,积分路径模块I-Path,包括:

亚采样电荷泵I-SSCP和环路电容器C

亚采样电荷泵I-SSCP的第一输入端接亚采样鉴相器SSPD的第一输出端,亚采样电荷泵I-SSCP的第二输入端接亚采样鉴相器SSPD的第二输出端,亚采样电荷泵I-SSCP的第三输入端接脉冲发生器PG的输出端,亚采样电荷泵I-SSCP的输出端与环路电容器C

环路电容器C

积分路径模块I-Path则是通过对相位差进行积分操作,将相位差随时间的变化量累积起来,不需要很大的增益也可以实现。这样在长时间的积分过程中,短期的相位差变化就会变得不明显,而长期的相位误差得到累计和补偿,有效减少了电荷泄露效应对锁相环的影响,所以它主要是对振荡器的相位起补偿作用,使系统达到稳定的锁定状态。

可选地,亚采样鉴相器SSPD、脉冲发生器PG、比例路径模块P-Path、积分路径模块I-Path、压控振荡器VCO和缓冲器BUFFER构成核心环路;其中,

亚采样鉴相器SSPD的第一输入端接入参考时钟信号Fref,亚采样鉴相器SSPD的第二输入端和第三输入端分别接缓冲器BUFFER的第一输出端和第二输出端;

脉冲发生器PG的输入端接入参考时钟信号Fref;

压控振荡器VCO的第一输入端接比例路径模块P-Path中的第一节点,压控振荡器VCO的第二输入端接积分路径模块I-Path的第二节点,压控振荡器VCO的第一输出端和第二输出端分别接缓冲器BUFFER的第一输入端和第二输入端;

压控振荡器VCO的第一输出端还接分频器Div的输入端。

在本发明实施例中,核心环路的动态稳定性由比例路径模块P-Path主导,积分路径控制电压移动时的非线性,并不会对电路的稳定性造成明显影响。

可选地,鉴频鉴相器PFD、电荷泵CP和分频器Div构成锁频环路;其中,

鉴频鉴相器PFD的第一输入端接入参考时钟信号Fref,鉴频鉴相器PFD的第二输入端接分频器Div的输出端,鉴频鉴相器PFD的第一输出端和第二输出端分别接电荷泵CP的第一输入端和第二输入端;

电荷泵CP的输出端接比例路径模块P-Path中的第一节点;

分频器Div的输入端接缓冲器BUFFER的第一输出端。

可选地,比例路径模块P-Path中的亚采样电荷泵P-SSCP或积分路径模块I-Path中亚采样电荷泵I-SSCP,如图5所示,包括:

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

MOS管M

可选地,比例路径模块P-Path中的亚采样电荷泵P-SSCP或积分路径模块I-Path中亚采样电荷泵I-SSCP的增益由MOS管M

可选地,MOS管M

MOS管M

比例路径模块P-Path和积分路径模块I-Path的亚采样电荷泵都采用了这种结构,二者的主要差别在于增益大小。电荷泵增益的决定因素是M2和M3管跨导gm的大小。但在先进工艺条件下,系统电压较低,而SSCP每一条支路都是三个MOSFET的堆叠,导致了电压余量不足,负责提供电流的M1管不可避免的工作在线性区,因此,其漏极电流对电压的变化十分敏感。再根据跨导公式:

式中,u

可以分析得出跨导g

可选地,比例路径模块P-Path的工作方式包括:

比例路径模块P-Path将控制电压信号转换成电流信号并放大,再通过纹波电容器C1处理输出调节信号,影响压控振荡器VCO的控制电压进而实现对压控振荡器VCO频率和相位的调节。

可选地,比例路径模块P-Path的工作方式还包括:

当双环路亚采样锁相环实现锁定后,比例路径模块P-Path开始围绕偏置电压V

比例路径模块P-Path负责相位跟踪,具有高线性度和低噪声;积分路径模块I-Path用于稳定电路,并且可以产生宽的控制电压调谐范围来覆盖期望的频率锁定范围。比例路径模块P-Path可以快速响应外部扰动和变化,积分路径模块I-Path可以消除持续的干扰,从而实现更稳定的锁定状态。

当锁相环实现锁定之后,比例路径就会围绕着其偏置电压值V

压控振荡器VCO的控制电压,是以V

调谐曲线是一个以Y轴为频率,X轴为电压的曲线,理想情况是一个一次函数,电压越高,频率越高,呈线性关系;新的频率越高,这个新点对应的电压就会越高;但是这个新的频率不能太高,太高的话,以V

由于比例路径的增益要比积分路径大很多,所以环路的动态稳定性由比例路径主导,这样积分路径控制电压移动时的非线性,并不会对电路的稳定性造成明显影响,而作为主导的比例路径,只工作在固定偏置电压V

本发明实施例所提供的方案中,采用了比例路径模块P-Path使得压控振荡器VCO的非线性敏感度显著降低,也使得电荷泵CP所需要的线性电压范围更小,比例路径负责相位跟踪,具有高线性度和低噪声;还采用了积分路径模块I-Path减小了电荷泄露效应对锁相环的影响,并且可以产生宽的控制电压调谐范围来覆盖期望的频率锁定范围,提高了锁相环的稳定性。比例路径可以快速响应外部扰动和变化,积分路径可以消除持续的干扰,从而实现更稳定的锁定状态。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

以上所述仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内所作的任何修改、等同替换、改进等,均包含在本发明的保护范围内。