一种用于OLT设备网口辐射抑制电路及设计方法

文献发布时间:2023-06-19 11:06:50

技术领域

本发明涉及电气与电子设备领域,尤其涉及一种用于OLT设备网口辐射抑制电路及设计方法。

背景技术

(Optical Line Terminal,OLT)光线路终端设备为金属外壳,在进行辐射测试时,OLT设备的网口通过网线与(Personal Computer,PC)个人计算机相连,该结构类似于屏蔽环境引出一根天线,容易将内部高频干扰发送到外部。OLT设备内部干扰源主要集中在为(Passive Optical Network,PON)无源光纤网络芯片和(CPU,Central Processing Unit)CPU中央处理器芯片供应的多组差分时钟,时钟作为一个固定频率的波形,根据傅里叶变换,能量较为集中,容易辐射超标。

目前,现有技术的做法为采用较好的屏蔽网线,让屏蔽效果尽可能好,尽可能保持良好的屏蔽环境,以及在网口线靠IC侧加4.7PF/8.2PF的小电容,滤除高频干扰。但在实际使用环境用户一般不会使用屏蔽网线,导致辐射测试过高。因此需解决不使用屏蔽网线时的网口辐射抑制问题,进而能通过辐射测试。

发明内容

为克服相关技术中存在的问题,本发明提供一种用于OLT设备网口辐射抑制电路及设计方法,从而解决不使用屏蔽网线时,网口辐射过高的缺陷。

根据本发明实施例的第一方面提供一种用于OLT设备网口辐射抑制电路,该电路包括:振荡电路、CPLD电路、分压电阻、C1电容、C2电容、网络变压器、BOB-smith电路;所述振荡电路用于输出单端时钟到所述CPLD电路;所述CPLD电路包括1个输入具体为第一CPLD输入;所述CPLD电路包括两个输出分别为第一CPLD输出和第二CPLD输出;所述第一CPLD输出和所述第二CPLD输出之间并联所述分压电阻;所述C1电容包括C1电容第一端和C1电容第二端;所述C2电容包括C2电容第一端和C2电容第二端;所述C1电容第一端与所述第一CPLD输出连接;所述C2电容第一端与所述第二CPLD输出连接;所述C1电容第二端、所述C2电容第二端与所述处理器的输入连接;所述处理器与至少一个所述网络变压器连接,所述网络变压器的输出连接所述BOB-smith电路。

在一个或多个实施例中,优选地,所述分压电阻采用阻值为5.1欧姆的定值电阻。

在一个或多个实施例中,优选地,所述CPLD电路输出的电平为3.3V的电压。

在一个或多个实施例中,优选地,所述网络变压器包括6个输入,包括网络变压器第一输入、网络变压器第二输入、网络变压器第三输入、网络变压器第四输入、网络变压器第五输入、网络变压器第六输入;

所述网络变压器包括6个输出,包括网络变压器第一输出、网络变压器第二输出、网络变压器第三输出、网络变压器第四输出、网络变压器第五输出、网络变压器第六输出;

所述网络变压器第一输入、所述网络变压器第三输入、所述网络变压器第四输入、所述网络变压器第六输入均与一个4.7pF的电容接地;

所述网络变压器第二输入和所述网络变压器第五输入连接电容C5,用于滤除所述处理器的共模干扰信号。

在一个或多个实施例中,优选地,所述BOB-smith电路包括电阻R1,所述电阻R1的阻值为50欧姆;

所述电阻R1与所述网络变压器第二输出、所述网络变压器第五输出连接。

在一个或多个实施例中,优选地,所述BOB-smith电路包括电流浪涌卸放电路,所述电流浪涌卸放电路包括1个双向防护二极管D1,所述双向防护二极管D1用于电流浪涌卸放;

所述电流浪涌卸放电路与所述网络变压器第二输出、所述网络变压器第五输出连接。

在一个或多个实施例中,优选地,所述BOB-smith电路包括电容C6,所述电容C6采用陶瓷电容,所述电容C6容值为1uF;

所述电容C6与所述电阻R1串联后接地;

所述电容C6与所述电阻R1串联后与所述电流浪涌卸放电路并联。

根据本发明实施例的第二方面提供一种用于OLT设备网口辐射抑制电路的设计方法,该设计方法包括:

利用逻辑代码编写将输入的单端时钟配置为至少一对输出差分时钟;

将所述输出差分时钟配置为原始所述输入的单端时钟的幅度的20%;

处理器根据所述输出差分时钟向至少一个网络变压器提供数据信号;

根据所述网络变压器内部结构将网络变压器抽头接电容接地,滤除所述处理器的共模干扰信号;

根据电容频率特性曲线,电容谐振频率取电容阻抗值最低时,根据第一计算公式滤除干扰信号;

设计BOB-Smith电路的电阻和电容参数,滤除干扰信号;

第一计算公式:

其中,ESR为陶瓷电容串联等效电阻,Tanδ为陶瓷电容损耗角正切值,f

在一个或多个实施例中,优选地,所述将所述输出差分时钟配置为原始所述输入的单端时钟的幅度的20%,具体包括:

在所述CPLD电路中对引脚功能进行设置,将输出电平类型选择为3.3V的电压信号,所述CPLD电路自动将对应引脚设置为差分的P引脚,并自动将N脚分配给与所述P引脚对应的差分引脚;

所述CPLD电路输出的差分信号近似为方波,其中,方波幅度为E,根据第二计算公式和第三计算公式获取方波的傅里叶级数展开;

根据处理器输入为CML电平,需要所述CPLD电路输出时钟和所述处理器之间加C1电容和C2电容进行AC耦合;

根据所述CPLD电路内部管脚结构,在PN间加一个电阻,与上拉限流电阻构成一个分压回路,对CPLD电路的输入电压进行分压,分压得到一个0.6V的输出电压;

根据所述第一公式分析,确定能量降低到原来的20%;

所述第二计算公式为:

其中,f(t)为方波函数,E为幅值大小,t为时间,T为周期;

所述第三计算公式为:

其中,g(t)为方波函数的傅里叶变换函数,E为幅值大小,t为时间,n为整数,ω

在一个或多个实施例中,优选地,所述设计BOB-Smith电路的电阻和电容参数,滤除干扰信号,具体包括:

选择干扰频率为谐振频率,根据谐振频率与陶瓷电容电容值、ESR、损耗角正切值关系获得干扰频率的电容作为抽头电容;

根据所述BOB-Smith电路功能需求,对每一路并联浪涌防护管,为浪涌泄放路径,使所述BOB-Smith电路的电容C6不承担防护作用;

在PCB制板时将差分阻抗控制为100欧姆,所述BOB-Smith电路每一路抽头电阻选择为差分阻抗的一半,设定为50欧姆;

选择所述BOB-Smith电路的电容C6电容值滤除干扰信号;

把所述网络变压器的所有抽头连接在一起,只需保留1路滤除干扰信号。

本发明的实施例提供的技术方案可以包括以下有益效果:

1、本发明通过该方案直接用一个逻辑芯片即可输出多路差分时钟信号,解决了传统由差分时钟buffer芯片提供是1颗差分时钟buffer仅可提供几路差分输出的问题。

2、本发明通过在逻辑输出差分时钟线之间接入电阻进行幅度调节,电路简单,可降低时钟辐射强度,同时可满足负载对于输入信号电平的要求。

3、本发明不大量增加元器件,不占用PCB空间,改动极小,且可使BOB-Smith电路电容选择不受限制,即适用用于信号线加电容滤除不掉辐射、不能使用屏蔽线的辐射整改的领域,也可用于对于金属包裹类设备,有网线或其他金属线引出壳体类设备,此外对于设备因为做浪涌测试而分开地的设备也能够起到辐射抑制的作用。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

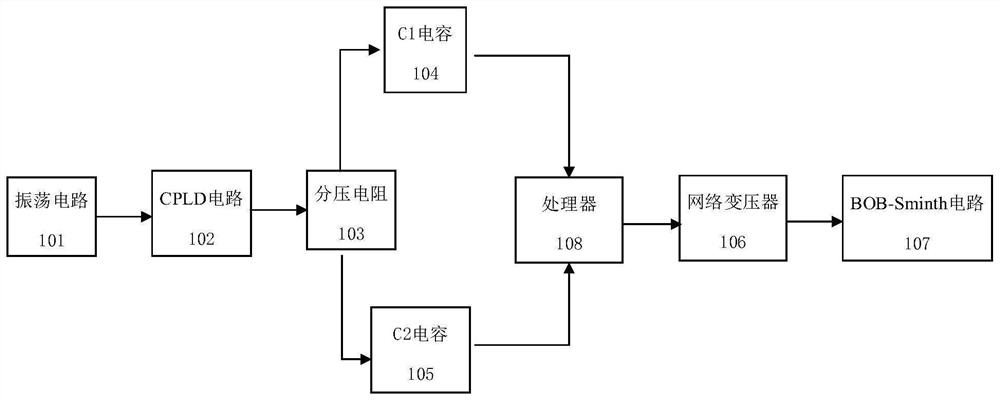

图1是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的结构图。

图2是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的CPLD电路输出示意图。

图3是本发明一个实施例的一种用于OLT设备网口辐射抑制电路中的步态采集显示装置中的CPLD电路的外部电气结构连接图。

图4是本发明一个实施例的一种用于OLT设备网口辐射抑制电路中的步态采集显示装置中的CPLD电路的内部电气结构图。

图5是本发明一个实施例的一种用于OLT设备网口辐射抑制电路中的网络变压器内部结构图。

图6是本发明一个实施例的一种用于OLT设备网口辐射抑制电路中的网络变压器的外部结构图。

图7是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的设计方法的流程图。

图8是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的设计方法中的所述将所述输出差分时钟配置为原始所述输入的单端时钟的幅度的20%的流程图。

图9是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的设计方法中的所述设计BOB-Smith电路的电阻和电容参数,滤除干扰信号流程图。

图10是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的设计方法中的电容频率特性曲线图。

图11是本发明一个实施例的用于OLT设备网口辐射抑制电路实施前效果图。

图12是本发明一个实施例的用于OLT设备网口辐射抑制电路实施后效果图。

具体实施方式

为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。

在本发明的说明书和权利要求书及上述附图中的描述的一些流程中,包含了按照特定顺序出现的多个操作,但是应该清楚了解,这些操作可以不按照其在本文中出现的顺序来执行或并行执行,操作的序号如101、102等,仅仅是用于区分开各个不同的操作,序号本身不代表任何的执行顺序。另外,这些流程可以包括更多或更少的操作,并且这些操作可以按顺序执行或并行执行。需要说明的是,本文中的“第一”、“第二”等描述,是用于区分不同的消息、设备、模块等,不代表先后顺序,也不限定“第一”和“第二”是不同的类型。

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

(Optical Line Terminal,OLT)光线路终端设备为金属外壳,在进行辐射测试时,OLT设备的网口通过网线与(Personal Computer,PC)个人计算机相连,该结构类似于屏蔽环境引出一根天线,容易将内部高频干扰发送到外部。OLT设备内部干扰源主要集中在为(Passive Optical Network,PON)无源光纤网络芯片和(CPU,Central Processing Unit)CPU中央处理器芯片供应的多组差分时钟,时钟作为一个固定频率的波形,根据傅里叶变换,能量较为集中,容易辐射超标。

本发明技术之前,现有技术的做法为采用较好的屏蔽网线,让屏蔽效果尽可能好,尽可能保持良好的屏蔽环境,以及在网口线靠近(Integrated CircuitChip,IC)芯片的一侧加4.7PF/8.2PF的小电容,滤除高频干扰。但在实际使用环境用户一般不会使用屏蔽网线,导致辐射测试过高。此外,也有技术在网络变压器网口侧的抽头通过75欧姆的电阻串联小电容到地,但电阻上有一定的小电流通过,也会产生噪声向外辐射,导致OLT设备辐射测试超标,无法通过。因此,需解决不使用屏蔽网线时的网口辐射抑制问题,进而能通过辐射测试。

本发明将考虑构建一种用于OLT设备网口辐射抑制电路及设计方法,通过对OLT设备上CPLD产生差分时钟进行降幅以及网口变压器进行抽头电容选取和BOB-Smith电路的选取来消除干扰,改善OLT设备网口辐射。

图1是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的结构图。

如图1所示,在一个或多个实施例中,优选地,所述用于OLT设备网口辐射抑制电路包括:振荡电路101、CPLD电路102、分压电阻103、C1电容104、C2电容105、网络变压器106、BOB-smith电路107、处理器108;所述振荡电路101用于输出单端时钟到所述CPLD电路102;所述CPLD电路102包括1个输入具体为第一CPLD输入;所述CPLD电路102包括两个输出分别为第一CPLD输出和第二CPLD输出;所述第一CPLD输出和所述第二CPLD输出之间并联所述分压电阻103;所述C1电容104包括C1电容第一端和C1电容第二端;所述C2电容105包括C2电容第一端和C2电容第二端;所述C1电容第一端与所述第一CPLD输出连接;所述C2电容第一端与所述第二CPLD输出连接;所述C1电容第二端、所述C2电容第二端与所述处理器108的输入连接;所述处理器108与至少一个所述网络变压器106连接,所述网络变压器106的输出连接所述BOB-smith电路107。

具体的,(Complex Programmable Logic Device,CPLD)是一种较PLD为复杂的逻辑元件,CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。

其工作原理是:所述振荡电路首先运行获取一个单一的时钟信号,经由CPLD电路分为多个时钟信号,进而通过分压电阻进行降压,并利用C1电容和C2电容进行交流耦合,最终经由BOB-smith电路完成浪涌卸放等任务。

在本发明实施例中,提供了一种用于OLT设备网口辐射抑制的电路架构,在该架构中所述分压电阻将CPLD电路102的输出电压由3.3V的水平拉低,但同时还能保证输出电压水平足够支撑后续的网络变压器工作。

图2是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的CPLD电路102输出示意图。在本发明实施例中,在逻辑代码编写里,将输入的单端时钟配置为输出差分时钟,则可以输出一对差分时钟,也可以输出多对差分时钟。进而在逻辑芯片的引脚设置里,将输出电平类型选择为3.3V的电平,则所述CPLD电路会自动将这个管脚设置为差分的P脚,并自动将N脚分配给这个差分对对应管脚,而所述CPLD电路输出的差分信号近似为方波,其中的E表示方波幅度。

图3是本发明一个实施例的一种用于OLT设备网口辐射抑制电路中的步态采集显示装置中的CPLD电路102的外部电气结构连接图。图4是本发明一个实施例的一种用于OLT设备网口辐射抑制电路中的步态采集显示装置中的CPLD电路102的内部电气结构图。如图3所示,在一个或多个实施例中,优选地,所述分压电阻103采用阻值为5.1欧姆的定值电阻。如图4所示,在一个或多个实施例中,优选地,所述CPLD电路102输出的电平为3.3V的电压。

在本发明实施例中,由于在内部的上拉电阻的电平是3.3V,当在本回路中采用了阻值为5.1欧姆的电阻进行分压时,则在PN间加上了所述分压电阻,与上拉限流电阻构成一个分压回路,对3.3V的VCC进行分压,得到一个0.6V电压,最终利用该电压的方波幅度将会为原来的1/5,最终产生的能量为原始的20%。

图5是本发明一个实施例的一种用于OLT设备网口辐射抑制电路中的网络变压器内部结构图。图6是本发明一个实施例的一种用于OLT设备网口辐射抑制电路中的网络变压器外部结构的示意图。

在一个或多个实施例中,优选地,所述网络变压器106包括6个输入,包括网络变压器第一输入501、网络变压器第二输入502、网络变压器第三输入503、网络变压器第四输入504、网络变压器第五输入505、网络变压器第六输入506;

所述网络变压器106包括6个输出,包括网络变压器第一输出507、网络变压器第二输出508、网络变压器第三输出509、网络变压器第四输出510、网络变压器第五输出511、网络变压器第六输出512;

所述网络变压器第一输入501、所述网络变压器第三输入503、所述网络变压器第四输入504、所述网络变压器第六输入506均与一个4.7pF的电容接地;

所述网络变压器第二输入502和所述网络变压器第五输入505连接电容C5,用于滤除所述处理器108的共模干扰信号。

在一个或多个实施例中,优选地,所述BOB-smith电路107包括电阻R1,所述电阻R1的阻值为50欧姆;

所述电阻R1与所述网络变压器第二输出508、所述网络变压器第五输出511连接。

在一个或多个实施例中,优选地,所述BOB-smith电路107包括电流浪涌卸放电路,所述电流浪涌卸放电路包括1个双向防护二极管D1,所述双向防护二极管D1用于电流浪涌卸放。

所述电流浪涌卸放电路与所述网络变压器第二输出508、所述网络变压器第五输出511连接。

所述BOB-smith电路包括电容C6,所述电容C6采用陶瓷电容,所述电容C6容值为1uF;

所述电容C6与所述电阻R1串联后接地;

所述电容C6与所述电阻R1串联后与所述电流浪涌卸放电路并联。

具体的,在所述BOB-Smith电路中,因为抽头有选择防雷管保护设计,网口防雷主要依靠防雷管进行,抽头的1nF高压陶瓷电容就不需要很高耐压值,可以选取大容值,低耐压的陶瓷电容,由常规的1nF改为1uF,保证网口测抽头的工频干扰很低。因此,本实施例只需一个1uF即解决问题,在单颗电容不能解决问题或者对成本不敏感时,可以使用级联法,采用1uF和100nF级联的方式,降低网线相对于地的低频分量,减小辐射传播的距离。因此,作为辅助,在靠近CPLD侧的信号线增加了4.7pF的对地电容。

在本发明实施例中,所述网络变压器的共模干扰信号可通过该侧抽头滤除,根据BOB-Smith电路功能,所述电容C6在发生浪涌冲击时会做为防护电容使用,需用高压电容以致该电容选取限制大可选范围小,但是本发明在BOB-Smith电路上每一路并联浪涌防护路径,双向防护二极管D1做为浪涌泄放路径,由于BOB-Smith电路电容C6不承担防护作用,只考虑EMC功能,具有更大选取范围。此外,由于根据制版的要求差分阻抗需要为100欧姆,BOB-Smith电路每一路抽头电阻选择为差分阻抗的一半,R1为50欧姆,保持阻抗连续性,在干扰信号滤除时不会产生信号反射。

图7是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的设计方法的流程图。

如图7所示,在一个或多个实施例中,优选地,本发明实施例的第二方面提供一种用于OLT设备网口辐射抑制电路的设计方法,该设计方法包括:

S701、利用逻辑代码编写将输入的单端时钟配置为至少一对输出差分时钟;

S702、将所述输出差分时钟配置为原始所述输入的单端时钟的幅度的20%;

S703、处理器根据所述输出差分时钟向至少一个网络变压器提供数据信号;

S704、根据所述网络变压器内部结构将网络变压器抽头接电容接地,滤除所述处理器的共模干扰信号;

S705、根据电容频率特性曲线,电容谐振频率取电容阻抗值最低时,根据第一计算公式滤除干扰信号;

S706、设计BOB-Smith电路的电阻和电容参数,滤除干扰信号;

第一计算公式:

其中,ESR为陶瓷电容串联等效电阻,Tanδ为陶瓷电容损耗角正切值,f

在本发明实施例中,首先根据需求利用逻辑代码在CPLD内设计,进而获得多路差分时钟,在此种情况下即可实现直接用一个逻辑芯片即可输出多路差分时钟信号,解决了传统由差分时钟buffer芯片提供是1颗差分时钟buffer仅可提供几路差分输出的问题;在此基础上,设计辐射抑制电路,并通过参数选型滤除干扰信号。

图8是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的设计方法中的所述将所述输出差分时钟配置为原始所述输入的单端时钟的幅度的20%的流程图。

如图8所示,在一个或多个实施例中,优选地,所述将所述输出差分时钟配置为原始所述输入的单端时钟的幅度的20%,具体包括:

S801、在所述CPLD电路中对引脚功能进行设置,将输出电平类型选择为3.3V的电压信号,所述CPLD电路自动将对应引脚设置为差分的P引脚,并自动将N脚分配给与所述P引脚对应的差分引脚;

S802、所述CPLD电路输出的差分信号近似为方波,其中,方波幅度为E,根据第二计算公式和第三计算公式获取方波的傅里叶级数展开;

S803、根据处理器输入为CML电平,需要所述CPLD电路输出时钟和所述处理器之间加C1电容104和C2电容105进行AC耦合;

具体的,CML即Current Mode Logic,具体为电流模式逻辑,CML电路主要靠电流驱动,是一种功耗较低的信号传输方式;

S804、根据所述CPLD电路内部管脚结构,在PN间加一个电阻,与上拉限流电阻构成一个分压回路,对CPLD电路的输入电压进行分压,分压得到一个0.6V的输出电压;

S805、根据所述第一公式分析,确定能量降低到原来的20%;

所述第二计算公式为:

其中,f(t)为方波函数,E为幅值大小,t为时间,T为周期;

所述第三计算公式为:

其中,g(t)为方波函数的傅里叶变换函数,E为幅值大小,t为时间,n为整数,ω

在本发明实施例中,根据本方案发明,首先的任务是要减小时钟源头辐射强度,因此在满足芯片要求的前提下将差分时钟幅度尽可能降低,在CPLD端差分时钟的PN脚之间并联一个5.1R电阻,将信号幅度拉低到0.6V左右。减小源头辐射强度为原始的20%。

图9是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的设计方法中的所述设计BOB-Smith电路的电阻和电容参数,滤除干扰信号流程图。

如图9所示,在一个或多个实施例中,优选地,所述设计BOB-Smith电路的电阻和电容参数,滤除干扰信号,具体包括:

S901、选择干扰频率为谐振频率,根据谐振频率与陶瓷电容电容值、ESR、损耗角正切值关系获得干扰频率的电容作为抽头电容;

S902、根据所述BOB-Smith电路功能需求,对每一路并联浪涌防护管,为浪涌泄放路径,使所述BOB-Smith电路的电容C6不承担防护作用;

S903、在PCB制板时将差分阻抗控制为100欧姆,所述BOB-Smith电路每一路抽头电阻选择为差分阻抗的一半,设定为50欧姆;

S904、选择所述BOB-Smith电路的电容C6电容值滤除干扰信号;

S905、把所述网络变压器的所有抽头连接在一起,只需保留1路滤除干扰信号。

在本发明实施例中,通过计算BOB-Smith的电阻、电容,主要实现两方面目的,第一方面是利用C6滤除干扰信号的同时不限制其容值选取范围,第二方面,将抽头电阻选择为50欧姆,保持阻抗连续性,进而实现在干扰信号滤除时,不产生信号的反射,进而产额外辐射。

图10是本发明一个实施例的一种用于OLT设备网口辐射抑制电路的设计方法中的电容频率特性曲线图。如图10所示,在本发明实施例中,选择谐振频率最接近干扰频率滤除效果最好,根据谐振频率与陶瓷电容电容值、ESR、损耗角正切值关系,利用所述第一计算公式,其中ESR和损耗角正切值电容厂家提供,可以得出谐振频率最接近干扰频率的电容作为抽头电容。

图11是本发明一个实施例的用于OLT设备网口辐射抑制电路实施前效果图。图12是本发明一个实施例的用于OLT设备网口辐射抑制电路实施后效果图。如图11和12所示为整改前和整改后的3m辐射测试结果,从结果对比:175MHZ、225MHZ、250MHZ、475MHZ、525MHZ、625MHZ等25MHZ倍频的超标点在整改后至少有4个dB的余量。

本发明的实施例提供的技术方案可以包括以下有益效果:

1、本发明通过该方案直接用一个逻辑芯片即可输出多路差分时钟信号,解决了传统由差分时钟buffer芯片提供是1颗差分时钟buffer仅可提供几路差分输出的问题。

2、本发明通过在逻辑输出差分时钟线之间接入电阻进行幅度调节,电路简单,可降低时钟辐射强度,同时可满足负载对于输入信号电平的要求。

3、本发明不大量增加元器件,不占用PCB空间,改动极小,且可使BOB-Smith电路电容选择不受限制,即适用用于信号线加电容滤除不掉辐射、不能使用屏蔽线的辐射整改的领域,也可用于对于金属包裹类设备,有网线或其他金属线引出壳体类设备,此外对于设备因为做浪涌测试而分开地的设备也能够起到辐射抑制的作用。

本领域内的技术人员应明白,本发明的实施例可提供为方法、系统、或计算机程序产品。因此,本发明可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本发明可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器和光学存储器等)上实施的计算机程序产品的形式。

本发明是参照根据本发明实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

- 一种用于OLT设备网口辐射抑制电路及设计方法

- 一种用于OLT设备网口辐射抑制电路及设计方法