一种高速ADC并串转换电路

文献发布时间:2023-06-19 11:06:50

技术领域

本发明涉及并串转换电路技术领域,尤其是一种基于同步时序逻辑电路的高速ADC并串转换电路。

背景技术

计算机技术、通信技术和微电子技术的高速发展,大大促进了ADC技术的发展。ADC作为模拟量与数据量接口的关键部件,广泛应用于各个领域,在信息技术中起着重要作用。ADC同计算机一样,经历了低速到高速的发展过程。ADC的低速(转换时间大于300us)结构有积分型、斜坡型、跟踪型;ADC中速(转换时间在1-300us)结构有逐次逼近型;A DC的高速(转换时间小于1us)结构有闪烁型、分区式以及高分辨率结构的Σ-Δ型。不同结构的ADC满足实际应用中广泛性和多样性的需求,其中高速ADC已经成为决定现代化电子设备性能(诸如雷达、通信、电子对抗、航天航空、导弹、测控、地展、医疗、仪器仪表、图像、高性能控制器、数字通信系统等)的重要环节。

由于单核ADC的采样数据率受限,进而发展出时间交替采样技术,也叫并行多通道采样技术,该技术是目前实现高频率采样的数据采集系统的最佳途径。为了便于采集数据的后续处理,需要将并行输入的数据转换为串行的输出数据,即并串转换。现有并串转换电路的实现方式中,当输入n路并行数据时,需消耗n个触发器和n个开关,当ADC为m位时,则需消耗n*m个触发器和n*m个开关,存在占用面积大,制作成本高的缺点。

发明内容

针对现有并串转换电路的实现方式的不足之处,本发明提出一种基于同步时序逻辑电路的高速ADC并串转换电路。

一种高速ADC并串转换电路,包括时钟复位管理单元、n个时序控制单元和数据选择输出单元,时钟复位管理单元为每个时序控制单元提供时钟信号和复位信号,每个时序控制单元用于各自通道内i路数据和q路数据的采样、校正和交织输出,数据选择输出单元用于按各通道数据的输出时序交织输出各通道的采样数据;

时钟复位管理单元为每个时序控制单元提供通道工作时钟、i路工作时钟、q路工作时钟,时序控制单元i路m位数据在i路工作时钟域下采样和校正,q路m位数据在q路工作时钟域下采样和校正,单通道并串转换通过单bit计数器计数,由通道工作时钟采样,交织输出对应通道的采样数据;

每个时序控制单元的通道工作时钟相差360°/n,其i路工作时钟由其通道工作时钟2分频产生,其q路工作时钟分别由其通道工作时钟2分频并反相产生。

进一步的,时序控制单元包括工作模式控制模块和校正输出模块,工作模式控制模块用于切换ADC工作模式,校正输出模块根据权重校正i路和q路输入的m位数据,并按照时钟相位关系,交替输出校正完毕后的i路和q路m位数据。

进一步的,数据选择输出单元交织输出各通道的采样数据的同时,输出随路时钟。

进一步的,时钟复位管理单元在ADC为工作状态时产生时,在ADC为睡眠和低功耗状态时关断时钟。

本发明公开的基于同步时序逻辑电路的高速ADC并串转换电路,可以实现多路并行m位数据到单路m位数据的并串转换,完成低采样数据率到高采样数据率的转换,相比于现有并串转换电路的实现方式,有效降低电路面积和功耗;同时,可根据ADC工作状态产生或关断时钟信号,降低电路功耗。

附图说明

图1为高速ADC并串转换电路结构示意图;

图2为时钟复位管理单元CRMU时钟框图;

图3为CRMU时钟相位关系图;

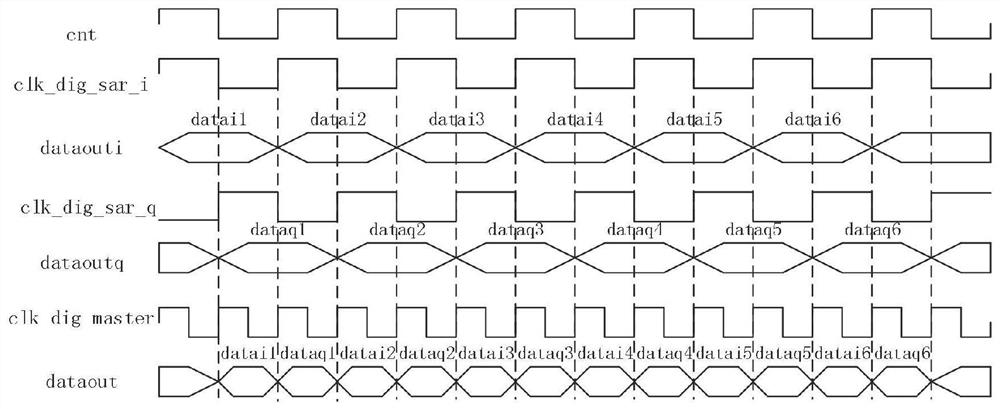

图4为单通道输出数据时序图;

图5为数据选择输出单元MUX数据输出时序图。

具体实施方式

下面结合附图和具体实施方式对本发明作进一步详细的说明。本发明的实施例是为了示例和描述起见而给出的,而并不是无遗漏的或者将本发明限于所公开的形式。很多修改和变化对于本领域的普通技术人员而言是显而易见的。选择和描述实施例是为了更好说明本发明的原理和实际应用,并且使本领域的普通技术人员能够理解本发明从而设计适于特定用途的带有各种修改的各种实施例。

实施例1

一种高速ADC并串转换电路,包括时钟复位管理单元、n个时序控制单元和数据选择输出单元,本实施例以n=4为例,具体结构参照图1。

时钟复位管理单元CRMU为每个时序控制单元提供时钟信号和复位信号,其时钟框图如图2所示,主时钟Clk经过4分频和移相产生对应四个时序控制单元的通道工作时钟clk_dig_master_ch1、clk_dig_master_ch2、clk_dig_master_ch3、clk_dig_master_ch4。四个通道工作时钟分别经过2分频产生clk_dig_sar_i_ch1、clk_dig_sar_i_ch2、clk_dig_sar_i_ch3、clk_dig_sar_i_ch4;经过2分频和反相产生clk_dig_sar_q_ch1、clk_dig_sar_q_ch2、clk_dig_sar_q_ch3、clk_dig_sar_q_ch4。

每个时序控制单元的通道工作时钟相差360°/n,其i路工作时钟由其通道工作时钟2分频产生,其q路工作时钟分别由其通道工作时钟2分频并反相产生。CRMU时钟相位关系如图3所示。经过主时钟Clk分频和移相后的四个通道工作时钟时钟相位依次相差90°,四个通道工作时钟分频后对应的i路工作时钟和q路工作时钟相位相差180°。

时序控制单元包括工作模式控制模块和校正输出模块。工作模式控制模块用于切换ADC工作模式。校正输出模块根据权重校正i路和q路输入的m位数据,并按照时钟相位关系,交替输出校正完毕后的i路和q路m位数据,具体为,时钟复位管理单元为每个时序控制单元提供通道工作时钟clk_dig_master、i路工作时钟clk_dig_sar_i、q路工作时钟clk_dig_sar_q。时序控制单元i路m位数据在i路工作时钟域下采样和校正,q路m位数据在q路工作时钟域下采样和校正,单通道并串转换通过单bit计数器计数,由通道工作时钟clk_dig_master采样,交织输出对应通道的采样数据,参照图4。

数据选择输出单元用于按各通道数据的输出时序交织输出各通道的采样数据,具体为数据选择输出单元工作在主时钟Clk时钟域下,通过2bit计数器计数,交织输出4通道的采样数据,参照图5,至此,完成8路并行m位数据到1路m位数据的转换。

数据选择输出单元交织输出各通道的采样数据的同时,输出随路时钟clkout,便于后续跨时钟域处理。

为减低功耗,时钟复位管理单元在ADC为工作状态时产生时,在ADC为睡眠和低功耗状态时关断时钟。

显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域及相关领域的普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都应属于本发明保护的范围。

- 一种高速ADC并串转换电路

- 一种基于时钟调相的并串转换电路