用于在衬底上形成钼薄膜的方法

文献发布时间:2023-06-19 11:11:32

技术领域

本发明涉及含钼材料的气相沉积。确切来说,本发明涉及二氯二氧化钼(MoO

背景技术

钼由于其极高熔点、较低热膨胀系数、较低电阻率和较高热导率的特征而逐渐用于制造半导体装置中,包括用于扩散阻挡层、电极、光罩、大功率电子衬底、低电阻栅极和互连件中。

此类效用已激励人们努力实现用于此类应用的钼薄膜的沉积,其表征为沉积薄膜的高保形性和高沉积速率以适应有效的大批量制造操作。此转而为研发适用于气相沉积操作的改进的钼源试剂以及利用此类试剂的改进非工艺参数做出努力。

五氯化钼最常用作含钼材料的化学气相沉积的钼源。然而,仍需要实现以更高沉积速率来沉积含钼材料以适应有效的大批量制造操作。

发明内容

本发明涉及含钼材料的气相沉积,且更确切来说,涉及二氯二氧化钼(MoO

在一个方面中,本发明提供一种在衬底上形成含钼材料的工艺,其包含在气相沉积条件下使衬底与二氯二氧化钼(MoO

在各种实施例中,本发明涉及一种在衬底上形成含钼材料的方法,其包含通过气相沉积工艺利用二氯二氧化钼(MoO

有利地,在本发明的工艺中,可在小于约400℃的温度下沉积钼,其使得所述工艺能够用于制造逻辑装置。此类逻辑装置由于在钼沉积之前与现有装置结构的兼容性而具有挑战。

此外,较高钼沉积速率降低工具时间和加工成本。我们还发现,由于暴露于钼前体(MoO

因此形成的薄膜具有小于1%氧,或小于0.1%氧,由大于99%钼组成,且拥有大于95%、大于99%或接近100%的保形性,如例如通过截面透射电子显微术成像技术所测定,以及在

本发明的其它方面、特征和实施例将从随后的说明书和所附权利要求书更加充分明显。

附图说明

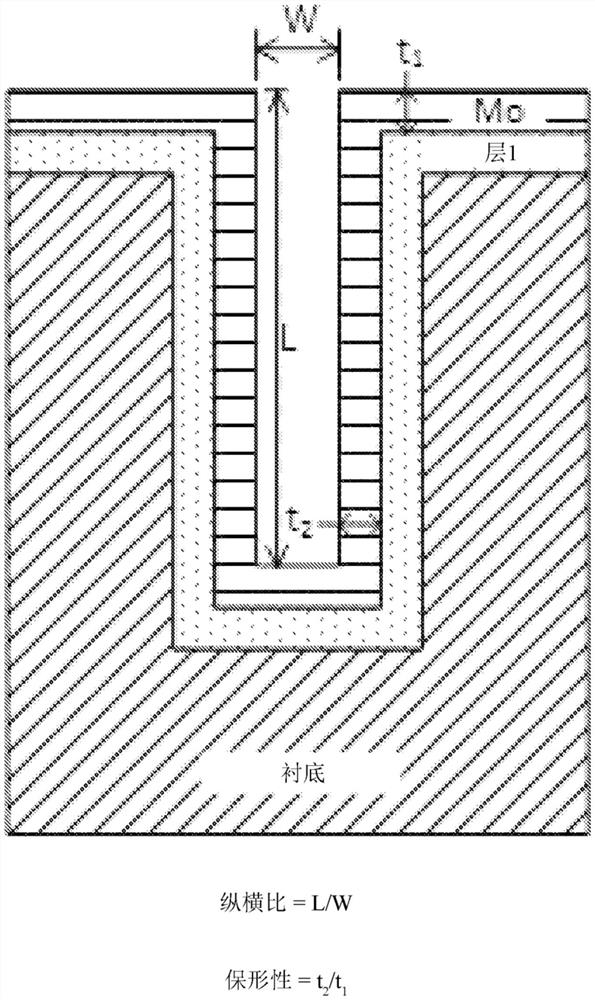

图1为展示通过所公开的方法形成于微电子装置上的钼(Mo)薄膜的纵横比和保形性的薄膜图示。

图2为各种钼前体的薄膜电阻率相比于薄膜厚度的比较。

图3为在

图4描绘随用于脉冲CVD Mo沉积的衬底温度而变化的Mo厚度和电阻率。

图5为MoO

图6为以μΩ·cm为单位的Mo电阻率相比于衬底温度的曲线图。

图7为脉冲化学气相沉积工艺的图示。压力由自动节流阀控制。安瓿向腔室脉冲“启用(on)”1秒,随后在循环的剩余59秒期间加压。当安瓿向所述腔室脉冲开启时,腔室中的压力剧增到比压力设定点的更高的压力值。

图8为说明使用H

具体实施方式

本发明涉及气相沉积钼,且确切来说涉及二氯二氧化钼(MoO

在本发明的各种实施例中,使用二氯二氧化钼(MoO

图2描绘展示三种不同Mo前体的薄膜电阻率相比于薄膜厚度的比较的曲线图。在曲线图中,将安瓿加热到70℃的温度且将薄膜沉积到具有TiN层的硅衬底涂层上。

在本发明的某些实施例中,可使用脉冲气相沉积条件来沉积前体。已发现,此可改进沉积的步阶式覆盖率。取决于衬底结构和反应器设计,脉冲沉积的适当“脉冲”和“净化”时间可各自独立地在1到120秒、1到60秒或1到20秒范围内。

在各种实施例中,选择蒸气条件以使得沉积的含钼材料的电阻率小于100μΩ·cm、小于50μΩ·cm、至多20μΩ·cm、任选地至多15-20μΩ·cm,且在其它实施例中,低至8μΩ·cm。

可在350℃到750℃的范围内,或在300℃到600℃的范围内,或在300℃到575℃的范围内的(衬底)温度下沉积含钼材料。

在各种实施例中,除任选的存在例如氢的还原剂以外,气相沉积条件包含惰性气氛。在某些实施例中,可在大体上不存在其它金属蒸气的情况下沉积二氯二氧化钼(MoO

本发明的工艺可包含使二氯二氧化钼(MoO

本发明的额外优点为较高钼沉积速率降低工具时间和加工成本。因而,所述工艺由于暴露于钼前体(MoO

在本发明的一个方面中,图3展示随衬底温度而变化的沉积的MoOCl

在本发明的其它实施例中,用于所描述工艺中的衬底可具有任何合适的类型,且可例如包含半导体装置衬底,例如硅衬底、二氧化硅衬底或其它硅类衬底。在各种实施例中,衬底可包含一或多种金属或电介质衬底,例如TiN、Mo、MoC、SiO

在某些实施例中,例如在例如二氧化硅的氧化物衬底或替代地硅或多晶硅衬底的情况下,衬底可经加工或制造以于其上包括势垒层(例如氮化钛)以用于后续沉积材料。

在一个实施例中,沉积于衬底表面上的含钼层可例如通过脉冲化学气相沉积(CVD)或原子层沉积(ALD)或其它气相沉积技术,无需预先形成晶核层且因此直接利用二氯二氧化钼(MoO

图4展示随用于从MoO

另外,图6描绘展示用于比较从MoO

另外,图7提供展示前体引入脉冲、H

利用二氯二氧化钼(MoO

图5描绘表示随用于两个反应器压力(60和80T)的H

在各种实施例中,在300℃到750℃范围内或如上文对于(MoO

更一般来说,根据本发明的在衬底上形成含钼材料的广义方法可包含气相沉积条件,所述气相沉积条件包含存在氢或其它还原气体。在存在或不存在氢的情况下,可将含钼材料沉积于势垒层或表面上。举例来说,势垒层可由氮化钛构成,且在存在氢的情况下,氮化钛层可与二氯二氧化钼(MoO

将了解,可以诸多替代方式且在多种工艺条件下进行本发明的方法。本发明的工艺可例如以在衬底上制得半导体装置的工艺形式进行。半导体装置可具有任何合适的类型,且可例如包含DRAM装置、3-D NAND装置、或其它装置或装置集成结构。在各种实施例中,衬底可包含其中沉积含钼材料的通孔。举例来说,装置可具有在2:1到40:1范围内的深度比横向尺寸的纵横比(L/W)(参见图1)。

根据本发明的用于沉积含钼材料的工艺化学反应可包括通过反应2MoO

在某些实施例中,本发明涉及一种在衬底上形成含钼材料的方法,其包含通过化学气相沉积(CVD)工艺利用二氯二氧化钼(MoO

可如本文中不同地描述以任何合适方式进行此类工艺。在特定实施例中,此类方法可通过包含化学气相沉积,例如脉冲化学气相沉积的气相沉积工艺来进行。可进行所述方法以使得所得含钼材料大体上由元素钼构成,且在各种实施例中,钼可在存在氢或其它适合的还原气体的情况下沉积在衬底表面上。在本发明的其它实施例中,MoO

一般来说,可进行用于在衬底上形成含钼材料的本发明的方法以实现以高水平的步阶式覆盖率,例如75%到100%的步阶式覆盖率沉积含钼材料。

形成于衬底上的含钼薄膜展现良好粘附特性。在一个实施例中,进行沉积而无需预处理二氧化硅衬底且通过ASTM D 3359-02-用于利用带测试测量粘附性的标准测试方法,所得钼薄膜展现>95%的粘附性。

本发明可进一步通过其优选实施例的以下实例说明,但应理解,除非另外具体指示,否则仅出于说明的目的包括这些实例且不打算限制本发明的范围。

通用程序:

可通过以下工艺步骤序列于在二氧化硅基底层上包含氮化钛势垒层的衬底上制造半导体装置。

步骤1:净化沉积腔室;

步骤2:在存在氢(H

步骤3;在H

步骤4:重复步骤1到3(任选的)以形成具有所需特征的钼薄膜层。

实例1

以下范围中的工艺参数;

1)在1标准立方厘米/分钟(sccm)到1000sccm范围内的前体流动。

2)在1到10000sccm范围内的惰性前体载气流动

3)在25sccm到25000sccm范围内的H

4)在0.1T到250T范围内的压力

5)300到1000℃范围内的衬底温度

6)脉冲CVD循环时间包括a)0.1秒到120秒的前体脉冲“启用”时间,b)1秒到120秒的前体脉冲“断开”时间

7)1到10000次循环的沉积循环

用于Al

在400℃到700℃的衬底温度下,持续1秒“启用”和39秒“断开”的20到200次沉积循环,在4000sccm(4lpm)H

用于SiO

在450℃到700℃的衬底温度下,持续1秒“启用”和39秒“断开”的20到200次沉积循环,在4lpm H

用于TiN衬底的实例3

在360℃到700℃的衬底温度下1秒“启用”和39秒“断开”的25到200次沉积循环,在4lpm H

- 用于在衬底上形成钼薄膜的方法

- 一种在钼基衬底上制备石墨烯薄膜的方法