一种Sigma-Delta型ADC数字处理装置

文献发布时间:2023-06-19 11:27:38

技术领域

本发明实施例涉及高精度信号处理技术,尤其涉及一种Sigma-Delta型ADC 数字处理装置。

背景技术

随着智能变电站的不断发展,电子式互感器得到了极大的推广和应用,并发挥出越来越重要的作用。但由于基于Rogowski线圈的电子式电流互感器(ECT)的直接输出量是一次侧电流信号的微分形式,且与该信号的相位相差90°,因此需要一个高精度数字积分器把测量信号还原成与被测电流信号成正比的量。然而,由于测量精度的限制,数字积分器应用不多,尤其是在谐波信号测量中存在相当大的误差。因此发明一种改进型数字积分器改善ECT测量的精度就显得非常重要。研究表明,通过增加单位周期采样点数或计算量可以改进数字积分器精度。然而,对于如何具体增加采样率和如何解决采样率提高带来的误差,实现相位信息的实时解算却鲜有提及。

发明内容

本发明提供一种Sigma-Delta型ADC 数字处理装置,以实现成本低,支持多种ADC采样率的需求,有效的滤除模拟调制器的高频噪声和直流,可以达到很高的信噪比。

本发明实施例提供了一种Sigma-Delta型ADC 数字处理装置,包括:

模拟模块,所述模拟模块用于采集电路电压并生成采样数据;

数字模块,所述数字模块与所述模拟模块连接,用于对所述采样数据进行下采和修正并提供时钟信号到所述模拟模块中。

可选的,所述模拟模块包括放大器和Sigma-Delta模拟调制器,所述放大器与所述Sigma-Delta模拟调制器连接。

可选的,所述放大器用于将所述电路电压的信号幅度进行增幅。

可选的,所述Sigma-Delta模拟调制器用于根据所述电路电压生成采样数据。

可选的,所述数字模块包括下采模块和高通滤波模块,所述下采模块与所述高通滤波模块连接,所述下采模块用于将所述采样数据下采到需要的采样率和位宽,所述高通滤波模块用于将消除所述采样数据的直流和低频分量。

可选的,所述下采模块包括梳状滤波器、补偿滤波器和半带滤波器,所述补偿滤波器连接在所述梳状滤波器与所述半带滤波器之间。

可选的,所述梳状滤波器包括三级滤波结构,所述梳状滤波器的传输函数表示为:

可选的,所述补偿滤波器为FIR低通滤波器,用于处理补偿带宽和抽取滤波。

可选的,所述半带滤波器为对称的FIR滤波器,用于抽取滤波。

可选的,所述高通滤波模块包括一个单极点的一阶IIR滤波器,其时阈表达式为:

本发明实施例公开了一种Sigma-Delta型ADC 数字处理装置,包括:模拟模块,所述模拟模块用于采集电路电压并生成采样数据;数字模块,所述数字模块与所述模拟模块连接,用于对所述采样数据进行下采和修正并提供时钟信号到所述模拟模块中。本发明实施例提供的一种Sigma-Delta型ADC 数字处理装置通过数字抽取滤波和高通滤波数字处理的技术方案,解决了现有技术中成本高和信噪比低的问题,实现了成本低,支持多种ADC采样率的需求,有效的滤除模拟调制器的高频噪声和直流,可以达到很高的信噪比。

附图说明

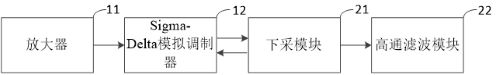

图1为本发明实施例一提供的一种Sigma-Delta型ADC 数字处理装置的模块连接图;

图2为本发明实施例中一种Sigma-Delta型ADC 数字处理装置的电路模块连接图;

图3为本发明实施例一中高通滤波模块的结构示意图;

图4为本发明实施例二中下采模块的模块连接图;

图5为本发明实施例二中梳状滤波器的结构示意图;

图6为本发明实施例二中补偿滤波器的结构示意图。

具体实施方式

下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

在更加详细地讨论示例性实施例之前应当提到的是,一些示例性实施例被描述成作为流程图描绘的处理或方法。虽然流程图将各步骤描述成顺序的处理,但是其中的许多步骤可以被并行地、并发地或者同时实施。此外,各步骤的顺序可以被重新安排。当其操作完成时处理可以被终止,但是还可以具有未包括在附图中的附加步骤。处理可以对应于方法、函数、规程、子例程、子程序等等。

此外,术语“第一”、“第二”等可在本文中用于描述各种方向、动作、步骤或元件等,但这些方向、动作、步骤或元件不受这些术语限制。这些术语仅用于将第一个方向、动作、步骤或元件与另一个方向、动作、步骤或元件区分。举例来说,在不脱离本申请的范围的情况下,可以将第一模块为第二模块,且类似地,可将第二模块称为第一模块。第一模块和第二模块两者都是模块,但其不是同一模块。术语“第一”、“第二”等而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

实施例一

图1为本发明实施例一提供的一种Sigma-Delta型ADC 数字处理装置的模块连接图,本发明实施例提供的一种Sigma-Delta型ADC 数字处理装置适用于数模转换的情况,具体地,本发明实施例一提供的一种Sigma-Delta型ADC 数字处理装置包括:模拟模块1和数字模块2。

所述模拟模块1用于采集电路电压并生成采样数据。所述模拟模块1包括放大器11和Sigma-Delta模拟调制器12,所述放大器11与所述Sigma-Delta模拟调制器12连接。

图2为本实施例中一种Sigma-Delta型ADC 数字处理装置的电路模块连接图,在本实施例中,所述放大器11用于将所述电路电压的信号幅度进行增幅。放大器11是增加信号幅度或功率的装置,它是自动化技术工具中处理信号的重要元件。运算放大器11是模数转换电路中的一个最通用、最重要的的单元。全差分运放是指输入和输出都是差分信号的运放, 与普通的单端输出运放相比有以下几个优点:输出的电压摆幅较大;较好的抑制共模噪声;更低的噪声;抑制谐波失真的偶数阶项比较好等。因此通常高性能的运放多采用全差分形式。所述Sigma-Delta模拟调制器12用于根据所述电路电压生成采样数据。Sigma-delta调制器具有非常良好的除噪性能,现在主要有三种结构,如单环结构,级联结构以及误差反馈结构都可以很好的完成噪声滤除功能,可以根据设计的需要求来选择调制器的结构,特别是数字调制器的出现,较模拟而言,其可靠性强,容易用简单的电路来实现,并且还可以组成相当复杂、精确和高速的系统等优点,现在已经成为DAC和ADC的设计主流。Sigma-delta调制系统特别在坨螺系统中得到了方泛的应用,其调制系统与数字插值滤器以及D/A转换器(以下简称DAC)构成一个Sigma-delta DAC,较传统的DAC相比,其转换精度以及信噪比都有一个良好的改进,也放宽了对后级模拟电路的设计要求,简化了模拟电路设计的复杂度。

所述数字模块2包括下采模块21和高通滤波模块22,所述下采模块21与所述高通滤波模块22连接,所述下采模块21用于将所述采样数据下采到需要的采样率和位宽,所述高通滤波模块22用于将消除所述采样数据的直流和低频分量。

在本实施例中,下采模块21用于将模拟调制器的数据下采到需要的采样率和位宽,ADC 模拟调制器的过采样率为128,下采模块21需要完成128倍下采。高通滤波模块22用于消除直流和低频分量。具体地,所述高通滤波模块22包括一个单极点的一阶IIR滤波器,其时阈表达式为:

本发明实施例公开了一种Sigma-Delta型ADC 数字处理装置,包括:模拟模块,所述模拟模块用于采集电路电压并生成采样数据;数字模块,所述数字模块与所述模拟模块连接,用于对所述采样数据进行下采和修正并提供时钟信号到所述模拟模块中。本发明实施例提供的一种Sigma-Delta型ADC 数字处理装置通过数字抽取滤波和高通滤波数字处理的技术方案,解决了现有技术中成本高和信噪比低的问题,实现了成本低,支持多种ADC采样率的需求,有效的滤除模拟调制器的高频噪声和直流,可以达到很高的信噪比。

实施例二

图1为本发明实施例二提供的一种Sigma-Delta型ADC 数字处理装置的模块连接图,本发明实施例提供的一种Sigma-Delta型ADC 数字处理装置适用于数模转换的情况,具体地,本发明实施例二提供的一种Sigma-Delta型ADC 数字处理装置包括:模拟模块1和数字模块2。

所述模拟模块1用于采集电路电压并生成采样数据。所述模拟模块1包括放大器11和Sigma-Delta模拟调制器12,所述放大器11与所述Sigma-Delta模拟调制器12连接。

图2为本实施例中一种Sigma-Delta型ADC 数字处理装置的电路模块连接图,在本实施例中,所述放大器11用于将所述电路电压的信号幅度进行增幅。放大器11是增加信号幅度或功率的装置,它是自动化技术工具中处理信号的重要元件。运算放大器11是模数转换电路中的一个最通用、最重要的的单元。全差分运放是指输入和输出都是差分信号的运放, 与普通的单端输出运放相比有以下几个优点:输出的电压摆幅较大;较好的抑制共模噪声;更低的噪声;抑制谐波失真的偶数阶项比较好等。因此通常高性能的运放多采用全差分形式。所述Sigma-Delta模拟调制器12用于根据所述电路电压生成采样数据。Sigma-delta调制器具有非常良好的除噪性能,现在主要有三种结构,如单环结构,级联结构以及误差反馈结构都可以很好的完成噪声滤除功能,可以根据设计的需要求来选择调制器的结构,特别是数字调制器的出现,较模拟而言,其可靠性强,容易用简单的电路来实现,并且还可以组成相当复杂、精确和高速的系统等优点,现在已经成为DAC和ADC的设计主流。Sigma-delta调制系统特别在坨螺系统中得到了方泛的应用,其调制系统与数字插值滤器以及D/A转换器(以下简称DAC)构成一个Sigma-delta DAC,较传统的DAC相比,其转换精度以及信噪比都有一个良好的改进,也放宽了对后级模拟电路的设计要求,简化了模拟电路设计的复杂度。

所述数字模块2包括下采模块21和高通滤波模块22,所述下采模块21与所述高通滤波模块22连接,所述下采模块21用于将所述采样数据下采到需要的采样率和位宽,所述高通滤波模块22用于将消除所述采样数据的直流和低频分量。

在本实施例中,下采模块21用于将模拟调制器的数据下采到需要的采样率和位宽,ADC 模拟调制器的过采样率为128,下采模块21需要完成128倍下采。在本实施例中,下采模块21如图4所示,下采模块21包括梳状滤波器211、补偿滤波器212和半带滤波器213,所述补偿滤波器212连接在所述梳状滤波器211与所述半带滤波器213之间。下采由三部分组成,梳状滤波器211完成32倍下采,补偿滤波器212完成2倍下采,半带滤波器213完成2倍下采。为了支持不同的采样率,只需要数字给ADC 模拟调制器提供不同的时钟。如实现48KHz采样率需提供6.144MHz,实现8K采样率需提供1.024MHz的时钟。所述梳状滤波器211包括三级滤波结构,所述梳状滤波器211的传输函数表示为:

所述补偿滤波器212为FIR低通滤波器,用于处理补偿带宽和抽取滤波。FIR(Finite Impulse Response)滤波器:有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。补偿滤波器212是一个FIR低通滤波器。在本实施例中,补偿滤波器212作用为补偿CIC滤波器的带内不平坦和作为2倍抽取滤波器。本方案的补偿滤波器212为64阶,具体地,量化后的系数h1为:

[0.000614166259765625 0.00107574462890625 -0.000240325927734375 -0.00133132934570313 0.000785827636718750 0.00185203552246094 -0.00187683105468750 -0.00230026245117188 0.003572463989257810.00216293334960938 -0.00601196289062500 -0.001043319702148440.00886535644531250 -0.00175285339355469 -0.01171302795410160.00661849975585938 0.0135364532470703 -0.0139751434326172 -0.0132007598876953 0.0236721038818359 0.00901031494140625 -0.03539848327636720.000877380371093750 0.0482978820800781 -0.0193748474121094 -0.0618400573730469 0.0520286560058594 0.0769767761230469 -0.117319107055664 -0.108839035034180 0.330829620361328 0.632328033447266 0.330829620361328 -0.108839035034180 -0.117319107055664 0.0769767761230469 0.0520286560058594 -0.0618400573730469 -0.0193748474121094 0.04829788208007810.000877380371093750 -0.0353984832763672 0.009010314941406250.0236721038818359 -0.0132007598876953 -0.0139751434326172 0.01353645324707030.00661849975585938 -0.0117130279541016 -0.001752853393554690.00886535644531250 -0.00104331970214844 -0.006011962890625000.00216293334960938 0.00357246398925781 -0.00230026245117188 -0.00187683105468750 0.00185203552246094 0.000785827636718750 -0.00133132934570313 -0.000240325927734375 0.001075744628906250.000614166259765625] 补偿滤波器212有一个尺度因子Scale1,滤波后的数据乘以2scale1来实现放大和缩小信号。Scale1的范围为-2~2。FIR的实现结构如图6所示, FIR滤波器是有一个 “抽头延迟线”加法器和乘法器的集合构成的。x(n)是输入,y(n)是输出。传给每个乘法器的操作数h(n)就是一个滤波器的系数。

所述半带滤波器213为对称的FIR滤波器,用于抽取滤波。半带滤波器213作为一种对称的FIR滤波器,其计算效率高,实时性强,所以适合二倍抽取。本方案的补偿滤波器212为55阶,位宽为S(20,19) 。量化后的系数h2为:

半带滤波器213系数为:[-0.000820159912109375 0 0.00122642517089844 0 [-0.00209808349609375 0 0.00333404541015625 0 -0.00503540039062500 00.00732612609863281 0 -0.0103740692138672 0 0.0144329071044922 0 -0.0199241638183594 0 0.0276260375976563 0 -0.0392093658447266 00.0590553283691406 0 -0.103282928466797 0 0.317359924316406 0.5000000000000000.317359924316406 0 -0.103282928466797 0 0.0590553283691406 0 -0.0392093658447266 0 0.0276260375976563 0 -0.0199241638183594 00.0144329071044922 0 -0.0103740692138672 0 0.00732612609863281 0 -0.00503540039062500 0 0.00333404541015625 0 -0.00209808349609375 00.00122642517089844 0 -0.000820159912109375] 半带滤波器213与补偿滤波器212实现结构相同,半带滤波器213也有一个量化因子Scale2,滤波后的数据乘以2scale2来实现放大和缩小信号。Scale2的范围为-2~2。

高通滤波模块22用于消除直流和低频分量。具体地,所述高通滤波模块22包括一个单极点的一阶IIR滤波器,其时阈表达式为:

本发明实施例公开了一种Sigma-Delta型ADC 数字处理装置,包括:模拟模块,所述模拟模块用于采集电路电压并生成采样数据;数字模块,所述数字模块与所述模拟模块连接,用于对所述采样数据进行下采和修正并提供时钟信号到所述模拟模块中。本发明实施例提供的一种Sigma-Delta型ADC 数字处理装置通过数字抽取滤波和高通滤波数字处理的技术方案,解决了现有技术中成本高和信噪比低的问题,实现了成本低,支持多种ADC采样率的需求,有效的滤除模拟调制器的高频噪声和直流,可以达到很高的信噪比。

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

- 一种Sigma-Delta型ADC数字处理装置

- 一种部分分裂流水线逐次逼近型ADC数字电路