芯片封装结构及芯片封装结构及其形成方法

文献发布时间:2023-06-19 12:14:58

技术领域

本公开涉及一种芯片封装结构及其形成方法。

背景技术

在各种电子应用,例如个人电脑、手机、数字相机和其他电子装置中使用了半导体装置。通常通过在半导体基板上依序沉积绝缘层或介电层、导电层和半导体层,并使用光刻工艺来图案化各种材料层,以在材料层上形成电路部件和元件来制造半导体装置。

通常会在单个半导体晶片上制造出数十个或数百个集成电路。通过沿着切割道锯切集成电路以单粒化裸片。然后将各个裸片分开封装以形成封装体。半导体工业通过不断降低最小特征尺寸,而不断提高各种电子部件(例如晶体管、二极管、电阻、电容等)的整合密度,从而可将更多的部件整合到给定的区域中。然而,由于特征尺寸持续降低,所以变得更加难以继续执行工艺。因此,如何形成具有高整合密度的电子元件的可靠封装体是一种挑战。

发明内容

本公开的目的在于提出一种芯片封装结构及用于形成芯片封装结构的方法,以解决上述至少一个问题。

本公开一些实施例提供一种用于形成芯片封装结构的方法,包括提供线路基板、在聚合物层以及导电垫上方形成导电粘合层、在导电粘合层上方形成镍层以及将芯片通过导电凸块接合到线路基板。线路基板包括基板、导电垫以及聚合物层,聚合物层位于基板以及导电垫上方,且聚合物层具有露出导电垫的一第一开口。导电粘合层直接接触并共形地覆盖聚合物层以及导电垫。镍层比导电粘合层厚,且镍层以及导电粘合层由不同的材料所形成。导电凸块位于镍层以及芯片之间。

本公开一些实施例提供一种用于形成芯片封装结构的方法,包括提供线路基板,线路基板包括基板、第一导电垫以及第一聚合物层,第一导电垫位于基板的第一表面上方,第一聚合物层位于第一表面以及第一导电垫上方,第一聚合物层具有第一开口,第一开口露出第一导电垫;在第一聚合物层以及第一导电垫上方形成第一导电粘合层,第一导电粘合层直接接触第一聚合物层以及第一导电垫;在第一导电粘合层上方形成焊料结构;以及通过下凸块冶金层以及第一导电凸块将芯片接合到线路基板,下凸块冶金层位于芯片以及第一导电凸块之间,导电凸块连接到第一导电粘合层以及下凸块冶金层,焊料结构形成一部分的第一导电凸块,且下凸块冶金层的第一厚度实质上等于第一导电粘合材料层的第二厚度。

本公开一些实施例提供一种芯片封装结构,包括线路基板、导电粘合层、镍层、芯片以及导电凸块。线路基板包括基板、第一导电垫、第二导电垫以及聚合物层,第一导电垫以及第二导电垫分别位于基板的第一表面以及第二表面上方,第一导电垫比第二导电垫窄,且聚合物层位于第一表面以及第一导电垫上方。导电粘合层穿过聚合物层且位于第一导电垫上方,其中导电粘合层直接接触聚合物层以及第一导电垫。镍层位于导电粘合层上方,其中镍层比导电粘合层厚,且镍层以及导电粘合层由不同的材料形成。芯片位于线路基板上方。导电凸块位于镍层以及芯片之间。

附图说明

以下将配合所附附图详述本公开的实施例。应注意的是,依据在业界的标准做法,多种特征并未按照比例示出且仅用以说明例示。事实上,可能任意地放大或缩小元件的尺寸,以清楚地表现出本公开的特征。

图1A至图1E是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。

图2是根据一些实施例的用于形成芯片封装结构的工艺的阶段的剖面图。

图3A至图3C是根据一些实施例的用于形成芯片封装结构的工艺各个阶段的剖面图。

图4是根据一些实施例的用于形成芯片封装结构的工艺的阶段的剖面图。

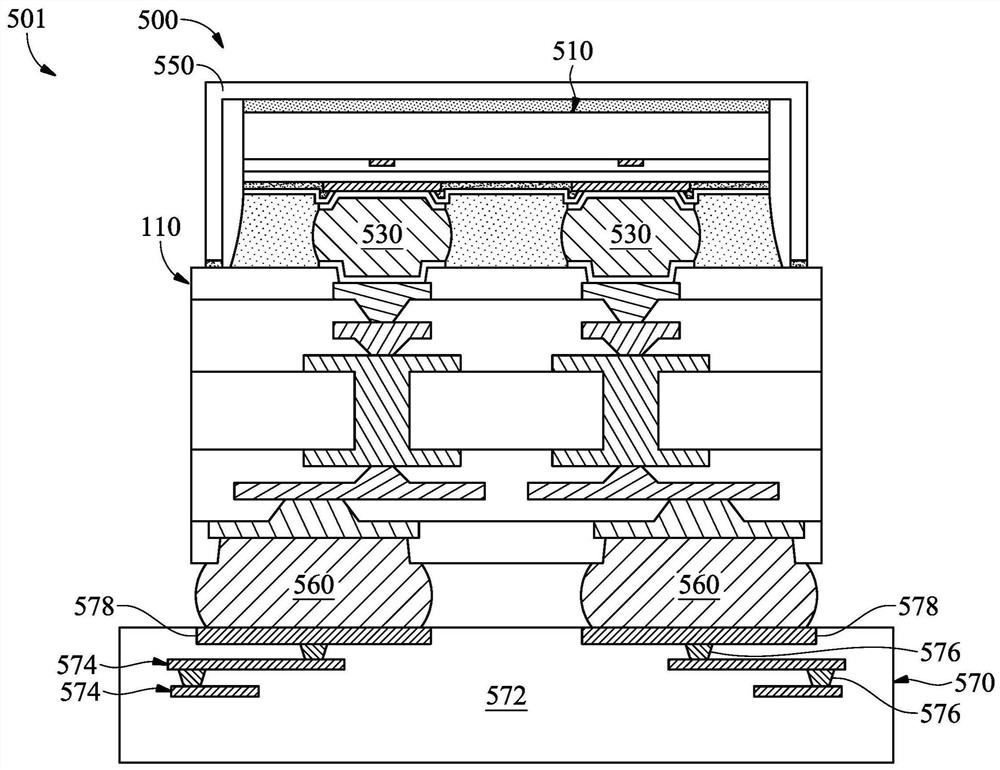

图5A至图5D是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。

图6A至图6E是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。

图7A至图7C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。

图8A至图8D是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。

图9A至图9C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。

图10A至图10C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。

图11A至图11C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。

附图标记如下:

110:线路基板

111:基板

111a,111b:表面

112:基板通孔

113a,113b,114a,114b,574:线路层

115a,115b,515,578:导电垫

115a1,118a1,142,922,932,1032:顶表面

116a,116b,576:导孔

117a,117b:绝缘层

118a,118b:聚合物层

120,610:导电粘合层

120a,610a:导电粘合材料层

122,124:导电层

122a,124a:材料层

122b,124b,924,934,1034:侧壁

124a1,132,322,516a,517a,622,812,1012,1112,P1,P2:开口

130,310,320,620,710,810,910,1010,1110:掩模层

140,530a:焊料结构

140a,140b,1150a:焊料层

140c,1150:焊球

500,501,600,601,700,800,801,900,901,1000,1001,1100,1101:芯片封装结构

510:芯片

511:半导体基板

511a:前表面

511b:后表面

512:元件

513:介电层

514:内连线层

516,572:绝缘层

517:缓冲层

520:凸块下冶金层

530:导电凸块

540,541:粘着层

550:散热盖

560:导电凸块

570:线路基板

820,920,1020,1120:镍层

830,930,1030,1130:钯层

840,940,1140:金层

1022,1122:凹槽

1040:盖层

A:切割道

T1,T2,T3,T4,T5,T6:厚度

U:底部填充层

W1,W2,W3,W4:宽度

具体实施方式

以下公开许多不同的实施方法或是范例来实行所提供的标的的不同特征,以下描述具体的元件及其排列的实施例以阐述本公开。当然这些实施例仅用以例示,且不该以此限定本公开的范围。举例来说,在说明书中提到第一特征部件形成于第二特征部件上方,其包括第一特征部件与第二特征部件是直接接触的实施例,另外也包括于第一特征部件与第二特征部件之间另外有其他特征的实施例,也就是说,第一特征部件与第二特征部件并非直接接触。此外,在不同实施例中可能使用重复的标号或标示,这些重复仅为了简单清楚地叙述本公开,不代表所讨论的不同实施例及/或结构之间有特定的关系。

此外,其中可能用到与空间相关用词,例如“在下方”、“下方”、“下”、“上方”、“上”及类似的用词,这些空间相关用词为了便于描述图示中一个(些)元件或特征与另一个(些)元件或特征之间的关系,这些空间相关用词旨在涵盖包括特征的装置的不同方向。当设备被转向不同方位时(旋转90度或其他方位),则其中所使用的空间相关形容词也将依转向后的方位来解释。应理解的是,可以在上述方法前、中、后提供额外的操作,并且对于上述方法的其他实施例来说,可以取代或去除所描述的一些操作。

以下对本公开的一些实施例进行描述。可以在所述实施例中描述的阶段之前、之中及/或之后提供额外的操作。对于不同的实施例,可以更换或去除所述的某些阶段。可以在半导体装置结构中增加额外的特征。对于不同的实施例,可以更换或去除以下描述的某些功能。尽管通过使用特定顺序来执行的操作以讨论一些实施例,但是可以通过其他的逻辑顺序来执行所述操作。

图1A至图1E是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。如图1A所示,根据一些实施例,提供了线路基板110。根据一些实施例,线路基板110包括基板111、基板通孔(或镀通孔(plated through holes PTH))112、线路层113a、线路层113b、线路层114a和线路层114b、导电垫115a和导电垫115b、导孔116a和导孔116b、绝缘层117a和绝缘层117b,以及聚合物层118a和聚合物层118b。

根据一些实施例,基板111具有表面111a和表面111b。根据一些实施例,表面111a与表面111b相反。在一些实施例中,基板111由绝缘材料制成,例如纤维材料、聚合物材料(例如聚合物有机材料)或玻璃材料。举例来说,纤维材料包括玻璃纤维材料。

在一些其他实施例中,根据一些实施例,基板111由半导体材料或导电材料制成。半导体材料包括例如硅或锗。导电材料包括例如金属材料。

根据一些实施例,基板通孔112穿过基板111。根据一些实施例,线路层113a和线路层113b分别形成在表面111a和表面111b上方。根据一些实施例,基板通孔112将线路层113a电性连接至线路层113b。

根据一些实施例,如果基板111由半导体材料或导电材料制成,则在基板111与基板通孔112之间以及基板111与线路层113a和线路层113b之间形成绝缘层(未示出),以使基板111与基板通孔112以及线路层113a和线路层113b电性绝缘。

根据一些实施例,在表面111a上形成线路层114a、导电垫115a、导孔116a、绝缘层117a、和聚合物层118a。根据一些实施例,线路层114a和导孔116a位于绝缘层117a中。根据一些实施例,导电垫115a位于绝缘层117a上方。根据一些实施例,导孔116a在线路层113a和线路层114a之间以及在线路层114a和导电垫115a之间提供电性连接。

根据一些实施例,聚合物层118a形成在绝缘层117a和导电垫115a上方。根据一些实施例,聚合物层118a具有开口P1。根据一些实施例,开口P1分别露出其下方的导电垫115a。根据一些实施例,聚合物层118a部分地覆盖导电垫115a。

根据一些实施例,聚合物层118a是阻焊剂(solder resist,SR)层、味之素积层膜(Ajinomoto build-up film,ABF)或预浸材料(prepreg,PP)。根据一些实施例,阻焊剂层由阻焊剂材料制成。根据一些实施例,聚合物层118a由任何合适的聚合物材料制成,例如树脂或聚酰亚胺(polyimide)。

根据一些实施例,在表面111b上方形成线路层114b、导电垫115b、导孔116b、绝缘层117b、和聚合物层118b。根据一些实施例,线路层114b和导孔116b位于绝缘层117b中。根据一些实施例,导电垫115b位于绝缘层117b上方。根据一些实施例,导孔116b在线路层113b和线路层114b之间以及在线路层114b和导电垫115b之间提供电性连接。

根据一些实施例,聚合物层118b形成在绝缘层117b和导电垫115b上方。根据一些实施例,聚合物层118b具有开口P2。根据一些实施例,开口P2分别露出导电垫115b。根据一些实施例,聚合物层118b部分地覆盖导电垫115b。

根据一些实施例,聚合物层118b是阻焊剂层、味之素积层膜或预浸材料。根据一些实施例,阻焊剂层由阻焊剂(SR)材料制成。根据一些实施例,聚合物层118b由任何合适的聚合物材料制成,例如树脂或聚酰亚胺。

在一些实施例中,导电垫115a比导电垫115b窄。换句话说,根据一些实施例,导电垫115b的宽度W1大于导电垫115a的宽度W2。根据一些实施例,宽度W1在大约200μm至大约600μm的范围内。根据一些实施例,宽度W2在大约20μm至大约110μm的范围内。在一些实施例中,开口P2的(最大)宽度W3大于开口P1的(最大)宽度W4。

基板通孔112、线路层113a、线路层113b、线路层114a和线路层114b、导电垫115a和导电垫115b以及导孔116a和导孔116b由导电材料制成,例如金属材料或其合金,根据一些实施例。根据一些实施例,金属材料包括铝、铜或钨。

如图1A所示,根据一些实施例,在聚合物层118a和导电垫115a上方形成导电粘合材料层120a。根据一些实施例,导电粘合材料层120a共形地(conformally)覆盖聚合物层118a的顶表面118a1、开口P1的内壁S、和导电垫115a的顶表面115a1。

根据一些实施例,导电粘合材料层120a与聚合物层118a和导电垫115a直接接触。根据一些实施例,导电粘合材料层120a穿过聚合物层118a。根据一些实施例,导电粘合材料层120a是单层结构。在一些其他实施例中,导电粘合材料层120a是多层结构。

根据一些实施例,导电粘合材料层120a由镍(Ni)、钛(Ti)、铜(Cu)、钯(Pd)、其合金、其组合或其他合适的金属或合金制成。根据一些实施例,使用沉积工艺(例如溅镀工艺)或镀层(plating)工艺(例如无电镀层(electroless plating)工艺)形成导电粘合材料层120a。

如图1B所示,根据一些实施例,在导电粘合材料层120a上方形成掩模层130。根据一些实施例,掩模层130具有开口132。根据一些实施例,开口132露出在导电垫115a上方或附近的导电粘合材料层120a。根据一些实施例,掩模层130由光刻胶材料制成,例如聚合物材料。

如图1B所示,根据一些实施例,在开口132中形成焊料层140a。根据一些实施例,焊料层140a形成在导电粘合材料层120a上方。根据一些实施例,焊料层140a与导电粘合材料层120a直接接触。

根据一些实施例,由如锡(Sn)或锡合金的合适的焊接材料制成焊料层140a。根据一些实施例,使用镀层工艺来形成焊料层140a,例如电镀(electroplating)工艺。根据一些实施例,导电粘合材料层120a在电镀工艺中作为籽晶层。

如图1B至图1C所示,根据一些实施例,去除了掩模层130和掩模层130下的导电粘合材料层120a。根据一些实施例,在焊料层140a下方所剩下的导电粘合材料层120a形成导电粘合层120。根据一些实施例,导电粘合层120能够改善焊料层140a与聚合物层118a之间以及焊料层140a与导电垫115a之间的黏附关系。

如图1D所示,根据一些实施例,在焊料层140a上执行回焊(reflow)工艺。根据一些实施例,回焊后的焊料层140a形成焊料结构140。根据一些实施例,焊料结构140具有顶表面142。根据一些实施例,顶表面142是弯曲的顶表面。根据一些实施例,回焊工艺的工艺温度在约200℃至约300℃的范围内。

如图1E所示,根据一些实施例,在焊料结构140上执行热压(thermo-compression)工艺以使焊料结构140的顶表面142变平。根据一些实施例,热压工艺的工艺温度在约50℃至约150℃的范围内。

在一些实施例中,导电粘合层120是单层结构。在一些其他实施例中,如图2所示,根据一些实施例,导电粘合层120是多层结构。根据一些实施例,导电粘合层120包括导电层122和导电层124。

在一些实施例中,导电层122由铜制成,并且导电层124由镍制成。在一些其他实施例中,根据一些实施例,导电层122由钛制成,并且导电层124由铜制成。在另一些实施例中,根据一些实施例,导电层122由钯制成,并且导电层124由铜制成。

图3A至图3C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。如图3A所示,根据一些实施例,在图1A的步骤之后,在导电垫115a上方或附近的导电粘合材料层120a上方形成掩模层310。根据一些实施例,掩模层310也被称为干膜(dryfilm)。根据一些实施例,掩模层310由聚合物材料制成。

如图3A至3B图所示,根据一些实施例,去除了从掩模层310露出的导电粘合材料层120a。根据一些实施例,留在掩模层310下方的导电粘合材料层120a形成了导电粘合层120。

如图3C所示,根据一些实施例,去除了掩模层310。如图3C所示,根据一些实施例,在聚合物层118a上方形成掩模层320。根据一些实施例,掩模层320具有露出导电粘合层120的开口322。根据一些实施例,掩模层320由光刻胶材料制成,例如聚合物材料。

如图3C所示,根据一些实施例,执行印刷(printing)工艺以在开口322中形成焊料层140b。根据一些实施例,焊料层140b由如锡(Sn)或锡合金的合适的焊接材料制成。此后,根据一些实施例,如图1D所示,去除掩模层320,并在焊料层140b上执行回焊工艺以形成焊料结构140。

图4是根据一些实施例的用于形成芯片封装结构的工艺的阶段的剖面图。如图4所示,根据一些实施例,在图3B的步骤之后去除掩模层310。如图4所示,根据一些实施例,焊球140c设置在导电粘合层120上方。此后,如图1D所示,根据一些实施例,对焊球140c进行回焊以形成焊料结构140。

图5A至图5D是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。如图5A所示,根据一些实施例,在图1E的步骤之后提供芯片510。根据一些实施例,芯片510包括半导体基板511、元件512、介电层513、内连线层514、导电垫515、绝缘层516、和缓冲层517。

根据一些实施例,半导体基板511具有前表面511a和与前表面511a相反的后表面511b。在一些实施例中,半导体基板511由至少一种元素半导体材料制成,包括具有单晶、多晶或非晶结构的硅或锗。在一些其他实施例中,半导体基板511由化合物半导体制成,例如碳化硅、砷化镓、磷化镓、磷化铟、砷化铟,或由合金半导体制成,例如SiGe或GaAsP或其组合。半导体基板511还可包括多层半导体、绝缘体上半导体(semiconductor on insulator(SOI),例如绝缘体上硅或绝缘体上锗)或其组合。

在一些实施例中,元件512形成在前表面511a上方或邻近前表面511a的半导体基板511中。根据一些实施例,元件512包括有源元件(例如晶体管、二极管等)及/或无源元件(例如电阻、电容、电感等)。

根据一些实施例,介电层513形成在前表面511a和元件512上。根据一些实施例,介电层513由氧化物材料制成,例如氧化硅。在一些其他实施例中,介电层513由聚合物材料制成,例如聚苯并恶唑(polybenzoxazole,PBO)、聚酰亚胺、苯并环丁烯(benzocyclobutene,BCB)、环氧树脂、光敏材料或其他合适的材料。

根据一些实施例,内连线层514形成在介电层513上方。根据一些实施例,内连线层514包括介电层(未示出)和在介电层中的导电内连线结构(未示出)。

根据一些实施例,导电垫515形成在内连线层514上。根据一些实施例,导电垫515经过内连线层514电性连接到元件512。根据一些实施例,导电垫515由导电材料制成,例如铜(Cu)、铜合金、铝(Al)、铝合金、钨(W)、钨合金、钛(Ti)、钛合金、钽(Ta)或钽合金。

根据一些实施例,绝缘层516形成在内连线层514和导电垫515的外围部分上方。根据一些实施例,绝缘层516具有开口516a,开口516a露出导电垫515的中心部分。

根据一些实施例,绝缘层516由介电材料制成,例如未掺杂的硅酸盐玻璃(undopedsilicate glass,USG)、氮化硅、氧化硅或氮氧化硅。根据一些实施例,使用沉积工艺(例如化学气相沉积工艺或物理气相沉积工艺)和蚀刻工艺来形成绝缘层516。

根据一些实施例,缓冲层517形成在绝缘层516上方。根据一些实施例,缓冲层517还形成在导电垫515的外围部分上方。

根据一些实施例,缓冲层517具有开口517a,开口517a露出导电垫515的中心部分。根据一些实施例,缓冲层517用于缓冲在随后的接合工艺期间在导电垫515上方形成的凸块的接合应力。

根据一些实施例,缓冲层517由比绝缘层516及/或导电垫515更软的材料制成。根据一些实施例,缓冲层517由如环氧树脂、聚酰亚胺、苯并环丁烯(BCB)、聚苯并恶唑(PBO)的聚合物材料或其他合适的材料制成。

如图5A所示,根据一些实施例,在导电垫515和邻近于导电垫515的缓冲层517上形成凸块下冶金层(under bump metallurgy,UBM)520。根据一些实施例,凸块下冶金层520由钛、氮化钛、钽、氮化钽、铜制成,或由包括银、铬、镍、锡及/或金的铜合金制成。

如图5A所示,根据一些实施例,焊料结构530a形成在凸块下冶金层520上方。根据一些实施例,焊料结构530a由如锡(Sn)或锡合金的合适的焊接材料制成。

如图5B所示,根据一些实施例,芯片510通过导电凸块530接合到线路基板110。根据一些实施例,导电凸块530位于导电粘合层120和凸块下冶金层520之间,并连接到导电粘合层120和凸块下冶金层520。在一些实施例中,导电凸块530由图1E和图5A中的焊料结构140和焊料结构530a形成。

在一些实施例中,导电粘合层120的厚度T1实质上等于凸块下冶金层520的厚度T2。根据一些实施例,厚度T1的范围在约0.5μm至约2μm之间。根据一些实施例,厚度T2在大约0.5μm至大约2μm的范围内。

根据一些实施例,本申请中的用语“实质上等于”是指“在10%以内”。举例来说,根据一些实施例,用语“实质上等于”是指厚度T1和厚度T2之间的差异在凸块下冶金层520和导电粘合层120的平均厚度的10%之内。这种差异可能是由于工艺所造成的。

根据一些实施例,由于厚度T1实质上等于厚度T2,因此由导电粘合层120施加到导电凸块530的拉伸应力(tensile stress)实质上等于由凸块下冶金层520施加到导电凸块530的拉伸应力。因此,根据一些实施例,在导电凸块530中,由导电粘合层120和凸块下冶金层520施加的拉伸应力实质上彼此平衡。

根据一些实施例,拉伸应力的平衡防止了导电凸块530产生裂纹。根据一些实施例,因此提高了导电凸块530的良率。根据一些实施例,具有导电粘合层120、凸块下冶金层520、和导电凸块530的晶片封装结构的良率也得以提高。

如图5B所示,根据一些实施例,在芯片510和线路基板110之间形成底部填充层U。根据一些实施例,底部填充层U围绕导电凸块530。根据一些实施例,底部填充层U包括绝缘材料,例如聚合物材料。

如图5B所示,根据一些实施例,在线路基板110上方形成粘合层540。根据一些实施例,粘着层540围绕芯片510和底部填充层U。根据一些实施例,粘合层540具有环形的形状。根据一些实施例,粘合层540由聚合物制成,例如环氧树脂或硅氧树脂。根据一些实施例,使用点胶(dispensing)工艺来形成粘合层540。

如图5B所示,根据一些实施例,在晶片510上方形成粘合层541。根据一些实施例,粘合层541由银浆、锡浆、金属粉末和聚合物的混合物或具有良好导热性的其他合适的黏合材料所制成。根据一些实施例,使用点胶工艺来形成粘合层541。

如图5B所示,根据一些实施例,散热盖550设置在晶片510和粘合层540和粘合层541上方。根据一些实施例,散热盖550由高导热率材料制成,例如金属材料(铝或铜)、合金材料(例如不锈钢)或碳化铝硅(AlSiC)。在另一些实施例中,首先在散热盖550上形成粘合层540和粘合层541,然后将散热盖550、粘合层540、和粘合层541设置在晶片510和线路基板110上方。

如图5C所示,根据一些实施例,在导电垫115b上方和开口P2中形成导电凸块560。根据一些实施例,由如锡(Sn)或锡合金的合适的焊接材料制成导电凸块560。

如图5C所示,根据一些实施例,沿着切割道A在线路基板110上执行切割工艺,以切穿线路基板110来形成芯片封装结构500。

如图5D所示,根据一些实施例,芯片封装结构500通过导电凸块560接合到线路基板570。根据一些实施例,线路基板570包括绝缘层572、线路层574、导孔576、和导电垫578。

根据一些实施例,线路层574和导孔576位于绝缘层572中。根据一些实施例,导电垫578位于绝缘层572上。根据一些实施例,导孔576在线路层574之间提供电性连接,以及在线路层574和导电垫578之间提供电性连接。

根据一些实施例,线路层574、导孔576、和导电垫578由导电材料制成,例如金属材料或其合金。金属材料包括铝、铜或钨。

根据一些实施例,在此步骤中实质上形成了芯片封装结构(或板级封装结构,board-level package structure)501。根据一些实施例,芯片封装结构501包括芯片封装结构500、导电凸块560、和线路基板570。根据一些实施例,芯片封装结构501是球栅阵列(ball grid array,BGA)封装结构。

图6A至图6E是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。根据一些实施例,如图6A所示,图6A的步骤类似于图1A的步骤,除了图6A的步骤在将导电粘合材料层120a形成在聚合物层118a和导电垫115a上方的期间还在聚合物层118b和导电垫115b上方形成导电粘合材料层610a。

在一些实施例中,导电粘合材料层120a和导电粘合材料层610a由相同的材料制成。根据一些实施例,导电粘合材料层610a由镍(Ni)、钛(Ti)、铜(Cu)、钯(Pd)、其合金、其组合或其他合适的金属或合金制成。根据一些实施例,使用沉积工艺来形成导电粘合材料层610a,例如无电电镀工艺。

在一些其他实施例(未示出)中,导电粘合材料层120a和导电粘合材料层610a以不同的工艺形成。根据一些实施例,导电粘合材料层120a和导电粘合材料层610a由不同的材料制成。

如图6B所示,根据一些实施例,执行图1B至图1E和图5A至图5B的步骤,以形成在线路基板110上方的导电粘合层120、芯片510、凸块下冶金层520、导电凸块530、底部填充层U、粘合层540、和散热盖550。

如图6C所示,根据一些实施例,将线路基板110上下反转。如图6C所示,根据一些实施例,在导电粘合材料层610a上方形成掩模层620。根据一些实施例,掩模层620具有开口622。根据一些实施例,开口622露出在导电垫115b上方或附近的导电粘合材料层610a。根据一些实施例,掩模层620由如聚合物材料的光刻胶材料制成。

如图6C所示,根据一些实施例,在开口622中形成焊料层560a。根据一些实施例,焊料层560a形成在导电粘合材料层610a上方。根据一些实施例,焊料层560a与导电粘合材料层610a直接接触。

根据一些实施例,焊料层560a由合适的焊接材料制成,例如锡(Sn)或锡合金。根据一些实施例,使用镀层工艺来形成焊料层560a,例如电镀工艺。根据一些实施例,导电粘合材料层610a在电镀工艺中用作籽晶层。

如图6C至图6D所示,根据一些实施例,去除了掩模层620和掩模层620下方的导电粘合材料层610a。根据一些实施例,留在焊料层560a下方的导电粘合材料层610a形成了导电粘合层610。

如图6D所示,根据一些实施例,在焊料层560a上执行回焊工艺。根据一些实施例,回焊后的焊料层560a形成导电凸块560。根据一些实施例,导电凸块560具有球形的形状。

如图6D所示,根据一些实施例,沿着切割道A在线路基板110上执行切割工艺以切穿线路基板110,从而形成芯片封装结构600。

如图6E所示,根据一些实施例,芯片封装结构600通过导电凸块560接合至线路基板570。根据一些实施例,线路基板570包括绝缘层572、线路层574、导孔576、和导电垫578。

根据一些实施例,线路层574和导孔576位于绝缘层572中。根据一些实施例,导电垫578位于绝缘层572上。根据一些实施例,导孔576在线路层574之间提供电性连接,以及在线路层574和导电垫578之间提供电性连接。

根据一些实施例,线路层574、导孔576、和导电垫578由导电材料制成,例如金属材料或其合金。金属材料包括铝、铜或钨。

在此步骤中,根据一些实施例,实质上形成了芯片封装结构(或板级封装结构)601。根据一些实施例,芯片封装结构601包括了芯片封装结构600、导电凸块560以及线路基板570。

在一些实施例中,如图6A至图6D所示,通过沉积导电粘合材料层610a,并且去除掩模层620下的导电粘合材料层610a来形成导电粘合层610。在一些其他实施例中(例如图7A至图7B的实施例),通过沉积导电粘合材料层610a,并去除从掩模层露出的导电粘合材料层610a来形成导电粘合层610。

图7A至图7C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。如图7A所示,根据一些实施例,在图6B的步骤之后,将线路基板110上下翻转。如图7A所示,根据一些实施例,在导电垫115b上方或附近的导电粘合材料层610a上方形成掩模层710。根据一些实施例,掩模层710也被称为干膜。根据一些实施例,掩模层710由聚合物材料制成。

如图7A至图7B所示,根据一些实施例,去除了从掩模层710露出的导电粘合材料层610a。根据一些实施例,留在掩模层710下方的导电粘合材料层610a形成了导电粘合层610。如图7B所示,根据一些实施例,去除掩模层710。

此后,根据一些实施例,如图7C所示,在导电粘合层610上方形成导电凸块560。根据一些实施例,使用印刷工艺(类似于图3C的印刷工艺)或者球安装工艺(ball mountingprocess,类似于图4的球安装工艺)和回焊工艺来形成导电凸块560。

如图7C所示,根据一些实施例,沿着切割道A在线路基板110上执行切割工艺,以切穿线路基板110而形成芯片封装结构700。

图8A至图8D是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。如图8A所示,根据一些实施例,提供了线路基板110。如图8A所示,根据一些实施例,在聚合物层118a和导电垫115a上方形成材料层122a。

根据一些实施例,材料层122a共形地覆盖聚合物层118a的顶表面118a1、聚合物层118a的开口P1的内壁S、和导电垫115a的顶表面115a1。根据一些实施例,材料层122a与聚合物层118a和导电垫115a直接接触。

如图8A所示,根据一些实施例,在材料层122a上方形成材料层124a。根据一些实施例,材料层124a共形地覆盖材料层122a。根据一些实施例,材料层124a在开口P1中具有凹槽124a1。根据一些实施例,材料层122a和材料层124a由不同的材料制成。根据一些实施例,材料层122a由钛或钯制成。根据一些实施例,材料层124a由铜制成。

在一些实施例中,材料层122a由钛制成,材料层124a由铜制成,并且材料层122a和材料层124a使用溅镀工艺形成。在一些实施例中,材料层122a由钯制成,材料层124a由铜制成,并且材料层122a和材料层124a使用无电镀层工艺形成。根据一些实施例,材料层122a和材料层124a一起形成导电粘合材料层120a。

如图8B所示,根据一些实施例,在材料层124a上方形成掩模层810。根据一些实施例,掩模层810具有开口812,开口812露出在导电垫115a上方或附近的材料层124a。根据一些实施例,掩模层810由光刻胶材料制成,例如聚合物材料。

如图8B所示,根据一些实施例,在开口812和凹槽124a1中形成镍层820。根据一些实施例,镍层820填充在凹槽124a1中。根据一些实施例,镍层820比导电粘合材料层120a厚。换句话说,根据一些实施例,镍层820的厚度T3大于导电粘合材料层120a的厚度T4。根据一些实施例,厚度T3在大约3μm至大约30μm的范围之内。根据一些实施例,厚度T4在约0.5μm至约2μm的范围内。

镍层820可以在随后的高电流密度操作期间防止导电垫115a的铜迁移到随后形成在镍层820上方的导电凸块中。因此可以减少镍层820的电迁移(electromigration)问题。

根据一些实施例,镍层820由镍或其合金制成。根据一些实施例,材料层122a和材料层124a以及镍层820由不同的材料制成。根据一些实施例,使用镀层工艺来形成镍层820,例如无电镀层工艺。

如图8B所示,根据一些实施例,在镍层820上方形成钯层830。根据一些实施例,钯层830比镍层820薄。根据一些实施例,钯层830由钯或其合金制成。根据一些实施例,使用镀层工艺来形成钯层830,例如无电镀层工艺。

如图8B所示,根据一些实施例,在钯层830上方形成金层840。根据一些实施例,金层840比镍层820薄。根据一些实施例,金层840由金或其合金制成。根据一些实施例,使用镀层工艺来形成金层840,例如浸镀工艺(immersion plating process)。

如图8C所示,根据一些实施例,去除了掩模层810以及掩模层810下方的材料层122a和材料层124a。根据一些实施例,留在镍层820下方的材料层122a形成了导电层122。根据一些实施例,留在镍层820下方的材料层124a形成了导电层124。根据一些实施例,导电层122和导电层124一起形成导电粘合层120。

如图8C至图8D所示,根据一些实施例,执行图1D至图1E和图5A至图5B的步骤以形成在线路基板上方的晶片510、凸块下冶金层520、导电凸块530、底部填充层U、粘合层540、和散热盖550。根据一些实施例,在将芯片510接合到线路基板110上之后,钯层830和金层840被分散(或溶解)在导电凸块530中。根据一些实施例,导电凸块530与镍层820直接接触。

如图8D所示,根据一些实施例,执行图5C的步骤,以在导电垫115b上形成导电凸块560并形成芯片封装结构800。为了简单起见,根据一些实施例,图8D仅示出其中一个芯片封装结构800。

如图8D所示,根据一些实施例,执行图5D的步骤以通过导电凸块560将线路基板110接合到线路基板570。根据一些实施例,导电凸块560位于线路基板110的导电垫115b与线路基板570的导电垫578之间。

在此步骤中,根据一些实施例,实质上形成了芯片封装结构(或板级封装结构)801。根据一些实施例,芯片封装结构801包括芯片封装结构800、导电凸块560、和线路基板570。根据一些实施例,芯片封装结构801是球栅阵列(BGA)封装结构。

图9A至图9C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。如图9A所示,根据一些实施例,在图8A的步骤之后,在导电垫115a上方或附近的材料层124a上方形成掩模层910。根据一些实施例,掩模层910也被称为干膜。根据一些实施例,掩模层910由聚合物材料制成。

如图9A至图9B所示,根据一些实施例,去除未被掩模层910覆盖的材料层122a和材料层124a。根据一些实施例,留在掩模层910下方的材料层122a形成了导电层122。根据一些实施例,留在掩模层910下方的材料层124a形成了导电层124。根据一些实施例,导电层122和导电层124一起形成导电粘合层120。如图9B所示,根据一些实施例,去除掩模层910。

如图9B所示,根据一些实施例,在导电粘合层120上方形成镍层920。根据一些实施例,镍层920覆盖导电粘合层120的顶表面120a和侧壁120b。

根据一些实施例,镍层920比导电粘合层120厚。即,根据一些实施例,镍层920的厚度T5大于导电粘合层120的厚度T6。根据一些实施例,厚度T5在大约3μm至大约30μm的范围内。根据一些实施例,厚度T6在大约0.5μm至大约2μm的范围内。

根据一些实施例,镍层920由镍或其合金制成。根据一些实施例,使用镀层工艺来形成镍层920,例如使用无电镀层工艺。

如图9B所示,根据一些实施例,在镍层920上方形成钯层930。根据一些实施例,钯层930共形地覆盖镍层920的顶表面922和侧壁924。根据一些实施例,钯层930比镍层920薄。

根据一些实施例,钯层930由钯或其合金制成。根据一些实施例,使用镀层工艺来形成钯层930,例如使用无电镀层工艺。

如图9B所示,根据一些实施例,在钯层930上方形成金层940。根据一些实施例,金层940共形地覆盖钯层930的顶表面932和侧壁934。根据一些实施例,金层940比镍层920薄。根据一些实施例,金层940由金或其合金制成。根据一些实施例,使用镀层工艺来形成金层940,例如浸镀工艺。

如图9B至图9C所示,根据一些实施例,执行图5A至图5B的步骤以形成在线路基板110上方的芯片510、凸块下冶金层520、导电凸块530、底部填充层U、粘合层540、和散热盖550。根据一些实施例,在将芯片510接合到线路基板110之后,将钯层930和金层940溶解在导电凸块530中。

如图9C所示,根据一些实施例,执行图5C的步骤以在导电垫115b上形成导电凸块560并形成芯片封装结构900。为了简单起见,根据一些实施例,图9C仅示出其中一个芯片封装结构900。

如图9C所示,根据一些实施例,执行图5D的步骤,以通过导电凸块560将线路基板110接合到线路基板570。根据一些实施例,导电凸块560位于线路基板110的导电垫115b与线路基板570的导电垫578之间。

在此步骤中,根据一些实施例,实质上形成了芯片封装结构(或板级封装结构)901。根据一些实施例,芯片封装结构901包括芯片封装结构900、导电凸块560、和线路基板570。根据一些实施例,芯片封装结构901是球栅阵列(BGA)封装结构。

图10A至图10C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。如图10A所示,根据一些实施例,在图8A的步骤之后,在材料层124a上方形成掩模层1010。根据一些实施例,掩模层1010具有开口1012,开口1012露出在导电垫115a上方或附近的材料层124a。根据一些实施例,掩模层1010由光刻胶材料制成,例如聚合物材料。

如图10A所示,根据一些实施例,镍层1020形成在掩模层1010的开口1012和材料层124a的开口124a1中。根据一些实施例,镍层1020共形地覆盖材料层124a。根据一些实施例,镍层1020具有部分在凹槽124a1中的凹槽1022。

根据一些实施例,镍层1020比导电粘合材料层120a厚。根据一些实施例,镍层1020由镍或其合金制成。根据一些实施例,使用镀层工艺来形成镍层1020,例如无电镀层工艺。

如图10A所示,根据一些实施例,在镍层1020上方和在凹槽1022中形成铜层1030。根据一些实施例,铜层1030比镍层1020厚。根据一些实施例,铜层1030填充在凹槽1022中。根据一些实施例,铜层1030由铜或其合金制成。根据一些实施例,使用镀层工艺来形成铜层1030,例如无电镀层工艺。

如图10A至图10B所示,根据一些实施例,去除了掩模层1010以及掩模层1010下方的材料层122a和材料层124a。根据一些实施例,留在镍层1020下方的材料层122a形成了导电层122。根据一些实施例,留在镍层1020下方的材料层124a形成了导电层124。根据一些实施例,导电层122和导电层124一起形成导电粘合层120。

图10B所示,根据一些实施例,在铜层1030、镍层1020、和导电粘合层120上形成盖层1040。根据一些实施例,盖层1040共形地覆盖铜层1030的顶表面1032和侧壁1034、镍层1020的侧壁1022、导电层122的侧壁122b、和导电层124的侧壁124b。根据一些实施例,盖层1040用于防止铜层1030、镍层1020、和导电粘合层120被氧化。

根据一些实施例,盖层1040由不同于铜层1030、镍层1020、和导电粘合层120的材料制成。根据一些实施例,盖层1040由锡或有机材料制成。

根据一些实施例,有机材料包括有机保焊(organic solderabilitypreservative,OSP)材料。有机保焊材料包括苯并三唑(benzotriazole)、苯并咪唑(benzimidazoles)或其组合和衍生物。在一些实施例中,通过将铜层1030、镍层1020、和导电粘合层120的金属表面浸入有机保焊溶液中来形成盖层1040,有机保焊溶液可包含咪唑烷(alkylimidazole)、苯并三唑、松香(rosin)、松香酯(rosin esters)或苯并咪唑的化合物。在一些其他实施例中,盖层1040由包括2-芳基咪唑(2-arylimidazole)作为有效成分的苯基咪唑(phenylimidazole)或其他咪唑(imidazole)化合物制成。

如图10B至图10C所示,根据一些实施例,执行图5A至图5B的步骤以形成在线路基板110上的芯片510、凸块下冶金层520、导电凸块530、底部填充层U、粘合层540和散热盖550。根据一些实施例,导电凸块530位于铜层1030和晶片510之间。根据一些实施例,在将芯片510接合到线路基板110之后,将覆盖层1040溶解在导电凸块530中。

如图10C所示,根据一些实施例,执行图5C的步骤以在导电垫115b上形成导电凸块560并形成芯片封装结构1000。为了简单起见,根据一些实施例,图10C仅示出其中一个芯片封装结构1000。

如图10C所示,根据一些实施例,执行图5D的步骤以通过导电凸块560将线路基板110接合到线路基板570。根据一些实施例,导电凸块560位于线路基板110的导电垫115b与线路基板570的导电垫578之间。

在此步骤中,根据一些实施例,实质上形成了芯片封装结构(或板级封装结构)1001。根据一些实施例,芯片封装结构1001包括了芯片封装结构1000、导电凸块560以及线路基板570。根据一些实施例,芯片封装结构1001是球栅阵列(BGA)封装结构。

图11A至图11C是根据一些实施例的用于形成芯片封装结构的工艺的各个阶段的剖面图。如图11A所示,根据一些实施例,在图8A的步骤之后,在材料层124a上方形成掩模层1110。根据一些实施例,掩模层1110具有开口1112,开口1112露出在导电垫115a上方或附近的材料层124a。根据一些实施例,掩模层1110由光刻胶材料制成,例如聚合物材料。

如图11A所示,根据一些实施例,在掩模层1110的开口1112和材料层124a的开口124a1中形成镍层1120。根据一些实施例,镍层1120共形地覆盖材料层124a。根据一些实施例,镍层1120具有部分在凹槽124a1中的凹槽1122。

根据一些实施例,镍层1120比导电粘合材料层120a厚。根据一些实施例,镍层1120由镍或其合金制成。根据一些实施例,使用镀层工艺来形成镍层1120,例如无电镀层工艺。

如图11A所示,根据一些实施例,在镍层1120上方形成钯层1130。根据一些实施例,钯层1130比镍层1120薄。根据一些实施例,钯层1130由钯或其合金制成。根据一些实施例,使用镀层工艺来形成钯层1130,例如无电镀层工艺。

如图11A所示,根据一些实施例,在钯层1130上方形成金层1140。根据一些实施例,金层1140比镍层1120薄。根据一些实施例,金层1140由金或其合金制成。根据一些实施例,使用镀层工艺来形成金层1140,例如浸镀工艺。

如图11A所示,根据一些实施例,在开口1112中和金层1140上方形成焊料层1150a。根据一些实施例,焊料层1150a比镍层1120厚。根据一些实施例,焊料层1150a由锡或其合金制成。根据一些实施例,使用镀层工艺来形成焊料层1150a,例如电镀工艺或无电镀层工艺。

如图11A至图11B所示,根据一些实施例,去除了掩模层1110以及掩模层1110下方的材料层122a和材料层124a。根据一些实施例,留在镍层1120下方的材料层122a形成了导电层122。根据一些实施例,留在镍层1120下方的材料层124a形成了导电层124。根据一些实施例,导电层122和导电层124一起形成导电粘合层120。

如图11B所示,根据一些实施例,在焊料层1150a上执行回焊工艺。根据一些实施例,回焊的焊料层1150a形成焊球1150。金层1140和钯层1130溶解在焊球1150中。根据一些实施例,焊球1150与镍层1120直接接触。

如图11B至图11C所示,根据一些实施例,执行图5A至图5B的步骤以形成在线路基板110上的芯片510、凸块下冶金层520、导电凸块530、底部填充层U,粘合层540、散热盖550。根据一些实施例,导电凸块530位于镍层1120和凸块下冶金层520之间。导电凸块530的一部分由焊球1150形成。

如图11C所示,根据一些实施例,执行图5C的步骤以在导电垫115b上形成导电凸块560并形成晶片封装结构1100。为了简单起见,根据一些实施例,图11C仅示出其中一个芯片封装结构1100。

如图11C所示,根据一些实施例,执行图5D的步骤以通过导电凸块560将线路基板110接合到线路基板570。根据一些实施例,导电凸块560位于线路基板110的导电垫115b与线路基板570的导电垫578之间。

在此步骤中,根据一些实施例,实质上形成了芯片封装结构(或板级封装结构)1101。根据一些实施例,芯片封装结构1101包括了芯片封装结构1100、导电凸块560以及线路基板570。根据一些实施例,芯片封装结构1101是球栅阵列(BGA)封装结构。

用于形成芯片封装结构600、700、800、900、1000和1100的工艺和材料可以与用于形成上述芯片封装结构500的工艺或材料类似或相同。用于形成芯片封装结构601、801、901、1001和1101的工艺和材料可以与用于形成上述芯片封装结构501的工艺和材料类似或相同。图1A至图11C中使用相同的标号表示的元件具有类似或相同的结构和材料,从而不再赘述。

根据一些实施例,提供了芯片封装结构及其形成方法。此方法(用于形成芯片封装结构的方法)在线路基板和导电凸块之间形成导电粘合层,以改善在导电凸块和线路基板的聚合物层之间以及在导电凸块和线路基板的导电垫之间的黏附性。此方法在导电粘合层和导电凸块之间形成镍层。镍层可防止在高电流密度操作期间导电垫的材料迁移到导电凸块中。因此,镍层减少了电迁移的问题。

本公开实施例提供一种用于形成芯片封装结构的方法,包括提供线路基板、在聚合物层以及导电垫上方形成导电粘合层、在导电粘合层上方形成镍层以及将芯片通过导电凸块接合到线路基板。线路基板包括基板、导电垫以及聚合物层,聚合物层位于基板以及导电垫上方,且聚合物层具有露出导电垫的一第一开口。导电粘合层直接接触并共形地覆盖聚合物层以及导电垫。镍层比导电粘合层厚,且镍层以及导电粘合层由不同的材料所形成。导电凸块位于镍层以及芯片之间。

在一些实施例中,在将芯片接合到线路基板的操作之前,在镍层上方形成金层,在将芯片接合到线路基板之后,金层溶解在导电凸块中。在一些实施例中,形成导电粘合层、镍层以及金层的操作包括:在聚合物层以及导电垫上方形成导电粘合材料层;在导电粘合材料层上方形成掩模层,其中掩模层具有第二开口,第二开口露出在导电垫上方或附近的导电粘合材料层;在第二开口中形成镍层;在镍层上方形成金层;以及去除掩模层以及掩模层下方的导电粘合材料层,留在镍层下方的导电粘合材料层形成导电粘合层。在一些实施例中,形成导电粘合层的操作包括:在聚合物层以及导电垫上方形成导电粘合材料层;在导电垫上方或附近的导电粘合材料层上方形成掩模层;去除从掩模层露出的导电粘合材料层,其中留在掩模层下方的导电粘合材料层形成导电粘合层;以及去除掩模层。在一些实施例中,金层覆盖镍层的侧壁以及顶表面。在一些实施例中,在镍层上方形成金层的操作之后,在镍层上方形成焊球,其中金层溶解在焊球中,且导电凸块的一部分从焊球形成。在一些实施例中,在将芯片接合到线路基板的操作之前,在镍层上方形成铜层,其中导电凸块位于铜层以及芯片之间。在一些实施例中,镍层共形地覆盖导电粘合层,且镍层具有凹槽,凹槽部分地位于第一开口中,且铜层填充凹槽。在一些实施例中,形成盖层,盖层覆盖铜层的顶表面以及第一侧壁、镍层的第二侧壁以及导电粘合层的第三侧壁。在一些实施例中,盖层由锡或者有机材料所形成。

本公开一些实施例提供一种用于形成芯片封装结构的方法,包括提供线路基板,线路基板包括基板、第一导电垫以及第一聚合物层,第一导电垫位于基板的第一表面上方,第一聚合物层位于第一表面以及第一导电垫上方,第一聚合物层具有第一开口,第一开口露出第一导电垫;在第一聚合物层以及第一导电垫上方形成第一导电粘合层,第一导电粘合层直接接触第一聚合物层以及第一导电垫;在第一导电粘合层上方形成焊料结构;以及通过下凸块冶金层以及第一导电凸块将芯片接合到线路基板,下凸块冶金层位于芯片以及第一导电凸块之间,导电凸块连接到第一导电粘合层以及下凸块冶金层,焊料结构形成一部分的第一导电凸块,且下凸块冶金层的第一厚度实质上等于第一导电粘合材料层的第二厚度。

在一些实施例中,形成第一导电粘合层以及焊料结构的操作包括:在第一聚合物层以及第一导电垫上方形成导电粘合材料层;在导电粘合材料层上方形成掩模层,其中掩模层具有第二开口,第二开口露出邻近或位于第一导电垫上方的导电粘合材料层;在第二开口中形成焊料层;去除掩模层以及位于掩模层下方的导电粘合材料层,其中留在焊料层下方的导电粘合材料层形成第一导电粘合层;以及回焊焊料层以形成焊料结构。在一些实施例中,形成第一导电粘合材料层的操作包括:在第一聚合物层以及第一导电垫上方形成导电粘合材料层;在第一导电垫附近或上方的导电粘合材料层上方形成第一掩模层;去除从第一掩模层露出的导电粘合材料,其中留在第一掩模层下方的导电粘合材料形成第一导电粘合层;以及去除第一掩模层。在一些实施例中,于第一导电粘合层上方形成焊料结构的操作包括:在第一聚合物层上方形成一第二掩模层,其中第二掩模层具有露出第一导电粘合层的第二开口;将一焊料层印刷到第二开口中;去除第二掩模层;以及回焊焊料层以形成焊料结构。在一些实施例中,在第一导电粘合层上方形成焊料结构的操作包括:将焊球设置在第一导电粘合层上方;以及回焊焊球以形成焊料结构。在一些实施例中,在焊料结构上方进行热压工艺,以平坦化焊料结构的顶表面。在一些实施例中,第一导电粘合层通过无电镀层工艺或溅镀工艺所形成。在一些实施例中,线路基板还包括第二导电垫以及第二聚合物层,第二导电垫位于基板的第二表面上方,第一导电垫比第二导电垫窄,第二聚合物层位于第二表面以及第二导电垫上方,且第二聚合物层具有露出第二导电垫的一第二开口,且用于形成芯片封装结构的方法还包括:在第一聚合物层以及第一导电垫上方形成第一导电粘合层时,在第二聚合物层以及第二导电垫上方形成第二导电粘合层;以及在将芯片接合到线路基板之后,在第二导电粘合层上方形成第二导电凸块。

本公开一些实施例提供一种芯片封装结构,包括线路基板、导电粘合层、镍层、芯片以及导电凸块。线路基板包括基板、第一导电垫、第二导电垫以及聚合物层,第一导电垫以及第二导电垫分别位于基板的第一表面以及第二表面上方,第一导电垫比第二导电垫窄,且聚合物层位于第一表面以及第一导电垫上方。导电粘合层穿过聚合物层且位于第一导电垫上方,其中导电粘合层直接接触聚合物层以及第一导电垫。镍层位于导电粘合层上方,其中镍层比导电粘合层厚,且镍层以及导电粘合层由不同的材料形成。芯片位于线路基板上方。导电凸块位于镍层以及芯片之间。

在一些实施例中,镍层覆盖导电粘合层的侧壁以及顶表面。

上述内容概述许多实施例的特征,因此本领域技术人员可更加理解本公开的各面向。本领域技术人员可能无困难地以本公开为基础,设计或修改其他工艺及结构,以达到与本公开实施例相同的目的及/或得到相同的优点。任何所属技术领域中技术人员也应了解,在不脱离本公开的精神和范围内做不同改变、代替及修改,如此等效的创造并没有超出本公开的精神及范围。

- 芯片封装结构及芯片封装结构及其形成方法

- 芯片封装结构和芯片封装结构的制备方法