存储器器件以及形成存储器结构的方法

文献发布时间:2024-01-17 01:27:33

技术领域

本申请的实施例涉及半导体技术领域,更具体地,涉及存储器器件以及形成存储器结构的方法。

背景技术

半导体存储器用于电子应用的集成电路,包括例如收音机、电视、手机和个人计算设备。半导体存储器的一种类型是相变随机存取存储器(PCRAM,phase-change randomaccess memory),其涉及在相变材料(诸如硫属材料)中储存数值。相变材料可以在非晶相(具有高电阻率)和结晶相(具有低电阻率)之间切换,以指示位代码。PCRAM单元通常包括两个电极之间的相变材料(PCM,phase change material)元件。

发明内容

根据本申请的实施例的一个方面,提供了一种形成存储器结构的方法,包括:形成存储器单元的存储器结构,存储器结构插入在上电极和下电极之间;形成存储器单元的选择器结构,选择器结构插入在上电极和下电极之间,选择器结构包括设置在第一层中的第一材料和设置在第二层中的第二材料,第一材料包括第二材料和附加元素,第一材料包括双向阈值开关材料;以及在选择器结构上方形成字线,字线的纵长方向垂直于位线的纵长方向,位线设置在选择器结构下方。

根据本申请的实施例的另一个方面,提供了.一种形成存储器结构的方法,包括:形成位线金属;沉积底部电极金属;在底部电极金属上方沉积存储器层;在底部电极金属上方沉积选择器层;在选择器层上方沉积顶部电极金属;在顶部电极金属上方形成第一掩模,并且将顶部电极金属、选择器层、存储器层和底部电极金属图案化为与位线金属对应的条带的集合;沉积横向围绕条带的集合的绝缘层;在绝缘层和顶部电极金属上方形成字线金属;在字线金属上方形成第二掩模;以及图案化字线金属,并且使用第二掩模将顶部电极金属、选择器层、存储器层和底部电极金属图案化为柱的集合,每个柱对应于存储器单元。

根据本申请的实施例的又一个方面,提供了一种存储器器件,包括:存储储器结构,选择器结构,选择器结构包括第一材料层和第二材料层,其中第二材料层包括来自第一材料层的材料的子集,顶部电极,和底部电极,存储器结构和选择器结构插入在顶部电极和底部电极之间;位线,耦合到底部电极;以及源极线,耦合到顶部电极。

附图说明

当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应该强调,根据工业中的标准实践,各个部件未按比例绘制并且仅用于说明的目的。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

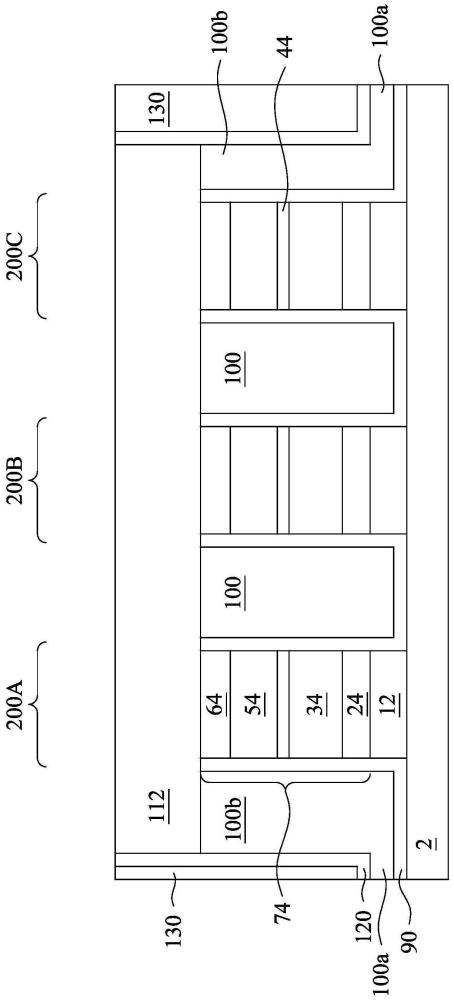

图1示出了根据一些实施例的存储器阵列中的交叉点或交叉条存储器单元的阵列的透视图。

图2A示出了根据一些实施例的存储器单元的简图。

图2B示出了根据一些实施例的选择器切换结构的特征。

图3示出了根据一些实施例的存储器阵列的电路示意图。

图4A、图4B、图4C和图4D示出了根据一些实施例的存储器单元的各种配置。

图5A、图5B、图5C和图5D示出了根据一些实施例的存储器单元的存储器元件的各种配置。

图6、图7、图9、图11、图13、图15、图17、图19、图21、图23、图25提供了根据一些实施例的形成存储器阵列的中间视图。

图8A至图8D、图10A至图10B、图12A至图12B、图14A至图14B、图16A至图16B、图18A至图18B、图20A至图20B、图22A至图22B、图24A至图24B提供了根据一些实施例的形成存储器阵列的中间视图。

图26A和图26B以及图30A、图30B、图31A和图31B提供了根据一些实施例的形成存储器阵列的中间视图。

图27A和图27B示出了根据一些实施例的各种配置。

图28和图29示出了根据一些实施例的浓度曲线图。

具体实施方式

以下公开内容提供了许多用于实现本发明的不同特征不同的实施例或实例。下面描述了组件和布置的具体实施例或实例以简化本发明。当然,这些仅是实例而不旨在限制。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可以在各个示例中重复参考数字和/或字母。该重复是为了简单和清楚的目的,并且其本身不指示讨论的各个实施例和/或配置之间的关系。

此外,为了便于描述,本文中可以使用诸如“在…下方”、“在…下面”、“下部”、“在…上面”、“上部”等的间隔关系术语,以描述如图中所示的一个元件或部件与另一元件或部件的关系。除了图中所示的方位外,间隔关系术语旨在包括器件在使用或操作工艺中的不同方位。装置可以以其它方式定位(旋转90度或在其它方位),并且在本文中使用的间隔关系描述符可以同样地作相应地解释。

实施例利用具有多层的存储器单元的选择器层结构。切换材料的浓度百分比从外向内逐渐增加,从而导致更好的切换性能。切换层和附近金属层之间的干扰较小。此外,改进的切换性能包括比单层选择器结构更灵敏的开/关切换曲线图,以及更小的周期至周期V

图1示出了根据一些实施例的存储器阵列300中的交叉点或交叉条存储器单元200的阵列的透视图。存储器阵列300包括以“交叉点”配置连接的位线12、字线112和存储器单元200,其中特定的位线12和特定的字线112的寻址一起选择特定的存储器单元200。在一些实施例中,可以堆叠存储器阵列300以创建3D存储器阵列(未示出)。存储器阵列300可以形成在衬底上(例如,见图6的衬底2),衬底可以是半导体衬底或其他类型的衬底。在一些实施例中,衬底可以包括有源器件和/或无源器件(例如晶体管、二极管、电容器、电阻器等)。器件可以根据适用的制造工艺来形成。在一些实施例中,衬底中未形成任何器件。在一些实施例中,存储器阵列300形成在衬底上方的互连结构的金属化层中。存储器阵列300可以电连接到一个或多个金属化层。例如,在一些实施例中,字线112和/或位线12可以是金属化层的导电线。

在图1所示的实施例中,每个存储器单元200包括底部电极24、存储器储存结构34、中间层44、选择器结构54和顶部电极64。顶部电极64和底部电极24之间的元件,例如包括存储器储存结构34、中间层44和选择器层54,可以被称为存储器元件76。位线12电连接到存储器阵列300中的存储器单元200的对应列的底部电极24。存储器阵列300的每个列具有相关联的位线12(例如,位线12A、12B或12C),并且列中的存储器单元200连接到该列的相同位线12。字线112连接到存储器阵列300中的对应行的存储器单元200的顶部电极64。存储器阵列300的每个行具有相关联的字线112(例如,字线112A、112B、112C),并且行中的存储器单元200连接到该行的字线112。以此方式,可以通过字线112和位线12的适当组合来选择存储器阵列300的每个存储器单元200。例如,可以通过存取连接到存储器单元200B的单个字线112B以及也存取连接到存储器单元200的单个位线12B,来选择(例如,用于读取或写入操作)特定的存储器单元200B。图1中具体标记的其他存储器单元包括存储器单元200A、200C、200D和200E,它们沿着在一些后续附图中用作截面参考线的参考线A-A(200A、2001B、200C)和B-B(200D、200B、200E)。

在一些实施例中,每个存储器单元200的存储器储存结构34的电阻是可编程的,并且可以在高电阻状态和低电阻状态之间变化,这可以对应于二进制代码的两种状态。存储器储存结构34可以使用任何合适的技术,本发明不应局限于任何特定类型的存储器存储技术。例如,存储器储存结构34可以包括用于PCRAM(相变随机存取存储器)器件的相变材料(PCM)、用于RRAM(resistive random access memory,电阻随机存取存储器)器件的两态电阻材料、用于MRAM(magnetic random access memory,磁随机存取存储器)器件的磁隧道结(magnetic tunnel junction,MTJ)。也可以使用其他存储器类型。

在一些实施例中,可以通过跨存储器单元200施加适当的电压脉冲而产生跨存储器储存结构34的对应电流脉冲,来编程(例如,“写入”)存储器单元200的存储器储存结构34的电阻状态。改变存储器储存结构34的电阻状态所需的电流是特定设计。由于存储器单元200的电阻的较大百分比是由存储器储存结构34提供的,因此实现的电流脉冲取决于存储器储存结构34的电阻率。例如,在一些实施例中,编程电流脉冲的幅度可以在约50μA到约800μA的范围内,尽管可能存在其他电流。施加的编程电压还取决于存储器储存结构34。例如,特定存储器单元200的读取可能是正向偏置的,而写入可能是反向偏置的,反之亦然。在一些情况下,编程电压脉冲的幅度可以在约1V至约2V的范围内,但也可能存在其他电压。在一些实施例中,可以通过跨存储器单元200施加相对小的电流来测量存储器单元200的电阻而不会扰乱存储器储存结构34的电阻态,从而读取存储器单元200的状态。其他类型的存储器或存储器结构可以使用与本示例不同的读取方案或幅度。

每个存储器单元200的选择器结构54用作选择器,其允许单独存取(例如,写入或读取)对应的存储器单元200。以此方式,存储器单元200的选择器结构54在本文中也可以称为“选择器54”。选择器结构54可以利用双向阈值开关(OTS,ovonic threshold switching)或其变体,诸如混合离子电子传导(MIEC,mixed-ionic-electronic conduction)等。为简单起见,所有此类变体也将称为OTS。

参考图2A和图2B,OTS选择器材料具有称为阈值电压(V

图2A示出了诸如如图1所示的存储器阵列300的简图。图2A中的存储器阵列300包括位线12,标记为BL

图2B中模拟了上述选择器结构54的行为。参考电压V

在一些实施例中,阈值电压V

图3示出了存储器阵列300的电路示意图。为了清晰起见,已删除了一些元件。位线驱动器控制到达各种导电位线12的电压信号,并且字线驱动器控制到达各种导电字线112的电压信号。存储器单元200包括存储器储存结构34和选择器结构54。它们可以是任意顺序。当提供参考电压以激活存储器单元200时,在读取操作中,可以读取产生的电流响应,以确定值是“1”还是“0”。写入操作可以取决于所使用的存储器储存结构34的类型。例如,在一些实施例中,可以施加较大的偏压,而在其他实施例中可以施加反向偏压。

图4A、图4B、图4C和图4D示出了存储器单元200的各种配置。各种配置是来自用于形成柱的图案化工艺,其中柱对应于与存储器单元200。在图4A中,存储器单元200具有类似于矩形棱柱的形状。在一些实施例中,转角可以是圆弧的,在其他实施例中可以是相对方形的。在图4B中,存储器单元200具有圆柱形。在图4C中,存储器单元200具有金字塔形。在图4D中,存储器单元200具有锥形。可以通过沉积如图7所示的存储器单元的每个层,并通过掩模使用可接受的光刻工艺图案化存储器单元200,来实现图4A、图4B、图4C和图4D中的存储器单元200的这些形状。在这些实施例中,在沉积存储器单元200的层之前形成并且分离位线12,再次使用可接受的光刻工艺和沉积技术。在对存储器单元200进行图案化之后,可以沉积包括衬垫层在内的周围介电层,以横向环绕存储器单元200,然后形成并图案化字线112。图4A和图4C中的存储器单元200可以由下面图6至图21中描述的过程形成,蚀刻工艺可能导致例如存储器单元200的侧壁成斜角(如图4C中所示)或成竖直(如图4A中所示)。

图5A、图5B、图5C和图5D示出了存储器元件76的各种配置。应该理解的是,在下面讨论的实施例中可以使用这些配置中的每个。具体的,为了说明目的,即使图5A中所示的存储器元件76的布局在其余附图中使用,但也可以替换图5A、图5B、图5C和图5D中所示的任何布局。还应理解,也可以使用未具体示出的这些的变体。例如,存储器储存结构34、中间层44和选择器结构54中的每个构成以串联形式排列的电阻元件。因此,每个单元(如果使用)的顺序不会显著影响存储器单元200的操作和本公开中讨论的原理。图5A示出了存储器储存结构34形成在存储器元件76的底部处,选择器结构54形成在存储器单元76的顶部处,中间层44插入在两者之间。图5B示出了存储器储存结构34形成在存储器元件76的底部处,中间层44形成在存储器单元76的顶部处,选择器结构54插入在两者之间。图5C和图5D省略了中间层44。在图5C中,存储器储存结构34形成在存储器元件76的底部处,选择器结构54形成在存储器单元76的顶部处。在图5D中,这些被反转,使得选择器结构54形成在存储器元件76的底部处,并且存储器储存结构34形成在存储器单元76的顶部处。

根据一些实施例,图6至图26B和图30A至图31B提供了存储器阵列300形成的中间视图。图6、图9、图11、图13、图15分别示出了形成存储器阵列300的中间过程的三维视图。为了清晰起见,省略或简化了一些部件。这些视图中的每个提供了参考截面线A-A和B-B,它们对应于上面关于图1提供的截面线。除非另有说明,以A结尾的图沿着A-A参考线,以B结尾的图则沿着B-B参考线。

图6和图7示出了存储器阵列300的层的形成,这些层随后将被图案化为存储器单元200。在本实例中,图7示出的截面视图适用于图6的参考截面A-A和B-B。

提供衬底2。衬底2可以是多个层中的任何一层或层的组合,这取决于存储器阵列的形成位置。如上所述,例如,存储器阵列可以形成在互连结构中。在这样的实施例中,衬底2可以是半导体衬底与其中器件的组合或者不具有形成在其中的器件,且具有形成在其上的任何数量的金属化层。在一些实施例中,衬底2可以包括半导体材料,诸如硅、硅锗等。在一些实施例中,衬底2包括晶体半导体衬底,诸如晶体硅衬底、晶体硅碳衬底、晶体硅锗衬底、III-V族化合物半导体衬底等。在一个实施例中,衬底2可以包括掺杂或未掺杂的体硅,或者绝缘体上硅(SOI)衬底的有源层。通常,SOI衬底包括半导体材料层,诸如硅、锗、硅锗或其组合,例如绝缘体上的硅锗(SGOI)。可使用的其他衬底包括多层衬底、梯度衬底或混合晶向衬底。

在其他实施例中,衬底2可以是载体衬底,诸如玻璃载体、陶瓷载体等,并且存储器阵列300形成在载体衬底上。

在衬底2上方形成位线层10。衬底2和位线层10之间可以形成任意数量的中间层和结构,例如包括位线层10位于其上部金属化层处的互连件。在一些实施例中,这样的中间层可以包括有源器件和/或无源器件。

位线层10可以由任何合适的导电材料形成。在一些实施例中,例如,位线层10可以由铜、金、铝、钌、镍、钴、钛、钨、氮化钛、钽、氮化钽等及其组合形成。在一些实施例中,位线层10可以由多个离散的层构成。位线层10可以使用任何合适的工艺来形成,诸如通过物理气相沉积(PVD)、化学气相淀积(CVD)、镀覆、原子层沉积(ALD)、溅射等。尽管位线层10被示为毯式沉积,但位线层10可以使用其他工艺形成,诸如镶嵌、双镶嵌或其他合适的工艺。

底部电极层20沉积在位线层10上方。底部电极层20可以使用与位线层10不同或相同的材料、并使用类似的工艺形成。在随后的工艺中,底部电极层20将被图案化为存储器单元200的底部电极。

接下来,在底部电极层20上方,形成存储器堆叠层70。这些层将在随后的工艺中被图案化为存储器单元200的柱74。然而,为了讨论图6和图7,存储器堆叠层70显示为包括存储器结构层30、界面层40和选择器结构层50,应该理解,这些层的顺序和/或存在可能取决于所使用的具体实现。例如,如以上关于图5A、图5B、图5C和图5D所讨论的那样,图5A、图5B、图5C和图5D示出了将存储器堆叠层70图案化为柱74之后,相应的存储器储存结构34、中间层44和选择器结构54可以以不同的顺序布置,在一些实施例中,中间层44可以省略。为了简单起见,仅显示图5A中的配置,但可以随时替换其他配置。

存储器结构层30可以包括任何适于所使用的存储器技术的层。例如,如果存储器技术是PCRAM,则存储器结构层30可以包括阻挡层和硫属化合物材料层。如果存储器技术是MRAM,则存储器结构可以包括自由层、参考层和用于切换自由层的MRAM磁矩的钉扎层。可酌情使用这些或其他存储器技术的其他层。这些层的形成可以使用适合于这些层的工艺来进行,诸如PVD、ALD、CVD、旋涂等。

中间层40形成在存储器结构层30上。中间层40可以使用与底部电极层20的材料或技术类似的材料或技术形成。选择器结构层50形成在中间层40上。以下关于图8A、图8B、图8C和图8D进一步详细讨论了选择器结构层50的形成和材料。

在形成选择器结构层50之后,形成顶部电极层60。可以使用类似于形成底部电极层20的工艺和材料来形成顶部电极层60。

图8A、图8B、图8C和图8D示出了选择器结构层50的各种配置,这些结构层随后被图案化为选择器结构54。如图8A、图8B、图8C和图8D所示,选择器结构层50的每个配置包括至少两个层,包括第一双向阈值开关(OTS)材料层55和第二OTS材料层57。图8A示出了夹在两个第二OTS材料层57之间的第一OTS材料层55。在图8A中,两个第二OTS材料层57由相同的材料组成。图8B示出了夹在第二OTS材料层57和第三OTS材料层59之间的第一OTS材料层55。图8C和图8D分别包括第一OTS材料层55和仅一个第二OTS材料层57,其中第二OTS/材料层57位于第一OTS材料层55的上方(图8C)或下方(图8D)。

利用双层或夹层选择器结构可在多个层之间提供梯度成分曲线图,从而提供更稳定的器件性能。单层OTS材料层可以具有大的周期至周期以及器件至器件V

第一OTS材料层55可以由合金或任何合适的双向材料组成,诸如SiGeCTe、NSiGeCTe、NSnZnTe、SiSnTe、SiZnTe和NSiZnSnTe等,或其组合。第二OTS材料层57(和第三OTS材料层59,如果使用)可以由合金或任何合适的双向材料组成,诸如CTe、GeCTe、SiCTe、ZnTe和SnTe等,或其组合。应该理解,列出的OTS材料中的每个都考虑了列出的元素中的每个的合适和适用的比率,并且不意在代表特定的比率。

在一些实施例中,第二OTS材料层57(和/或第三OTS材料层59,如果使用)可以包括第一OTS材料层55中使用的材料的子集。例如,如果第二OTS材料层57或第三OTS材料层59是CTe,则第一OTS材料层55可以是GeCTe、SiGeCTe或NSiGeCTe。如果第二OTS材料层57或第三OTS材料层59是GCTe,则第一OTS材料层55可以是SiGeCTe或NSiGeCTe。如果第二OTS材料层57或第三OTS材料层59是SiCTe,则第一OTS材料层55可以是SiGeCTe或NSiGeCTe。如果第二OTS材料层57或第三OTS材料层59是ZnTe,则第一OTS材料层55可以是NSnZnTe、SiZnTe/或NSiZnSnTe。如果第二OTS材料层57或第三OTS材料层59是SnTe,则第一OTS材料层55可以是NSnZnTe、SiSnTe-或NSiZnSnTe。

在同时利用第二OTS材料层57和第三OTS材料层59二者的实施例中,它们都可以是第一OTS材料层55的子集,或者至少一个可以是第一OTS材料层55的子集。例如,在第二和第三OTS材料层57和59都是第一OTS材料层55的子集的实施例中,如果第一OTS材料层55是NSiGeCTe或SiGeCTe,则第二OTS材料层57和第三OTS材料层59可以是GeCTe、CTe或SiCTe中的一个。如果第一OTS材料层55是NSnZnTe、SiZnTe、NSiZnSnTe,则第二OTS材料层57和第三OTS材料层59可以是ZnTe_或SnTe。在第二或第三OTS材料层57或59中只有一个是第一OTS材料层55的子集、而另一个允许有一个或多个附加元素的实施例中,如果第一OTS材料层55是NSiGeCTe或SiGeCTe,则第二OTS材料层57或第三OTS料料层59中的一个可以是ZnTe、SnTe,GeCTe、CTe或SiCTe,另一个可以是GeCTe,CTe或SiCTe。如果第一OTS材料层55是NSnZnTe、SiZnTe、NSiZnSnTe,则第二OTS材料层57或第三OTS材料层59中的一个可以是ZnTe、SnTe、GeCTe、CTe或SiCTe并且另一个可以是ZnTe或SnTe。如果第一OTS材料层55是SiSnTe,则第二OTS材料层57或第三OTS材料层59中的一个可以是ZnTe、SnTe、GeCTe、CTe或SiCTe,并且另一个可以是SnTe。在一些实施例中,第二OTS材料层57和第三OTS材料层59都可以具有在第一OTS材料层55中未出现的附加元素。

第一OTS材料层55、第二OTS材料层57和第三OTS材料层59(如果使用)可以使用任何合适的技术并按照其形成的顺序进行沉积(例如,见图8A、图8B、图8C和图8D)。例如,可以使用合适的沉积工艺沉积这些层,诸如PVD、CVD、等离子体增强CVD(PECVD)、ALD等。

第一OTS材料层55可以沉积至约5nm至15nm之间的厚度。第二OTS材料层57可以沉积至约2.5nm至5nm之间的厚度。当在第一OTS材料层55的任一侧使用第二OTS材料层57的两层时,如图8A所示,则这两层可以具有相同的厚度,也可以具有不同的厚度。如图8B所示,第三OTS材料层59可以沉积至约2.5nm至5nm之间的厚度。在图8B中,第二OTS材料层57的厚度和第三OTS材料层59的厚度可以相同,也可以不同。

在图9、图10A和图10B中,在存储器堆叠层70上方形成硬掩模层84。硬掩模层84可由任何合适的材料形成,诸如掺杂或未掺杂的氧化硅、氮化硅、氧氮化硅、碳化硅、掺杂硅酸盐玻璃、可流动氧化物、其他高k材料、低k材料等,或其组合。硬掩模层84可以使用任何合适的工艺形成,诸如通过可流动CVD、旋涂、PVD等。在形成硬掩模层84后,在硬掩模层84上方沉积光掩模88,并使用可接受的光图案化技术来图案化光掩模88。

在图11、图12A和图12B中,光掩模88的图案用于图案化硬掩模层84,从而形成硬掩模86。然后,硬掩模86用作掩模,以依次蚀刻存储器堆叠层70的每个层,然后蚀刻位线层10。用于蚀刻每个层的蚀刻工艺可以使用适合于每个层的材料的蚀刻技术。例如,在一些实施例中,使用合适的蚀刻剂的干蚀刻可用于蚀刻每个层。在其他实施例中,可以使用反应离子蚀刻。在其他实施例中,使用合适的蚀刻剂的湿蚀刻可以被使用。在其他实施例中,使用蚀刻技术的组合。作为蚀刻的结果,位线层10变为位线12,底部电极层20变为底部电极层22,存储器结构层30变为存储器结构层32,界面层40变为界面层42,选择器结构层50变为选择器层52,顶部电极层60变为顶部电极层62,存储器堆叠层70一起被变为存储器堆叠层72。在存储器堆叠层70的图案化之后,部分地蚀刻存储器单元200,并根据存储器单元200对齐的行而分离成行。

在图13、图14A和图14B中,保护层90可以在图案化的存储器堆叠层72上方共形地形成,并且介电填充物100则横向围绕并密封存储器堆叠层72。保护层90可以包括任何合适的绝缘材料。在一些实施例中,保护层90可以包括极低k材料,例如k值低于约4.0。在一些实施例中,保护层90可以包括多层结构,多层结构包括极低k材料和有助于保护低k材料的覆盖层。例如,在一些实施例中,低k材料可以包括氧碳氮化硅或氧氮化硅,而覆盖层可以包括碳化硅或氮化硅。这些仅仅是示例;可以改用其他合适的材料。介电填充物100可以使用任何合适的绝缘材料通过任何合适的工艺形成。在一些实施例中,介电填充物100可以是氧化硅或绝缘聚合物。介电填充物100可以使用任何合适的工艺形成,诸如通过旋涂、CVD、PVD等或其组合。当介电填充物100包括氧化硅时,也可以通过正硅酸乙酯(TEOS)沉积工艺形成介电填充物100。

在图15、图16A和图16B中,使用平坦化工艺,诸如化学机械抛光(CMP)工艺,使介电填充物100的上表面与顶部电极层62的上表面齐平。

在图17、图18A和图18B中,字线层110可以毯式沉积在介电填充物100和存储器堆叠层72上方。可以使用类似于形成位线层10的工艺和材料来形成字线层110。

在图19、图20A和图20B中,在字线层110上方形成硬掩模层114。硬掩模层114可以使用与以上关于硬掩模层84所描述类似的工艺和材料形成。在形成硬掩模层114之后,在硬掩模层114上方沉积光掩模118,并使用可接受的光图案化技术图案化光掩模118。

在图21、图22A和图22B中,光掩模118的图案用于图案化硬掩模层114,从而形成硬掩模116。然后将硬掩模116用作掩模,依次蚀刻字线层110和存储器堆叠层72的每个层。用于蚀刻每个层的蚀刻工艺可以使用适合于每个层材料的蚀刻技术。例如,在一些实施例中,使用合适的蚀刻剂的干蚀刻用于蚀刻每个层。在其他实施例中,可以使用反应离子蚀刻。在其他实施例中,使用合适的蚀刻剂的湿蚀刻可以被使用。在其他实施例中,使用蚀刻技术的组合。作为蚀刻的结果,字线层110变为字线112,顶部电极层62变为顶部电极64,选择器层52变为选择器结构54,界面层42变为界面层44,存储器结构层32变为存储器储存结构34,底部电极层24变为底部电极24,存储器堆叠层72一起变为柱74。在柱74的图案化之后,存储器单元200已完成蚀刻。当形成位线12时,存储器单元200被分离成行,当蚀刻字线112时,存储器单元200进一步被分离成列,从而形成完整的存储器单元200,其中存储器单元200包括插入在顶部电极64和底部电极22之间的存储器元件76(见图4A、图4B、图4C和图4D)。

在一些实施例中,可以通过图21、图22A和图22B中的蚀刻工艺完全去除介电填充物100的暴露区域,以形成介电填充物100b,但是在一些实施例中,在蚀刻工艺之后,介电填充物100的剩余部分100a可能会留下,剩余部分100a的上表面大致与位线12的上表面对齐。

在图23、图24A和图24B中,保护层120可以共形地形成在图案化的柱74上方,并且沉积的介电填充物130横向围绕并密封柱74。保护层120可以使用与形成保护层90类似的工艺和材料形成,并且介电填充物130可以使用与形成介电填充物100的工艺和材料类似的工艺和材料来形成。

在图案化和形成保护层120之后,每个柱74由保护层90和保护层120的组合横向密封。此外,每个柱74由介电填充物100和介电填充物130的组合横向密封。

在图25、图26A和图26B中,使用诸如化学机械抛光(CMP)工艺的平坦化工艺使介电填充物130的上表面与字线112的上表面齐平。因此,形成了存储器单元200,例如包括存储器单元200A、200B、200C、200D和200E,诸如如图25、图26A和图26B所示。

应该理解,可以使用其他工艺来形成存储器单元。例如,位线12可以形成在介电层(例如,100a)内,位线12与介电层齐平。然后,形成每个存储器堆叠层70。然后,可以对存储器堆叠层70中的每个层进行图案化,以形成柱74。柱74然后可以由保护层覆盖,诸如保护层90或保护层120。然后,可以用介电填充物(例如介电填充物100或介电填充物130)横向密封柱74。接下来,可以将介电填充物平坦化并齐平到柱74的顶部,然后可以形成字线112。

在图27A和图27B中,图示了相同于图26A和图26B的结构,但柱74图示为具有倾斜或锥形侧壁。在一些实施例中,柱74可以是不同的形状,如图4A、图4B、图4C和图4D所示。在图27A和图27B中,当蚀刻层(底部电极24、存储器储存结构34、界面层44、选择器结构54和顶部电极64)而形成柱时,蚀刻可能产生不垂直的侧壁。在一些实施例中,侧壁可以向外倾斜,如图27A和图27B所示,而在其他实施例中,例如通过翻转柱74的形状,侧壁可以向内倾斜。这些变化可以被其他附图替代,但为了简单起见,不另行单独说明。

图28和图29示出了第一OTS材料层55和第二OTS材料层57的梯度曲线图的几种变化。每个图的左侧表示包括图8A中的布局的选择器结构54,第一OTS材料层55夹在两个第二个OTS材料层57之间。这些层是柱74的部分,柱74包括选择器结构54上方的层和选择器结构54下方的层。这些上方和下方的层可能因布局而异,如上文关于图5A、图5B、图5C和图5D所描述的。

图28和图29中的每个图的右侧都包括一些图形,其中一个轴是选择器结构54的深度曲线图,另一个轴是选择器结构54中材料的原子百分比浓度。第一OTS材料层55和第二个OTS材料层57之间的层与层之间的分界从左侧延伸穿过图形。

标记为250A、250B和250C的线表示第一OTS材料层55和第二OTS材料层57共有的元素的原子百分数浓度。标记为260A和260B的线表示第一OTS材料层55独有的元素的原子百分比浓度。如上所述,第一OTS材料层55包括与第二OTS材料层57(和第三OTS材料层59)相同的元素的子集,以及第一OTS材料层55独有的附加元素。

在图28中,共有的元素的浓度高于非共有的元素。因此,共有的元素的浓度百分比大于第一OTS材料层55独有的元素的浓度百分比。在图29中,第一OTS材料层55独有的元素比共有的元素具有更高的浓度百分比。因此,第一OTS材料层55中的独有元素的浓度百分比图示为大于第二OTS材料层57。

在图28中,第一个图形的线250A示出了第一OTS材料层55和第二OTS材料层57中的共有元素从下部的第二个OTS材料层57到第一OTS材料层55逐渐增加,其中穿过第一OTS材料层55的厚度中的浓度平稳且一致。然后,共有的元素通过上部的第二OTS材料层57又逐渐减少。第二个图形的线250B示出了,第一OTS材料层55和第二OTS材料层57中共有的元素具有穿过下部的第二OTS材料层57和进入第一OTS材料层55的两个增加斜率。穿过第一OTS材料层55的厚度中的浓度平稳且一致。然后,共有的元素具有穿过第三OTS材料层57的另外两个减小斜率。第三图形的线250C示出了,第一OTS材料层55和第二OTS材料层57中的共有元素具有穿过下部的第二OTS材料层57并进入第一OTS材料层55的增加。然后,共有的元素进入到第一OTS材料层55时减少。然后,穿过第一OTS材料层55的厚度中的浓度平稳且一致。然后,共有的元素在进入上部的第二OTS材料层57时增加,然后穿过上部的第二OTS选择器上层57的剩余部分时减少。

图28的第一、第二和第三个图形中的每个的线260A示出了,第一OTS材料层55的独有元素实际上可以穿过下部的第二OTS材料层57的厚度时逐渐增加。例如,在沉积之后,第一OTS材料层55的独有元素可以扩散回相邻的第二OTS材料层57。对于第一OTS材料层55的厚度中,独有元素的浓度可以基本稳定。然后,对于上部的第二OTS材料层57,独有元素的浓度(线260A)可以穿过上部的第二OTS材料层57的厚度时减少。

在图29中,对于线250A、250B和250C,共有元素的浓度可能具有与上述图28所讨论内容类似的性质和特征。线260B具有与线260A类似的浓度特征,但第一OTS材料层55的独有元素的浓度大于第一OTS材料层55和第二OTS材料层57之间的共有元素的浓度。

图28和图29示出了第二OTS材料层57用于第一OTS材料层55的上方和下方的情况。在一些实施例中,第三OTS材料层59可以用于第一OTS材料层的上方或下方。在这些实施例中,浓度曲线可以与图28和图29中所示的相同,尽管第二OTS材料层57和第三OTS材料层59各自具有与第一切换层55共有的元素,但第二OTS材料层57和第三OTS材料层59的元素不共有。在一些实施例中,可以不使用第一OTS材料层55上方或下方的第二OTS材料层57。在这样的实施例中,所示曲线包括第一OTS材料层55和第二OTS材料层57之间的侧面/界面的浓度梯度。第一OTS材料层55相对于第二OTS材料层57的侧面的曲线与所示曲线相似,但更压缩。在这样的实施例中,相比于邻接层是第二OTS材料层57的情况,第一OTS材料层55的材料的扩散至更浅程度。取而代之的是,曲线被压缩成约为所示深度的10%至25%的深度距离内。

图30A和图30B示出了通孔150的形成,以将字线112和位线12耦合至金属化。在一些实施例中,介电填充物130可以不会被平坦化,相反,它可能会被保留以形成通孔150。在其他实施例中,在字线112和介电填充物130上沉积介电层140。然后,可以对应于通孔150穿过介电层130和介电层120形成开口。然后,通过在开口中沉积导电材料来形成通孔150。通孔150可以通过任何合适的工艺沉积,诸如通过ALD、CVD、镀覆等。在一些实施例中,可以在介电层140和通孔150之间形成阻挡层。

在图31A和图31B中,可以形成金属化层170,以在通孔150上方形成金属焊盘。可以通过首先在介电层140上沉积绝缘层160,例如层间电介质(ILD),然后在绝缘层160中形成与所形成的金属化图案相对应的开口来形成金属化层170。然后,可以通过任何合适的工艺形成金属化层170,诸如通过ALD、CVD、镀覆等。在一些实施例中,可以在介电层160和金属化层170之间形成阻挡层。

实施例具有优势。使用多层选择器结构可以改进切换性能,包括比单层选择器结构更灵敏的开/关切换特性,以及更小的周期至周期V

一个实施例是一种形成包括存储器单元的存储器结构的方法,该存储器结构插入在上电极和下电极之间。该方法还包括形成存储器单元的选择器结构,选择器结构插入在上电极和下电极之间,选择器结构包括设置在第一层中的第一材料和设置在第二层中的第二材料,第一材料包括第二材料和附加元素,第一材料包括双向阈值开关材料。该方法还包括在选择器结构上方形成字线,字线的纵长方向垂直于位线的纵长方向,位线设置在选择器结构下方。

在实施例中,第一层中的第一材料的浓度在第一层的整个厚度上基本均匀。在实施例中,第二层中的第二材料的浓度在第二层的整个厚度上具有浓度的梯度变化。在实施例中,浓度的梯度变化包括两个不同的斜率。在实施例中,第一斜率增加第二层中的第二材料的浓度,并且第二斜率减少第二层中的第二材料的浓度。在实施例中,第二层包括第一层中的附加元素,附加元素的浓度的梯度增加到第一层和第二层之间的界面。在实施例中,选择器结构设置在存储器结构上方。在实施例中,该方法可以包括:在存储器结构和选择器结构之间形成界面层。在实施例中,选择器结构包括第三层,第三层包括第三材料,第一层插入在第二层和第三层之间。在实施例中,第三材料不同于第二层的第二材料,其中第一层还包括第三材料。

另一种实施例是一种方法,包括形成位线金属。该方法还包括沉积底部电极金属。该方法还包括在底部电极金属上方沉积存储器层。该方法还包括在底部电极金属上方沉积选择器层。该方法还包括在选择器层上方沉积顶部电极金属。该方法还包括在顶部电极金属上方形成第一掩模,并且将顶部电极金属、选择器层、存储器层和底部电极金属图案化为与位线金属对应的条带的集合。该方法还包括沉积横向围绕条带的集合的绝缘层。该方法还包括在绝缘层和顶部电极金属上方形成字线金属。该方法还包括在字线金属上方形成第二掩模并图案化字线金属。该方法还包括使用第二掩模将顶部电极金属、选择器层、存储器层和底部电极金属图案化为柱的集合,每个柱对应于存储器单元。

在一个实施例中,该方法可以包括:沉积选择器层还包括:沉积包括第一双向阈值开关(OTS)材料的第一选择器层;和沉积包括第二OTS材料的第二选择器层,其中第二OTS材料包括第一OTS材料的子集。在实施例中,沉积选择器层还包括:沉积包括第三OTS材料的第三选择器层,其中第一选择器层插入在第二选择器层和第三选择器层之间,第一选择器层与第二选择器层具有第一共有界面以及与第三选择器层具有第二共有界面,第三OTS材料包括第一OTS材料的子集。在实施例中,第三OTS材料不同于第二OTS材料。

另一个实施例是一种器件,包括存储器单元,存储器单元可以包括:存储器结构,选择器结构,选择器结构包括第一材料层和第二材料层,其中第二材料层包括来自第一材料层的材料的子集,顶部电极,和底部电极,存储器结构和选择器结构插入在顶部电极和底部电极之间。该器件还包括耦合到底部电极的位线。该器件还包括耦合到顶部电极的源极线。

在实施例中,选择器结构还包括第三材料层,其中第三材料层包括来自第一材料层的材料的子集。在实施例中,第三材料层和第二材料层具有相同的材料成分。在实施例中,第一材料层中的第一材料的第一浓度对于第一材料层的整个厚度具有基本稳定的浓度曲线图。在实施例中,第一材料层独有的材料的第一百分比浓度大于第一材料层和第二材料层二者共有的材料的第二百分比浓度。在实施例中,第二材料层还包括第一材料层的材料的梯度百分比浓度。

上述概述了几个实施例的特征,以便本领域技术人员可以更好地理解本公开的各个方面。本领域技术人员应当理解,他们可以容易地使用本公开作为设计或修改用于实现本文所介绍的实施例的相同目的和/或实现其相同优点的其它过程和结构的基础。本领域技术人员还应当认识到,此类等效结构不背离本发明的精神和范围,并且它们可以在不背离本发明的精神和范围的情况下在本发明中进行各种改变、替换以及改变。

- 一种三维存储器件的形成方法及三维存储器件

- 可变电阻存储器件及形成可变电阻存储器件的方法

- 浮栅存储器件及其控制方法、3D存储器件与2D存储器件

- 交叉点存储器结构阵列和形成交叉点存储器结构阵列的方法

- 3D存储器件的制造方法及3D存储器件

- 具有防止存储器件内形成空洞的改进式存储器单元结构的存储器件

- 用于利用支撑结构形成三维存储器件的方法和产生的三维存储器件