一种芯片的金属布线结构及其芯片

文献发布时间:2023-06-19 09:54:18

技术领域

本发明涉及半导体芯片技术领域,尤其涉及一种芯片的金属布线结构及其芯片。

背景技术

随着芯片特征尺寸(Feature Size)的缩小,在同层金属边缘处的间隙(可以简单理解为同层金属线之间的空隙(space))存在机械应力;尤其是多层金属边缘重叠形成不同金属层的金属间隙重叠时,机械应力会更明显。

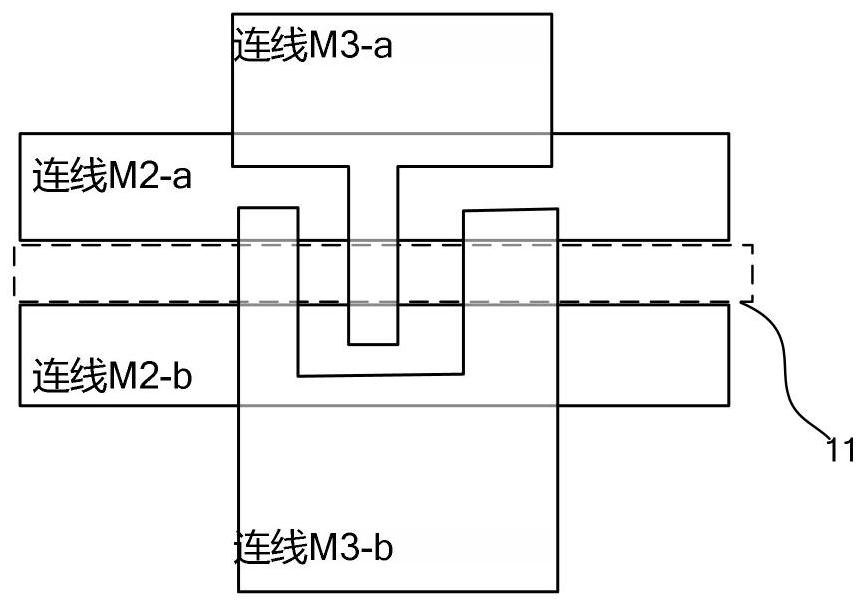

如图1现有技术金属布线平面示意图之一所示,图1中显示了不同层金属线的平面结构,这里示意了第二层金属M2(Metal2)和第三层金属M3(Metal3)。实际中还有更多的金属层,在图1中并未示意。M2的金属布线(或者称之为连线)为横向走线形式,如图中M2的金属布线M2-a和M2-b所示;M3的金属布线为纵向走线形式,如图中M3的金属布线M3-a和M3-b所示。金属布线M2-a和M2-b之间的空隙可以称之为间隙,如图中所示间隙11,同样的金属布线M3-a和M3-b之间的空隙可以称之为间隙。如图中所示间隙11。当然,实际芯片中金属布线会有很多,这里只是为了示意说明所以只显示了两层金属。

M2-a的边缘和M3-a的末端边缘重合,M2-b的边缘和M3-b的末端边缘重合;金属布线M2-a和M2-b之间的间隙和金属布线M3-a和M3-b之间的间隙重合,这样在它们重合的空间就形成了重叠的间隙11。

当然,第二层金属M2和第三层金属M3的连线也可以按照同样的方向走线,例如都按照同样走线方式(如图2现有技术金属布线平面示意图之二所示),金属布线M2-a和M2-b分别与金属布线M2-a和M3-b走线一致,都为横向走线形式),或者部分按照同样方式走线(如图4现有技术金属布线平面示意图之三所示),金属布线M2-a与M3-a走线一致,都为横向走线形式,金属布线M2-b与M3-b走线不一致,金属布线M2-b为横向走线形式,金属布线M3-b为纵向走线形式),总之只要在它们重合(重叠)的空间就形成了重叠的间隙11即可。

为了更清楚的说明问题,对于图1的剖面线AA’的剖面图如图4现有技术金属布线剖面示意图所示,这里图4中还增加了其它的金属层。由图2可以看出,在不同的金属层M2至Mn的不同金属布线关系下,形成了重叠的间隙11。

对于上述的重叠间隙11,在通常现有的集成电路芯片的版图(Layout)设计中,尤其是在金属层的布线中,基本不考虑金属上下层之间的关系,只要满足LVS(LayoutVersusSchematic)、DRC(Design Rule Check)等规则即可。这是由于以前芯片特征尺寸比较大,因此重叠的间隙11距离(即:图中M3-a和M3-b之间的距离)比较大,不会对芯片造成损坏。

但是随着芯片特征尺寸越来越小,间隙越来越小,间隙之间的机械应力越来越显著,机械应力向两边的金属布线方向(如图中黑色箭头所示)拉伸。当在间隙下面(或者上面)存在有金属线的时候(如图2中M1的金属布线M1-a),机械应力会导致下面(或者上面)的金属线造成损坏。尤其是在很多层金属叠加形成重叠间隙的情况下,机械应力对于间隙下(或者间隙上)的金属线的影响会更加明显,可以使金属线产生潜在裂缝等瑕疵。同时,由于芯片特征尺寸越来越小,金属线的宽度也越来越小,足够大的金属应力甚至会导致金属线断裂,从而造成芯片失效不能正常工作。如图4中M1的金属布线M1-a就因为机械应力的关系,而造成了损伤。

发明内容

为解决上述问题:根据本发明的第一方面,本发明提出了一种芯片的金属布线结构,所述金属布线结构包括多层金属布线,多层金属布线的间隙没有重叠。

优选的,所述多层金属布线的间隙没有重叠为相邻层金属布线的间隙没有重叠。

优选的,所述相邻层金属布线的间隙没有重叠为:金属布线边缘间隙被相邻层金属的布线跨越或者错开。

进一步优选的,所述相邻层金属为目标金属层和它的上层金属。

进一步优选的,所述相邻层金属为目标金属层和它的下层金属。

更进一步优选的,所述上层金属或下层金属的布线边缘与所述目标金属层的布线边缘不重叠。

更进一步优选的,所述上层金属或下层金属的布线边缘为齿状,所述齿状的上层金属或下层金属的布线第一部分在目标金属层布线的边缘内部错过间隙,所述齿状的上层金属或下层金属的布线第二部分在目标金属层布线的边缘外部跨越间隙。

更进一步优选的,所述上层金属或下层金属的布线的齿状被相应的设置为叉指的结构。

更进一步优选的,所述上层金属或下层金属的布线为并行的多个金属布线。

根据本发明的第二方面,本发明提出了一种芯片,所述芯片包括所述的金属布线结构。

优选的,所述芯片包含重复单元。

进一步优选的,所述重复单元为重复的金属布线。

进一步优选的,所述芯片为模拟或数字芯片

更进一步优选的,所述芯片为存储器芯片。

更进一步优选的,所述存储器芯片为易失或者非易失类型的存储器芯片。

更进一步优选的,所述芯片为带有缓存的逻辑运算芯片。

更进一步优选的,所述带有缓存的逻辑运算芯片为CPU芯片或者SOC。

更进一步优选的,所述芯片为FPGA芯片。

更进一步优选的,所述金属布线结构位于重复单元的中间区域。

更进一步优选的,所述金属布线结构位于芯片的边缘处。

本发明具有以下优点:

通过对金属布线的特殊设置,能够很大程度的克服因为机械应力所带来的可靠性问题,提高了芯片工作的稳定性。

附图说明

图1现有技术金属布线平面示意图之一;

图2现有技术金属布线平面示意图之二;

图3现有技术金属布线平面示意图之三;

图4现有技术金属布线平面示意图之一的剖面示意图;

图5本发明优选实施例一;

图6本发明优选实施例二;

图7本发明优选实施例三;

图8本发明优选实施例四;

具体实施方式

下面结合实施例及附图对本发明作进一步详细、完整地说明。

对于本发明的技术问题这里再做进一步的阐述,芯片中金属可靠性的问题是很难发现的。相对与芯片功能(function)问题,芯片的可靠性问题在芯片的测试验证过程中是隐性的,很难被发现和定位。通常芯片的设计完成后的认证阶段,对于可靠性需要进行大量不同的实验,例如老化实验、高低温实验等。本发明所要解决的技术问题,正是在基于大量不同类型的实验数据分析的基础上才发现的。

本发明的主要思路是:在芯片的金属(层)布线中,尽量减少或避免多层金属布线的边缘不会重叠,尤其是相邻层金属布线的边缘不会重叠,进一步的金属布线边缘间隙要被相邻(上层或下层)金属布线跨越或者错开。

如图5本发明优选实施例一所示;由图5可知,图中包含两层的金属M2和M3;金属M3在金属M2之上。这里仅以两层金属布线示意只是为了更清楚的说明问题,实际中可以为任意的两层或者是多层金属。M2的金属布线M2-a和M2-b之间形成了间隙11。

这里及其以下实施例中M2的金属布线M2-a和M2-b之间形成了间隙,可以认为已有间隙,把M2金属层认为是目标金属层,通过对它的相邻金属层进行设置以避免重叠间隙的形成。当然,这里只是示意,实际中任意有间隙的金属层都可以认为是已有间隙,都可以作为目标金属层对待,进而对它的相邻层金属布线进行设置以避免重叠间隙的形成。

为了解决背景技术中的问题,位于金属M2之上的金属M3的金属布线M3-a和M3-b进行了特别的设置。实际中,位于金属层M2之下的金属层,也可以或者应当做相应的设置。

金属M3的两个布线M3-a和M3-b形成的间隙与金属M2布线M2-a和M2-b形成的间隙错开分布设置。同时金属M3的一个布线M3-b跨越了金属M2布线的间隙11。

这样的好处是,通过将相邻层金属布线之间的间隙错开,避免了重叠的间隙的形成。

本发明的一种改进方式,在实施例一的基础上,对位于金属M2之上的金属M3的金属布线M3-a和M3-b进行了进一步的改进设置。如图6本发明优选实施例二所示;结合图6说明如下:

首先,与优选实施例一类似,金属布线M2-a的边缘和金属布线M3-a的末端边缘不在重合,M2-b的边缘和M3-b的末端边缘也不再重合;这样在它们就不会在重合的空间就形成重叠的间隙11。间隙11只是在M2的金属布线M2-a和M2-b之间形成。这样就大大的减少了间隙处的机械应力。

其次,金属层M3的金属布线M3-a和M3-b末端(边缘处)进行了特别的设置。金属布线M3-a和M3-b边沿分别成为齿状。即:金属布线M3-a和M3-b末端不再处于是同一水平线上,部分在M2的金属布线(M2-a和M2-b)边缘外部跨越间隙11,另一部分在M2的金属布线(M2-a和M2-b)边缘内部。如图所示,图中金属布线M3-a的末端(M3-a1和M3-a2)不在同一水平线上,部分(如图中M3-a1)在M2的金属布线M2-a的边缘外部跨越间隙11,另一部分(如图中M3-a2)在M2的金属布线M2-a的边缘内部错过间隙11。

实际中还可以是只有金属布线M3-a或者只有M3-b的情况。

这样的好处是:不仅避免了重叠的间隙11的形成(图中的间隙11只是单层金属M2形成),同时由于金属布线M3-a和/或M3-b利用齿状边缘形成部分跨越间隙(例如:M3-a1在M2的金属布线M2-b的边缘外部),部分远离金属间隙(例如:M3-a2在M2的金属布线M2-b的边缘内部)的情况,可以减少间隙向两边的机械应力,这样可以更好的提高芯片的可靠性。

本发明的另一种改进方式,在实施例二的基础上的优化,如图7本发明优选实施例三所示;由图7可知,与优选实施例二类似的,图中包含两层的金属M2和M3;金属M3在金属M2之上。位于金属M2之上的两个金属M3布线M3-a和M3-b利用齿状的边缘形成了叉指的结构。所谓的叉指结构如图所示,M3-a和M3-b边缘的齿状结构分别交错分布。

叉指结构除了具有优选实施例一的好处之外,同时还因为交错的跨越间隙11:所以能够更好的避免或降低间隙所产生的机械应力。

本发明的另一种改进方式,如图8本发明优选实施例四所示;由图8可知,与前述优选实施例类似的,图中包含两层的金属M2和M3;金属M3在金属M2之上。不同的是,金属M3为多条平行的设置的布线,例如上部的布线M3-a1、M3-a2……M3-an;下部的布线M3-b1、M3-b2……M3-bn。对于这样的方式的金属布线,相对应的布线彼此交错共同形成叉指的结构。

即:

M3的上部金属布线M3-a1位于金属布线M2-a边缘外部,从而跨越间隙11,相应M3的下部金属布线M3-b1位于金属布线M2-b边缘内部,从而错开间隙11;

M3的上部金属布线M3-a2位于金属布线M2-a边缘内部,从而错开间隙11,相应M3的下部金属布线M3-b2位于金属布线M2-b边缘外部,从而跨越间隙11。

M3的上部和下部金属布线依次交错设置分布。

这样设置的好处是:不仅避免了重叠的间隙11的形成,更进一步的是通过不同金属布线交错设置分布成叉指的结构,不同金属布线交错的设置抵消机械应力,从而可以更大程的度降低间隙的机械应力。

还需要说明的是,在芯片中如果存在大量重复单元,重复单元中间区域的机械应力非常集中。上述金属层在背景技术中所介绍的现有技术的情况下,机械应力会大大增加。芯片尤其是处在高低温交替的环境中,机械应力会变化剧烈。所以,通过本发明的技术以及上述实施例所进行金属布线的设置方式,更需要在芯片大量重复单元(或重复布线)的中间区域进行使用设置。

这里需要强调的是,在模拟或数字芯片中,都有可能存在大量重复单元,在重复单元的中间位置有可能用到被发明的技术。尤其是在数字电路为主的芯片中。例如有大量存储阵列的芯片,典型的比如存储器芯片,这里的存储器芯片可以是易失或者非易失类型的存储器;也可以是嵌入式存储器。由于为了存储数据,它们有着大量的存储阵列,这些存储阵列是重复单元。在存储阵列的中间位置,机械应力更为集中,所以更需要本发明的技术进行使用。特别的,在存储阵列的解码译码区域(尤其是相应地址的解码译码)及其存储数据传输的区域,存在大量的重复单元,这些重复单元还会有大量重复的金属布线,这种情况下,发生因机械应力而使芯片不能工作的前述问题更为严重,所以在解码译码区域,不仅有重复单元而且有重复的金属线使用的情况下,尤其是上层金属有大量重复使用的情形,应用本发明技术的所产生的效果会更好。当然上述大量重复的金属布线并不局限于解码译码区域及其存储数据传输的区域。

在带有缓存的逻辑运算芯片,比如CPU芯片或者SOC(System On Chip)芯片中,因为大量的计算内部包含有嵌入式的存储器,比如SRAM,甚至DRAM等。如前述,在这些存储器中也会使用本发明的技术。

另外,在FPGA芯片中(FieldProgrammable Gate Array),有大量重复可编程单元,这些重复单元的中间位置也可能会造成机械应力的集中,尤其是这些重复单元中有金属重复的时候,机械应力造成损坏的可能性更大,通过本发明可以更好的改善。

另外,因为由于芯片在封装后,外壳的机械压力会更多集中在的芯片边缘,所以在芯片的边缘处,也应该通过本发明的技术以及上述实施例所进行金属布线的设置方式,优化金属布线方式。

本发明的好处是:通过对金属布线的特殊设置,能够很大程度的克服因为机械应力所带来的可靠性问题,提高了芯片工作的稳定性。

- 一种芯片的金属布线结构及其芯片

- 金属再布线结构、芯片封装器件及芯片封装器件制作工艺