一种多层异质单晶薄膜衬底的制备方法

文献发布时间:2023-06-19 11:52:33

技术领域

本申请涉及半导体制备技术领域,特别涉及一种多层异质单晶薄膜衬底的制备方法。

背景技术

半导体工业进入后摩尔时代,依靠尺度微缩实现性能提升的途径将会遇到物理原理上难以跨越的瓶颈。将多种不同功能的器件进行片上异质集成或芯片化发展是的后摩尔时代实现功能器件性能提升另一条可行路径。这要求功能薄膜与半导体薄膜进行异质集成。

异质集成衬底通常由异质外延生长和离子注入剥离方法实现。但是,现在的异质外延生长和离子注入剥离方法难以制备较多层异质单晶薄膜。如21世纪初获得成功的绝缘体上硅材料,是由离子注入剥离方法得到的硅-氧化硅-硅材料的异质集成结构。然而在许多应用场景中,人们希望得到硅-铌酸锂-碳化硅-氧化硅-硅材料,以在一个平台上充分利用不同材料的优异特性。但是这类多层异质单晶薄膜衬底结构单独用传统的离子注入剥离方法所不能实现的,其主要瓶颈在于,不同单晶薄膜的离子注入、剥离温度等条件具有很大的差异。

发明内容

本申请实施例提供了一种多层异质单晶薄膜衬底的制备方法,可将任意多种具有功能薄膜与半导体薄膜集成于一片衬底,可用于多功能三维异质集成芯片的实现,为持续提高器件的性能提供一条可靠的途径。

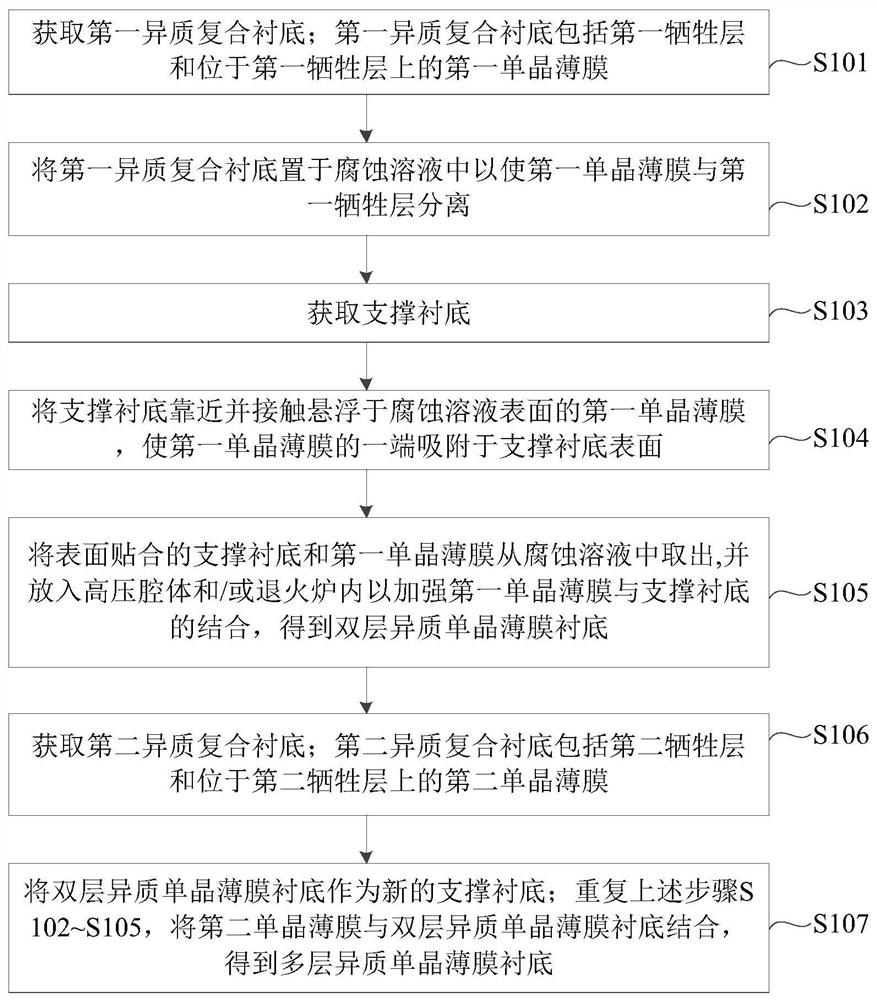

本申请实施例提供了一种多层异质单晶薄膜衬底的制备方法,包括:

S101,获取第一异质复合衬底;第一异质复合衬底包括第一牺牲层和位于第一牺牲层上的第一单晶薄膜;

S102,将第一异质复合衬底置于腐蚀溶液中以使第一单晶薄膜与第一牺牲层分离;

S103,获取支撑衬底;

S104,将支撑衬底靠近并接触悬浮于腐蚀溶液表面的第一单晶薄膜,使第一单晶薄膜的一端吸附于支撑衬底表面;

S105,将表面贴合的支撑衬底和第一单晶薄膜从腐蚀溶液中取出,并放入高压腔体和/或退火炉内以加强第一单晶薄膜与支撑衬底的结合,得到双层异质单晶薄膜衬底;

S106,获取第二异质复合衬底;第二异质复合衬底包括第二牺牲层和位于第二牺牲层上的第二单晶薄膜;

S107,将双层异质单晶薄膜衬底作为新的支撑衬底;重复上述步骤S102~S105,将第二单晶薄膜与双层异质单晶薄膜衬底结合,得到多层异质单晶薄膜衬底。

可选的,将表面贴合的支撑衬底和第一单晶薄膜从腐蚀溶液中取出,并放入高压腔体和/或退火炉内以加强第一单晶薄膜与支撑衬底的结合,包括:

将表面贴合的支撑衬底和第一单晶薄膜放置于高压腔体内,向高压腔体内充入高压气体;

其中,高压气体包括氧气、氮气和氩气中的至少一种;高压腔体内的压强为0.1~10Mpa;保持高压时间为1~10小时。

可选的,将表面贴合的支撑衬底和第一单晶薄膜从腐蚀溶液中取出,并放入高压腔体和/或退火炉内以加强第一单晶薄膜与支撑衬底的结合,包括:

将表面贴合的支撑衬底和第一单晶薄膜放置于退火炉内,采用温退火和高温退火相结合的方式进行;

其中,退火温度范围为100~1500摄氏度;退火过程中的升温速率小于每分钟1摄氏度;退火保温时间范围为1分钟至48小时;退火气氛包括氧气、氮气和氩气中的至少一种。

可选的,第一单晶薄膜与第二单晶薄膜的材质不相同。

可选的,第一单晶薄膜或第二单晶薄膜为硅、磷化铟、碳化硅、铌酸锂、钽酸锂、砷化镓和金刚石的任一种。

可选的,第一单晶薄膜或第二单晶薄膜的厚度范围为10纳米至100微米。

可选的,获取第一异质衬底包括,包括:获取绝缘体上铌酸锂结构衬底;

可选的,获取第二异质衬底,包括:获取绝缘体上碳化硅结构衬底;

其中,多层异质单晶薄膜衬底为碳化硅-铌酸锂-硅-氧化硅-硅结构衬底。

本申请实施例提供的一种多层异质单晶薄膜衬底的制备方法具有如下有益效果:

通过上述步骤S101~S107可以实现任意多层异质单晶薄膜衬底结构,且各异质单晶薄膜间的结合为范德华力结合,异质单晶薄膜之间的键合十分牢固;且本申请提供的一种任意多层异质单晶薄膜衬底的制备方法,可将多种具有不同功能的薄膜集成于一片衬底,用于多功能三维异质集成芯片的实现。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是本申请实施例提供的一种多层异质单晶薄膜衬底的制备方法的流程示意图;

图2a~2i是本申请实施例提供的一种多层异质单晶薄膜衬底的制备过程示意图;

图3是本申请实施例提供的一种碳化硅-铌酸锂之间键合界面的透射电子显微镜图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本申请保护的范围。

需要说明的是,本申请的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本申请的实施例能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或服务器不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

以下介绍本申请一种多层异质单晶薄膜衬底的制备方法的具体实施例,图1是本申请实施例提供的一种多层异质单晶薄膜衬底的制备方法的流程示意图,本申请本说明书提供了如实施例或流程图的方法操作步骤,但基于常规或者无创造性的劳动可以包括更多或者更少的操作步骤。实施例中列举的步骤顺序仅仅为众多步骤执行顺序中的一种方式,不代表唯一的执行顺序。结合图2a~2i所示的制备过程示意图,该方法可以包括:

S101,如图2a所示,获取第一异质复合衬底1;第一异质复合衬底1包括第一牺牲层11和位于第一牺牲层11上的第一单晶薄膜12。

一种可选的实施方式中,第一牺牲层11包括衬底硅111和二氧化硅层112。

一种可选的实施方式中,第一单晶薄膜12可以为硅、磷化铟、碳化硅、铌酸锂、钽酸锂、砷化镓和金刚石的任一种或其他功能薄膜或半导体材料。

S102,如图2b所示,将第一异质复合衬底1置于腐蚀溶液中以使第一单晶薄膜12与第一牺牲层11分离。

一种可选的实施方式中,腐蚀溶液为氢氟酸、缓冲氧化物刻蚀液和氟化铵溶液中的任一种。

S103,如图2c所示,获取支撑衬底2。

本申请实施例中,支撑衬底2的材质可以为硬质或柔性材料。

一种可选的获取支撑衬底的实施方式中,包括:获取绝缘体上硅结构衬底,绝缘体上硅结构衬底从下至上依次包括衬底硅211、氧化硅层212和硅薄膜213。

S104,如图2d所示,将支撑衬底2靠近并接触悬浮于腐蚀溶液表面的第一单晶薄膜12,使第一单晶薄膜12的一端吸附于支撑衬底2表面。

S105,如图2e所示,将表面贴合的支撑衬底2和第一单晶薄膜12从腐蚀溶液中取出,并放入高压腔体和/或退火炉内以加强第一单晶薄膜12与支撑衬底2的结合,得到双层异质单晶薄膜衬底3。

一种可选的实施方式中,步骤S105可以包括:

将表面贴合的支撑衬底2和第一单晶薄膜12放置于高压腔体内,向高压腔体内充入高压气体;其中,高压气体包括氧气、氮气和氩气中的至少一种;高压腔体内的压强为0.1~10Mpa;保持高压时间为1~10小时。

进一步地,步骤S105还可以包括:

将表面贴合的支撑衬底2和第一单晶薄膜12放置于退火炉内,采用温退火和高温退火相结合的方式进行;其中,退火温度范围为100~1500摄氏度;退火过程中的升温速率小于每分钟1摄氏度;退火保温时间范围为1分钟至48小时;退火气氛包括氧气、氮气和氩气中的至少一种。

S106,如图2f所示,获取第二异质复合衬底4;第二异质复合衬底4包括第二牺牲层41和位于第二牺牲层41上的第二单晶薄膜42。

一种可选的实施方式中,第二牺牲层41包括衬底硅411和二氧化硅层412。

一种可选的实施方式中,第一单晶薄膜42可以为硅、磷化铟、碳化硅、铌酸锂、钽酸锂、砷化镓和金刚石的任一种或其他功能薄膜或半导体材料。

具体的,第一单晶薄膜12与第二单晶薄膜42的材质可以相同,也可以不相同。

一种可选的实施方式中,第一单晶薄膜12或第二单晶薄膜42的厚度范围为10纳米至100微米。

S107,如图2g~2i所示,将双层异质单晶薄膜衬底3作为新的支撑衬底;重复上述步骤S102~S105,将第二单晶薄膜42与双层异质单晶薄膜衬底3结合,得到多层异质单晶薄膜衬底5。

本申请实施例中,通过上述步骤S101~S107可以实现任意多层异质单晶薄膜衬底结构,且各异质单晶薄膜间的结合为范德华力结合,异质单晶薄膜之间的键合十分牢固;且本申请实施例提供的一种任意多层异质单晶薄膜衬底的制备方法,可将多种具有不同功能的薄膜集成于一片衬底,用于多功能三维异质集成芯片的实现。

下面以制备铌酸锂-碳化硅-硅-氧化硅-硅为例对上述步骤S101~S107及其可选的实施方式进行进一步说明。

S101,获取一片尺寸为10mm*10mm的绝缘体上铌酸锂(LiNbO

S102,将LNOI置于腐蚀溶液中,腐蚀溶液将氧化硅层112腐蚀,一般需要1天左右的时间,使得铌酸锂薄膜12可以从硬质衬底中脱离,悬浮于液面;由于铌酸锂薄膜12的厚度较小,其具备一定的柔性和延展性,其弯曲角度可以达到60°,这保证在后续的操作步骤中薄膜不会碎裂;

S103,获取一片尺寸为10mm*10mm的绝缘体上硅结构2(Si on insulator,SOI),其由500um厚的硅衬底211、硅衬底上2um的氧化硅薄膜212以及氧化硅薄膜上500nm的硅薄膜213组成;

S104,将SOI衬底2中硅薄膜213的一面贴近步骤S102中悬浮于液面之上的铌酸锂薄膜12;由于薄膜间的毛细作用,铌酸锂薄膜12一端将吸附于SOI衬底2之上;

S105,对SOI衬底2相对于铌酸锂薄膜12表面进行缓慢的上拉运动,由于毛细作用力,铌酸锂薄膜12将跟随SOI衬底2运动,并逐渐贴合到SOI衬底2上,直至SOI衬底2与铌酸锂薄膜12从溶液中取出,形成铌酸锂-硅-氧化硅-硅的初步结合结构;

考虑到受液面气泡影响,铌酸锂薄膜12与SOI衬底2之间的界面层将出现气泡,且铌酸锂薄膜12会被顶起,因而为了消除该影响,可以将形成的铌酸锂-硅-氧化硅-硅的初步结合结构放置于高压腔体内,设置压强为5Mpa,保持高压时间为5小时,如此高压可以使得气泡被压破,从而消除铌酸锂薄膜12与SOI衬底2界面气泡,同时,气泡被压破后,被顶起的铌酸锂薄膜12会塌下去,重新铺在SOI衬底2上,从而整个表面的平整度将会提高,这为后续在铌酸锂薄膜12表面上继续得到平整的碳化硅薄膜提供了良好的表面;

为了进一步使得铌酸锂薄膜12与硅薄膜213直接的结合变得更加牢固,可以将铌酸锂-硅-氧化硅-硅的初步结合结构放置于退火炉中,采用后退火工艺,退火温度设置为550℃,退火时间为2小时,退火气氛为氮气气氛;从而可以得到铌酸锂-硅-氧化硅-硅结构的双层异质单晶薄膜衬底3;

S106,获取一片尺寸为10mm*10mm的绝缘体上碳化硅结构4(SiC on insulator,SiCOI),其由500um厚的硅衬底411、衬底上2um的氧化硅薄膜412以及氧化硅薄膜412上500nm的碳化硅薄膜42组成;SiCOI材料可以预先通过离子注入与剥离方法得到;

S107,同样的,将SiCOI置于腐蚀溶液中,大约2天左右的时间,使得碳化硅薄膜42可以从硬质衬底中脱离,悬浮于液面;由于碳化硅薄膜42的厚度较小,其具备一定的柔性和延展性,其弯曲角度可以达到60°,这保证在后续的操作步骤中薄膜不会碎裂;

将前述步骤S105中制备的铌酸锂-硅-氧化硅-硅结构的双层异质单晶薄膜衬底3中铌酸锂薄膜12的一面贴近步骤S107中悬浮于液面之上的碳化硅薄膜42;由于薄膜间的范德华力作用,碳化硅薄膜42将吸附与铌酸锂-硅-氧化硅-硅衬底之上,形成碳化硅-铌酸锂-硅-氧化硅-硅的初步结合结构;

将碳化硅-铌酸锂-硅-氧化硅-硅的初步结合放置于高压腔体内,设置压强5Mpa,保持高压时间为5小时;

采用后退火工艺,退火温度为500℃,退火时间为10小时,退火气氛为氮气气氛,最终得到牢固键合的碳化硅-铌酸锂-硅-氧化硅-硅的结构。

请参阅图3,图3是碳化硅-铌酸锂之间键合界面的透射电子显微镜图,图3中显示碳化硅薄膜和铌酸锂薄膜具有清晰的晶体结构,并且碳化硅的电子衍射花样具有清晰的单晶性点阵图案,说明在利用本申请上述方案的制备过程中,单晶材料的单晶性质可以得到很好的保持,有利于后续展开该结构的高性能多功能应用;另外,碳化硅薄膜和铌酸锂薄膜中间的无定形氧化硅层为碳化硅薄膜的自然氧化层,在材料晶格结构的过度区域,碳化硅薄膜和铌酸锂薄膜之间形成了良好的成键界面。

需要说明的是:上述本申请实施例先后顺序仅仅为了描述,不代表实施例的优劣。且上述对本说明书特定实施例进行了描述。其它实施例在所附权利要求书的范围内。在一些情况下,在权利要求书中记载的动作或步骤可以按照不同于实施例中的顺序来执行并且仍然可以实现期望的结果。另外,在附图中描绘的过程不一定要求示出的特定顺序或者连续顺序才能实现期望的结果。在某些实施方式中,多任务处理和并行处理也是可以的或者可能是有利的。

本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于设备实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

以上所述仅为本申请的较佳实施例,并不用以限制本申请,凡在本申请的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本申请的保护范围之内。

- 一种多层异质单晶薄膜衬底的制备方法

- 一种基于硅异质衬底的GaN层转移单晶薄膜制备方法