一种用于叠加的封装基底、叠加型封装基底及其芯片封装结构、制备方法

文献发布时间:2023-06-19 19:18:24

技术领域

本发明属于半导体封装技术领域,具体涉及一种用于叠加的封装基底、叠加型封装基底及其芯片封装结构、制备方法。

背景技术

在芯片的先进封装工艺制程中,芯片需要先转移到芯片封装厂进行高布线密度的封装制程和可靠性测试,再转送到贴装厂分别进行中布线密度的封装基板贴装和低布线密度的PCB板贴装。在此过程中,芯片封装厂和芯片贴装厂之间存在技术沟通、工艺链分属不同厂商等现象,导致芯片产品存在工艺加工周期长、产品加工成本高、芯片产品设计不灵活等问题。

在先进封装工艺中,需要完成晶圆划片、引出芯片引脚、并对芯片进行塑封保护等尺寸相对较小的封装工艺,其中用到的设备和辅材均是针对这一较小尺寸范围的封装制程,比如高布线密度扇出封装。芯片完成高布线密度的扇出封装工艺后,需要分别进行中、低布线密度的基板封装,由于基板中的铜布线的线宽和线径均较大,降低了铜布线的密度,造成芯片的贴装集成度较低。并且,芯片在封装厂和贴装厂之间转送,增加了转送过程中的产品可靠性风险及运输成本,芯片产品的封装工艺加工周期也较长。

发明内容

针对现有技术中所存在的不足,本发明提供了一种可提高芯片封装集成度,缩短加工周期的一种用于叠加的封装基底、叠加型封装基底及其芯片封装结构、制备方法。

一种叠加型封装基底,包括相互导电接合的第一封装基底和第二封装基底,所述第一封装基底包括第一布线层、位于所述第一布线层下表面的第一接合介电层以及被所述第一接合介电层包围的第一接合导电柱;所述第二封装基底包括第二布线层、位于所述第二布线层上表面的第二接合介电层以及被所述第二接合介电层包围的第二接合导电柱;所述第一接合导电柱与所述第二接合导电柱对应形成导电接合;

所述第一接合介电层和所述第二接合介电层发生物理接合形成接合介电层。

作为优选的方案,所述第一布线层的布线密度高于所述第二布线层。

作为优选的方案,所述第一接合介电层和所述第二接合介电层所采用的光刻胶材料包括聚酰亚胺基光刻胶;

和/或,

所述第一接合导电柱采用铜材料,所述第二接合导电柱采用铜材料。

一种用于叠加的封装基底,包括第一布线层、位于所述第一布线层上的第一接合介电层以及位于所述第一布线层上且被所述第一接合介电层包围的第一接合导电柱,所述第一接合导电柱用于与另一封装基底的导电柱形成导电接合,所述第一接合介电层用于与所述另一封装基底上的包围所述导电柱的介电层物理接合;

所述第一接合介电层的平均纵向高度小于所述第一接合导电柱的平均纵向高度。

作为优选的方案,所述第一接合介电层与所述第一接合导电柱形成的平均第一纵向高度差在0.1nm~10nm之间。

一种叠加型封装基底的芯片封装结构,包括前述任一种叠加型封装基底,其中所述第一布线层上表面设有芯片封装层;所述芯片封装层包括芯片、焊盘及包封层,所述芯片通过所述焊盘与所述第一布线层电连接;所述包封层包覆所述芯片;

所述芯片封装层还包括填充在所述芯片与所述第一布线层之间的底填胶层。

一种叠加型封装基底的制备方法,包括如下步骤:

制备第一封装基底,所述第一封装基底包括第一布线层及其上的第一接合介电层,所述第一接合介电层中嵌设有与所述第一布线层电连接的第一接合导电柱;

制备第二封装基底,所述第二封装基底包括第二布线层及其上的第二接合介电层,所述第二接合介电层中嵌设有与所述第二布线层电连接的第二接合导电柱;

使所述第一接合导电柱和所述第二接合导电柱的位置对应,并通过高温和/或高压和/或超声波处理进行导电接合。

作为优选的方案,所述制备第一封装基底,包括如下步骤:

在具有第一临时释放层的第一载板上制备第一布线层;

在所述第一布线层上制备具有开口阵列的第一接合介电层;

在所述第一接合介电层的开口阵列处制备第一接合导电柱并对其表面进行平坦化处理得到第一接合表面;

对所述第一接合表面进行氧气蚀刻,使第一接合介电层的平均纵向高度小于第一接合导电柱的平均纵向高度且形成第一纵向高度差;

所述制备第二封装基底,包括如下步骤:

在具有第二临时释放层的第二载板上制备第二布线层;

在所述第二布线层上制备具有开口阵列的第二接合介电层;

在所述第二接合介电层的开口阵列处制备第二接合导电柱并对其表面进行平坦化处理得到第二接合表面;

对所述第二接合表面进行氧气蚀刻,使第二接合介电层的平均纵向高度大于第二接合导电柱的平均纵向高度且形成第二纵向高度差。

作为优选的方案,所述第一接合表面的平均表面粗糙度为0.1nm-10nm;

和/或,

所述第二接合表面的平均表面粗糙度为0.1nm-10nm。

作为优选的方案,所述将所述第一接合导电柱和所述第二接合导电柱的位置对应,并通过高温和/或高压和/或超声波处理进行导电接合,包括如下步骤:

使所述第一接合导电柱和所述第二接合导电柱一一对应;

在高温和/或高压和/或超声波条件下,使所述第一接合介电层和第二接合介电层发生物理接合形成接合介电层,以及使所述第一接合导电柱表面的金属原子和所述第二接合导电柱表面的金属原子发生扩散形成导电接合。

作为优选的方案,在形成第一接合导电柱和第二接合导电柱之间的导电接合前,还包括如下步骤:

对所述第一接合介电层进行氧气蚀刻,使氧气蚀刻后对应的第一纵向高度差大于零;和/或

对所述第二接合介电层进行氧气蚀刻,使氧气蚀刻后对应的第二纵向高度差大于零。

作为优选的方案,当所述第一接合导电柱和/或所述第二接合导电柱采用纳米孪晶铜时,使所述第一接合导电柱和所述第二接合导电柱对准,再进行热处理以实现所述第一接合导电柱和所述第二接合导电柱之间的导电接合。

作为优选的方案,所述热处理温度范围为100℃-300℃。

一种叠加型封装基底的芯片封装结构的制备方法,包括前述任一所述的一种叠加型封装基底的制备方法,还包括如下步骤:

将芯片电连接到所述第一布线层上,并对芯片进行底部填充和塑封保护;

以所述第二布线层为基准面制备外联导电部件,得到芯片预封装体;

以若干芯片为单元分割所述芯片预封装体,制备得到具有叠加型封装基底的芯片封装结构。

一种叠加型封装基底的芯片封装结构的制备方法,包括如下步骤:

制备第一封装基底,所述第一封装基底包括第一布线层及其上的第一接合介电层,所述第一接合介电层中嵌设有与所述第一布线层电连接的第一接合导电柱;

在所述第一布线层关于所述第一接合介电层的相对另一侧上制备芯片封装层;

制备第二封装基底,所述第二封装基底包括第二布线层及其上的第二接合介电层,所述第二接合介电层中嵌设有与所述第二布线层电连接的第二接合导电柱;

在所述第二布线层关于所述第二接合介电层的相对另一侧上制备外联导电部件;

使所述第一接合导电柱和所述第二接合导电柱的位置对应,并通过高温和/或高压和/或超声波处理进行导电接合;

以若干芯片为单元进行分割,得到一种叠加型封装基底的芯片封装结构。

相比于现有技术,本发明具有如下有益效果:

首先,通过采用由布线密度不同的第一封装基底以及第二封装基底组合而成的叠加型封装基底,可将两种不同铜线尺寸的封装基底物理连接起来,其中第一封装基底是针对封装尺寸较小的芯片互连,第二封装基底用于与低布线密度的PCB板或封装基板互联,进而实现高布线密度的扇出再布线封装结构与低布线密度的PCB板或封装基板之间的过渡互联;其次,第二封装基底中的铜电路层采用芯片封装厂(而非传统的芯片贴装厂)的工艺制程,可进一步降低传统封装基板中的铜线尺寸,从而提高芯片的封装集成度,进一步降低芯片封装产品的尺寸;再次,由于芯片封装厂整合了一部分的传统封装基板工艺,还可精简芯片封装产品的加工工艺、降低芯片封装产品的加工周期。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

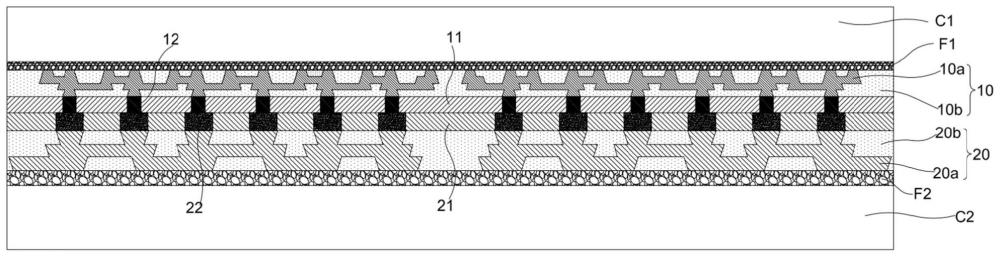

图1为本发明一种叠加型封装基底的芯片封装结构的示意图;

图2-图4为本发明第一种具有叠加型封装基底的芯片封装基底的制备方法步骤S1对应的结构示意图;

图5-图7为本发明第一种具有叠加型封装基底的芯片封装体的制备方法步骤S2对应的结构示意图;

图8-图10为本发明第一种具有叠加型封装基底的芯片封装体的制备方法步骤S3对应的结构示意图;

图11-图13为本发明第一种具有叠加型封装基底的芯片封装体的制备方法步骤S4对应的结构示意图;

图14为本发明第二种具有叠加型封装基底的芯片封装体的制备方法步骤S5对应的结构示意图。

图15为本发明第二种具有叠加型封装基底的芯片封装体的制备方法步骤S3′对应的结构示意图。

图16为本发明第二种具有叠加型封装基底的芯片封装体的制备方法步骤S5′对应的结构示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

在本申请使用的术语是仅仅出于描述特定实施例的目的,而非旨在限制本申请。在本申请的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“高度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本申请的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

第一方面,一种叠加型封装基底的芯片封装结构,如图1、图10所示,包括相互接合的第一封装基底P1和第二封装基底P2,所述第一封装基底P1包括第一布线层10、位于所述第一布线层10下表面的第一接合介电层11以及被所述第一接合介电层11包围的第一接合导电柱12;所述第二封装基底P2包括第二布线层20、位于所述第二布线层20上表面的第二接合介电层21以及被所述第二接合介电层21包围的第二接合导电柱22;所述第一接合导电柱12与所述第二接合导电柱22对应接合;所述第一布线层10的布线密度高于所述第二布线层20。所述第一布线层10上表面设有芯片封装层。

本实施例中,如图1所示,所述第一布线层10包括第一金属层10a和第一介电层10b,可采用多层布线结构;所述第二布线层20包括第二金属层20a和第二介电层20b,也可采用多层布线结构。所述第一布线层10的布线密度较高,对应所述第一金属层10a中的铜线尺寸较小,所述第一封装基底P1可用于与封装尺寸较小的芯片引脚的直接互连;所述第二布线层20的布线密度较低,对应所述第二金属层20a中的铜线尺寸较大,即所述第二金属层20a的线宽和线距均大于第一金属层10a的线宽和线距;所述第二封装基底P2可用于与低布线密度的PCB板之间的过渡互联。

所述第一封装基底P1和所述第二封装基底P2接合得到的叠加型封装基底,可将两种不同铜线尺寸的封装单元物理连接起来。所述第二封装基底中的铜电路层采用芯片封装厂的工艺制程,可进一步降低传统封装基板的铜线尺寸,从而提高芯片的封装集成度,进一步降低芯片封装产品的尺寸。此外,由于芯片封装厂整合了传统的封装基板工艺,还可精简芯片封装产品的加工工艺,进而降低芯片封装产品的加工周期。

作为优选的实施例,所述第一接合介电层11和所述第二接合介电层21对应接合,所述第一接合导电柱12和所述第二接合导电柱22对应物理接合,进而形成导电接合。

在一些实施例中,当第一接合导电柱12和第二接合导电柱22采用常规的电镀或化学镀制备以铜材料为导电介质时(也可采用其他本领域常见金属材料,如Al、Ag、Ni、W、Au等均可),所述第一接合导电柱12表面层的铜原子和第二接合导电柱22表面层的铜原子可在高温和/或高压和/或超声波条件下发生相互扩散,在高温和/或高压和/或超声波条件下形成基于铜原子共价键的接合铜层。具体地,所述高温和/或超声波条件使铜柱中的铜原子晶格振动加快,所述高压条件有利于第一接合导电柱12界面处的铜原子与第二接合导电柱22界面处的铜原子之间的相互扩散嵌入,从而在第一接合导电柱12界面和第二接合导电柱22界面之间形成一层铜原子共价键连接的同质融合铜层。并且,所述第一接合介电层11和所述第二接合介电层21可在高温和/或高压和/或超声波条件下发生物理接合形成接合介电层。

在一些实施例中,当采用高温处理来促进第一接合导电柱12表面层的铜原子和第二接合导电柱22表面层的铜原子之间的相互扩散融合时,由于高温处理会带来铜原子晶格的膨胀而发生铜柱的膨胀,以及接合介电层的膨胀,并且,一般情况下,接合介电层的热膨胀系数大于铜的热膨胀系数,因此需要在一一对应的第一接合介电层和第二接合介电层之间预留一定的间隙,且第一接合介电层和/或第二接合介电层的平均纵向高度小于第一接合导电柱和/或第二接合导电柱,使高温处理发生膨胀后的铜柱刚好物理接合,并且使高温处理发生膨胀的第一接合介电层和第二接合介电层刚好物理接合,所述间隙高度优选1nm-100nm。其中,所述第一接合介电层11的平均纵向高度可小于所述第一接合导电柱12的平均纵向高度且形成第一纵向高度差,其中,所述平均第一纵向高度差控制在0.1nm-10nm;所述第二介电层21的纵向高度可小于所述第二接合导电柱22的平均纵向高度且形成平均第二纵向高度差,其中,所述平均第二纵向高度差控制在0.1nm-10nm。

在一些实施例中,当第一接合导电柱12和第二接合导电柱22采用纳米孪晶铜时,首先,需要以第一接合介电层11为基准面来对第一封装基底进行平坦化的研磨处理,再在氧气蚀刻气氛中去除一定的第一接合介电层11,使第一接合介电层11的平均纵向高度小于第一接合铜柱的平均纵向高度且形成第一纵向高度差;还需要以第二介电层21为基准面来对第二封装基底进行平坦化的研磨处理,再在氧气蚀刻气氛中去除一定的第二接合介电层21,使第二接合介电层21的平均纵向高度小于第二接合铜柱的平均纵向高度且形成第二纵向高度差,其中,平坦化研磨的平均表面粗糙度(Ra)可以为0.1nm-10nm;然后,再对第一接合导电柱12和第二接合导电柱22进行一定温度范围的热处理即可实现纳米孪晶铜的导电接合,同时实现第一接合介电层11和第二接合介电层21之间的物理接合,其中,所述热处理温度为100℃-300℃。

作为优选的实施例,所述芯片封装层包括芯片、互连件E、底填胶层1和包封层2,所述芯片通过所述互连件E与所述第一布线层10电连接;所述包封层2包覆所述芯片。

本实施例中,如图1所示,所述芯片可包括第一芯片100和第二芯片200。所述芯片上的引脚柱101可通过焊料块102与所述焊盘13对应焊接,形成芯片到第一布线层的电连接。本实施例中可通过环氧树脂之类的材料对所述芯片进行塑封以形成包封层2,籍此对所述芯片进行包封保护,降低可靠性风险。

另外,所述芯片封装层还可包括填充在所述芯片与所述第一布线层之间的底填胶层1。所述底填胶层1的材料可以是环氧树脂基高分子材料;所述芯片通过底填胶层1来重新分配封装材料间的CTE失配导致的机械应力。

本方面所述的叠加型封装基底,其可由两个用于叠加的封装基底通过接合得到。举例来说,所述两个用于叠加的封装基底可以是所述第一封装基底P1和第二封装基底P2。其中,在两者接合之前,所述第一封装基底P1可包括第一布线层、位于所述第一布线层上的第一接合介电层以及位于所述第一布线层上且被所述第一接合介电层包围的第一接合导电柱。所述第二封装基底P2可包括第二布线层、位于所述第二布线层上的第二接合介电层以及位于所述第二布线层上且被所述第二接合介电层包围的第二接合导电柱。

所述第一接合导电柱用于与所述第二导电柱形成导电接合,所述第一接合介电层用于与所述第二接合介电层物理接合。

所述第一封装基底P1和第二封装基底P2中至少一者的介电层和导电柱具有纵向高度差。换句话说,所述第一接合介电层的平均纵向高度小于所述第一接合导电柱的平均纵向高度,和/或所述第二接合介电层的平均纵向高度小于所述第二接合导电柱的平均纵向高度。所述平均纵向高度差在0.1nm~10nm之间。

第二方面,一种叠加型封装基底的芯片封装结构的第一种制备方法,包括如下步骤:

S1:制备第一封装基底P1,所述第一封装基底P1包括第一布线层10及其上的第一接合介电层11,所述第一接合介电层11中嵌设有与所述第一布线层10电连接的第一接合导电柱12。

其中,本步骤S1具体可包括如下步骤:

S101:在具有第一临时释放层F1的第一载板C1上制备第一布线层10。

其中,如图2所示,准备第一载板C1,并在所述第一载板C1上制备第一临时释放层F1,然后在所述第一临时释放层F1上制备第一布线层10;所述第一布线层10包括第一介电层10b和第一金属层10a,所述第一介电层10b为导电金属的走线排布提供绝缘隔离作用。所述金属布线层10a可采用铜材料。所述第一布线层10可以由多层布线层组成。

所述第一介电层10b可采用涂覆聚酰亚胺光刻胶并经低温烘干、曝光、显影和高温固化等工艺制备所得。

S102:在所述第一布线层10上制备具有开口阵列的第一接合介电层11。

其中,如图3所示,对所述第一布线层10进行平坦化的研磨处理,得到表面平整度较高的第一布线层10表面;然后在所述第一布线层上制备第一接合介电层11。所述第一接合介电层11具有开口阵列,所述开口阵列用于露出所述第一金属层10a。

所述第一接合介电层11可采用涂覆聚酰亚胺光刻胶或直接贴敷带有感光剂的干膜,并经低温烘干、曝光、显影等工艺制备得到。也就是说,所述第一接合介电层11可以是经过低温烘干处理的聚酰亚胺光刻胶,其中的低温烘干处理是为了蒸发在第一接合介电层11中的有机溶剂和水分,并没有进行高温条件下的完全交联固化反应。

所述低温烘干的热处理温度范围根据光刻胶的材料成分而定,具体地,所述低温烘干的热处理的下限温度数值范围T1是为了去除光刻胶中溶剂,所述低温烘干的热处理的上限温度数值范围T2是为了让光刻胶充分交联固化,因此,针对所述第一接合介电层11的低温烘干的热处理温度范围为[T1,T2]。

S103:在所述第一接合介电层11的开口阵列处制备第一接合导电柱12并进行平坦化处理得到第一接合表面。所述第一接合导电柱12可采用铜材料。

其中,如图4所示,可在所述开口阵列处进行电镀铜或化学镀铜或沉积铜工艺,得到第一接合导电柱12;对所述第一接合介电层11及第一接合导电柱12的表面进行平坦化的研磨处理得到第一接合表面,使所述第一接合表面的平均表面粗糙度(Ra)≤10nm。所述第一接合导电柱12与第一金属层10a电连接。

S104:对所述第一接合表面进行氧气蚀刻,使第一接合介电层11的平均纵向高度小于第一接合导电柱12的的平均纵向高度且形成第一纵向高度差。

其中,将平坦化研磨处理后的第一接合介电层11和第一接合导电柱12的表面,置于氧气蚀刻气氛中,通过氧气蚀刻去除一定纵向高度的第一接合介电层,使第一接合介电层11的平均纵向高度小于第一接合导电柱12的平均纵向高度且形成第一纵向高度差,所述平均第一纵向高度差的范围为0.1nm-10nm。

S2:制备第二封装基底P2,所述第二封装基底P2包括第二布线层20及其上的第二接合介电层21,所述第二接合介电层21中嵌设有与所述第二布线层20电连接的第二接合导电柱22。

其中,本步骤S2具体可包括如下步骤:

S201:在具有第三临时释放层F3的第三载板C3上制备第二布线层20。

其中,如图5所示,准备第二载板C2,并在所述第二载板C2上制备第二临时释放层F3,然后在所述第二临时释放层F2上制备第二布线层20。所述第二布线层20包括第二金属层20a和第二介电层20b,所述第二介电层20b为金属的走线排布提供绝缘隔离作用。所述第二金属层20a可采用铜材料。所述第二布线层20可以由多层布线层组成。

S202:在所述第二布线层20上制备具有开口阵列的第二接合介电层21。

其中,如图6所示,对所述第二布线层20进行研磨处理,得到表面平整度较高的第二布线层20表面,并在所述第二布线层上制备第二接合介电层21。所述第二接合介电层21具有开口阵列,所述开口阵列用于露出所述第二金属层20a。

所述第二介电层20b可采用涂覆聚酰亚胺光刻胶或贴敷带有感光剂的干膜,并经低温烘干、曝光、显影等工艺制备所得。其中的低温烘烤处理是为了蒸发在第二接合介电层21中的有机溶剂和水分,所述低温烘干的热处理温度范围根据光刻胶的材料成分而定,具体地,所述低温烘干的热处理的下限温度数值范围T3是为了去除光刻胶中溶剂,所述低温烘干的热处理的上限温度数值范围T4是为了让光刻胶充分交联固化,因此,针对所述第二接合介电层21的低温烘干的热处理温度范围为[T3,T4]。

S203:在所述第二接合介电层21的开口阵列处制备第二接合导电柱22并平坦化处理得到第二接合表面。所述第二接合导电柱22可采用铜材料。

其中如图7所示,可在所述开口阵列处进行电镀铜或化学镀铜工艺,得到第二接合导电柱22;对所述第二接合介电层21及第二接合导电柱22的表面进行平坦化的研磨处理得到第二接合表面,使所述第二接合表面的平均表面粗糙度(Ra)≤10nm。所述第二接合导电柱22与第二金属层20a电连接。

S204:对所述第二接合表面进行氧气蚀刻,使第二接合介电层21的平均纵向高度小于第二接合导电柱22的平均纵向高度且形成第二纵向高度差。

其中,将平坦化研磨处理后的第二接合介电层21和第二接合导电柱22的表面,置于氧气蚀刻气氛中,通过氧气蚀刻去除一定纵向高度的第二接合介电层,使第二接合介电层21的平均纵向高度小于第二接合导电柱22的平均纵向高度且形成第二纵向高度差,所述平均第二纵向高度差的范围为0.1nm-10nm。

在一些实施例中,当采用高温处理来促进第一接合导电柱12表面层的铜原子和第二接合导电柱22表面层的铜原子之间的相互扩散融合时,由于高温处理会带来铜原子晶格的膨胀而发生铜柱的膨胀,以及接合介电层的膨胀,并且,一般情况下,接合介电层的热膨胀系数大于铜的热膨胀系数,因此需要在一一对应的第一接合导电柱和第二接合导电柱之间预留一定的间隙,并且第一接合介电层和/或第二接合介电层的平均纵向高度小于第一接合导电柱和/或第二接合导电柱的平均纵向高度,使高温处理发生膨胀后的铜柱刚好物理接合,同时使高温处理发生膨胀的第一接合介电层和第二接合介电层刚好物理接合。因此,可对经过研磨处理的第一接合介电层中进行氧气蚀刻去除一定纵向高度的第一接合介电层,使氧气蚀刻后的第一接合介电层在纵向高度上低于所述第一接合导电柱且形成一定的第一纵向高度差,所述平均第一纵向高度差控制在0.1nm-10nm;同理,也可对经过研磨处理的第二接合介电层中进行氧气蚀刻去除一定纵向高度的第一接合介电层,使氧气蚀刻后的第二接合介电层在纵向高度上低于所述第二接合导电柱且形成一定的第二纵向高度差,所述平均第二纵向高度差控制在0.1nm-10nm。

在一些实施例中,当所述接合铜柱采用纳米孪晶铜时,只需要将具有所述第一纵向高度差的第一接合导电柱和/或第二纵向高度差的的第二接合导电柱对准,再进行一定温度范围的热处理即可实现接合铜柱的导电接合,其中,所述热处理温度为100℃-300℃。

在一些实施例中,所述第二布线层20中的第二金属层20a的布线密度与所述第一布线层10中的第一金属层10a的布线密度不同。具体地,如图8所示,本实施例中可采用所述第二金属层20a的布线密度小于所述第一金属层10a的布线密度的方案,其中第二金属层20a的线宽和线距均大于第一金属层10a的线宽和线距。第二金属层20a中直径较大金属线可用于充当高布线密度的扇出再布线封装与低布线密度的PCB板之间的过渡互联;第一金属层10a中直径较小的金属线可用于与芯片引脚之间的互联。

S3:将所述第一封装基底P1的第一接合导电柱12和所述第二封装基底P2的第二接合导电柱22的位置对应,并通过高温和/或高压和/或超声波处理进行接合。

其中,本步骤S3具体可包括如下步骤:

S301:将所述第一接合导电柱12和所述第二接合导电柱22一一对应,如图8所示。

S302:在高温和/或高压和/或超声波条件下,使所述第一接合介电层11和第二接合介电层21进行交联接合,以及使所述第一接合导电柱12表面处的铜原子和所述第二接合导电柱22表面处的铜原子发生扩散并形成导电接合。

其中,如图9、图10所示,所述第一接合介电层11和第二接合介电层21的聚酰亚胺在经高温和/或高压和/或超声波处理形成接合介电层。此处的高温和/或高压和/或超声波处理可以实现第一接合介电层11和第二接合介电层21之间的物理接合,在二者之间形成接合介电层,将第一接合介电层11和第二接合介电层21紧密连接起来。

在一些实施例中,当第一接合导电柱和/或第二接合导电柱采用电镀铜或化学镀铜或沉积铜时,在高温和/或高压和/或超声波条件下,所述第一接合导电柱和第二接合导电柱中的铜原子会加快扩散速率,并在高压和/或超声波作用下冲破第一铜柱界面和第二铜柱界面,使第一接合导电柱12中的铜原子扩散嵌入到第二接合导电柱22中的铜晶体结构中,同时,第二接合导电柱22中的铜原子也扩散嵌入到第一接合导电柱12中的铜晶体结构中,从而形成导电连接良好的接合铜层。

在一些实施例中,当第一接合导电柱和/或第二接合导电柱采用纳米孪晶铜时,只需要将具有所述第一纵向高度差的第一接合导电柱和/或第二纵向高度差的的第二接合导电柱对准,

再进行一定温度范围的热处理即可实现接合铜柱的导电接合,其中,所述热处理温度为100℃-300℃。

至此,制备得到一种叠加型封装基底。

S4:将芯片与所述叠加型封装基底电连接,并对芯片进行底部填充和塑封保护,得到具有叠加型封装基底和外联导电部件的芯片预封装体。

本步骤S4具体可包括如下步骤:

S401:如图11所示,以第一布线层10为基准面制备焊盘13,并将芯片100和芯片200上的引脚柱101和焊料块102与焊盘13一一对应;

S402:如图12所示,引脚柱101和焊盘13之间通过高温回流焊工艺形成的焊球102’进行导电连接,即芯片100和芯片200与所述叠加型封装基底通过导电件E进行电连接;

底部填充导电件E,得到底填胶层1;

对芯片100和芯片200进行塑封填充制备塑封层2,并沿着芯片的无源面进行研磨,直至露出芯片中的硅材料,降低塑封填料对芯片散热的不利影响。

S403:如图13所示,准备带有第三临时释放层F3的第三载板C3,将S402中制备的芯片预封装结构翻转后贴合到第三临时释放层F3,去除第二临时释放层F2的第二载板C2;

以第二布线层20为基准面制备外联导电部件,所述外联导电部件包括外联导电柱23和外联焊球24。

S5:以若干芯片为单元分割芯片预封装体,制备得到具有叠加型封装基底和外联导电部件的芯片封装结构。

具体步骤如下:

如图14所示,将第一保护胶膜M1贴敷在外联导电部件上,翻转芯片封装结构;

准备带有第四临时释放层F4的第四载板C4,将芯片封装结构上的第一保护胶膜贴合在第四临时释放层F4上;

沿切割道3a将整个封装体以若干个芯片为单元进行分割,再解键合去除所述第四载板C4和第四临时释放层F4,得到如图1所示的芯片封装结构。

在一种叠加型封装基底的芯片封装结构的第二种制备方法中,包括如下步骤:

S1′:制备第一封装基底P1,参考步骤S1;

S2′:在所述第一布线层10关于所述第一接合介电层11的相对另一侧上制备芯片封装层,参考步骤S401~S402;

S3′:制备带有外联导电部件的第二封装基底P2,参考步骤S2。

如图15所示,在所述步骤S2的基础上,准备第五载板C5,并在所述第五载板C5上制备第五临时释放层F5,然后将第二接合介电层21和第二接合导电柱22贴敷到第五临时释放层F5上;并以第二布线层20为基准面制备外联导电部件。

其中,外联导电部件包括外联导电柱23和外联焊球24。

S4′:参考步骤S3,将所述第一封装基底P1中的第一接合导电柱12和所述第二封装基底P2中的第二接合导电柱22进行接合。

S5′:如图16所示,以若干芯片为单元分割叠加型封装基底,得到如图1所示的具有叠加型封装基底的芯片封装结构。

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。