半导体器件以及电子装置

文献发布时间:2023-06-19 09:51:02

技术领域

本公开涉及半导体器件以及电子装置。

背景技术

专利文献1中作为半导体器件而公开了在半导体层形成有多个沟槽的沟槽型肖特基整流器。这些的多个沟槽包含被设置在半导体层的外周部的附近的周围沟槽、以及被设置在比周围沟槽更远离半导体层的外周部的位置的内部沟槽。

在先技术文献

专利文献

专利文献1:JP特表2003-522513号公报

发明内容

-解决课题的手段-

本公开的半导体器件具备:

第1层,具有包含第1导电型的杂质的第1半导体;

第2层,与所述第1层相接,具有包含比所述第1半导体低浓度的第1导电型的杂质的第2半导体;

第1电极,相接于所述第1层的与所述第2层相反的一侧的第1面;和

第2电极,相接于所述第2层的与所述第1层相反的一侧的第2面,

所述第2层还具有:

第1沟槽,在内部具有与所述第2电极连接的第3电极;和

第2沟槽,位于比所述第1沟槽更靠近所述第2层的外周部的位置,在内部具有与所述第2电极连接的第4电极,

与所述第1沟槽和所述第2沟槽之间的所述第2面相接的所述第2电极的整个外周端相接于所述第4电极。

本公开的电子装置具备半导体器件,

所述半导体器件具备:

第1层,具有包含第1导电型的杂质的第1半导体;

第2层,与所述第1层相接,具有包含比所述第1半导体低浓度的第1导电型的杂质的第2半导体;

第1电极,相接于所述第1层的与所述第2层相反的一侧的第1面;和

第2电极,相接于所述第2层的与所述第1层相反的一侧的第2面,

所述第2层还具有:

第1沟槽,在内部具有与所述第2电极连接的第3电极;和

第2沟槽,位于比所述第1沟槽更靠近所述第2层的外周部的位置,在内部具有与所述第2电极连接的第4电极,

与所述第1沟槽和所述第2沟槽之间的所述第2面相接的所述第2电极的整个外周端相接于所述第4电极。

附图说明

图1是表示本公开的实施方式所涉及的肖特基势垒二极管的立体图。

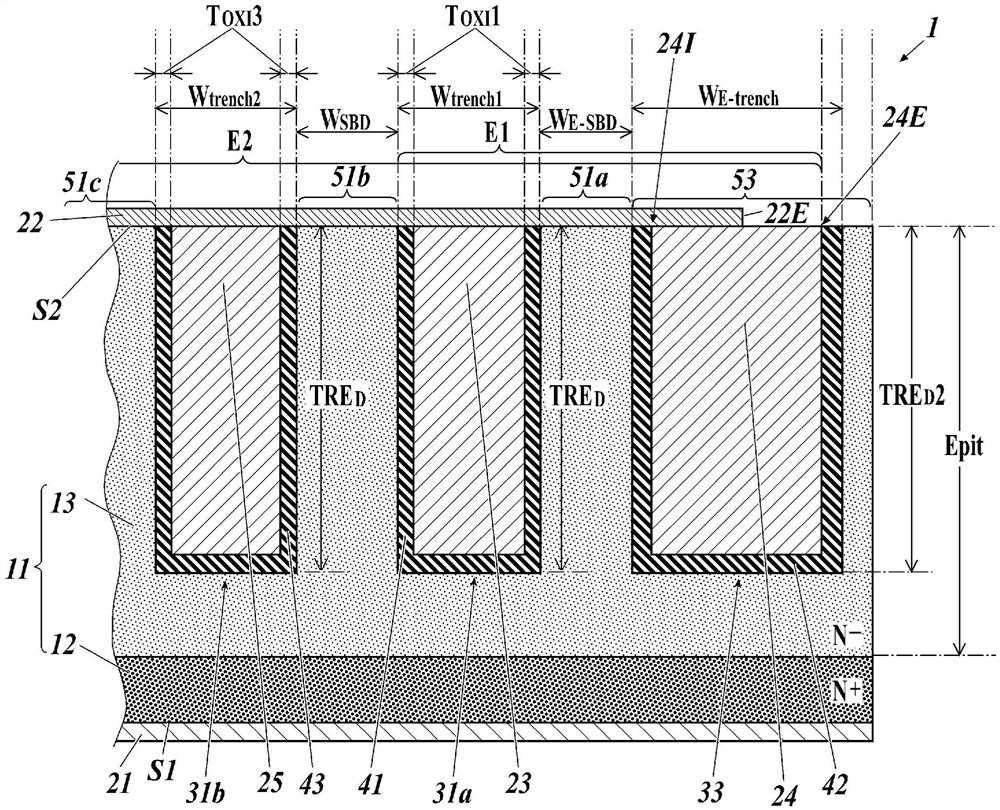

图2是表示图1的A-A线剖面的一部分的图。

图3是表示本公开的实施方式所涉及的肖特基势垒二极管的变形例的剖视图。

具体实施方式

以下,参照附图对本公开的实施方式进行详细说明。其中,存在对于已知的事项以及重复的事项等省略详细的说明的情况。附图以及以下的说明是为了本领域技术人员充分理解本公开。因此,附图以及以下的说明并不是意图限定权利要求书中记载的主题。全部的附图为示意图。附图的各部的相对尺寸可适当变更得较大或者变更得较小。

图1是表示本公开的实施方式所涉及的肖特基势垒二极管的立体图。图2是表示图1的A-A线剖面的一部分的图。图3是表示本公开的实施方式所涉及的肖特基势垒二极管的变形例的剖视图。

在本实施方式中,将从第1电极21朝向第2电极22的方向也称为上方,将其反向也称为下方。本实施方式所涉及的肖特基势垒二极管1具有板形状。将沿着肖特基势垒二极管1的板面的边缘的一圈的部分也称为外周部。在肖特基势垒二极管1的纵剖面,将靠近外周部的位置也称为外周侧,将靠近板面的中央的位置也称为中央侧。图2表示肖特基势垒二极管1的外周部的近旁。肖特基势垒二极管1相当于本公开所涉及的半导体器件的一例。

如图2所示,本实施方式所涉及的肖特基势垒二极管1具备:位于外周部的耐压部分53、和位于比耐压部分53更靠中央侧的整流器部分51a、51b、51c。

整流器部分51a、51b、51c的上方被第2电极22覆盖,侧方被相邻的一对内部沟槽31a、31b或者周围沟槽33的外表面夹着。在整流器部分51a、51b、51c中,在第2电极22与外延层13的N-型半导体的边界面生成肖特基势垒。

耐压部分53是从周围沟槽33到半导体层川的外周端的部分。耐压部分53缓和对肖特基势垒二极管1施加反向电压时从第2电极22的外周端施加于半导体层11的偏向的电场的集中,提升半导体层11的耐压。

肖特基势垒二极管1具备半导体层11、第1电极21和第2电极22。半导体层11包含半导体基板12和外延层13。半导体基板12相当于本公开所涉及的第1层的一例。外延层13相当于本公开所涉及的第2层的一例。

半导体基板12是硅基板,是含有微量的杂质的N型半导体(相当于本公开所涉及的第1导电型的第1半导体的一例)。杂质可以是砷(As)、磷(P)、锑(Sb)的任意。此外,半导体基板12也可以是P型半导体。在半导体基板12是P型半导体的情况下,以下的说明中的N型半导体可以替换为P型半导体。在半导体基板12是P型时,杂质可以是硼(B)、铝(A1)的任意。此外,半导体基板12可以是包含碳化硅(SiC)、氮化镓(Gallium nitride、GaN)、氧化镓(Ga

外延层13可以使用蒸镀法、分子线外延法、升华法、热分解法、CVD(ChemicalVapor Deposition:化学气相沉积)法、喷雾CVD(Chemical Vapor Deposition)法等各种的公知技术来形成。外延层13是与半导体基板12相同的导电型,相比于半导体基板12,含有低浓度的杂质。也就是说,外延层13包含N-型半导体(相当于本公开所涉及的第2半导体的一例)。另外,半导体基板12包含的杂质与外延层13包含的杂质可以不同。

外延层13具有多个内部沟槽31a、31b、以及一个周围沟槽33。一个内部沟槽31a相当于本公开所涉及的第1沟槽的一例。周围沟槽33相当于本公开所涉及的第2沟槽的一例。另一个内部沟槽31b相当于本公开所涉及的第3沟槽的一例。

包含两个内部沟槽31a、31b,多个内部沟槽可以在半导体层11的俯视下被设置为条纹状,也可以被设置为包围半导体层11的中央侧。内部沟槽31a、31b的数量可以是三个以上,也可以省略一个内部沟槽31b而设为一个。内部沟槽31a、31b在图2以及图3中在纸面前后方向延伸。

周围沟槽33位于耐压部分53,包围整流器部分51a、51b、51c。换言之,周围沟槽33沿着半导体层11的外周部,遍及半导体层11的整周而延伸。周围沟槽33在图2以及图3中,与内部沟槽31a、31b同样地在纸面前后方向延伸。

第1电极21相接于半导体基板12的与外延层13相反的一侧的面。该面也称为第1面S1。第1面S1在图2中位于纸面下侧。第1电极21包含金属。金属可以是包含合金的各种金属。此外,第1电极21也可以是其他的导体。

第2电极22相接于外延层13的与半导体基板12相反的一侧的面。该面也称为第2面S2。第2面S2在图2中位于纸面上侧。第2电极22包含金属。金属可以是包含合金的各种金属。此外,第2电极22也可以是其他的导体。

内部沟槽31a、31b以及周围沟槽33在外延层13的上下方向(即厚度方向)延伸。此外,内部沟槽31a、31b以及周围沟槽33在内侧分别具有在外延层13的厚度方向延伸的内部场电极23、25、24。内部沟槽31a包含的内部场电极23也称为第3电极。周围沟槽33包含的内部场电极24也称为第4电极。内部沟槽31b包含的内部场电极25也称为第5电极。内部场电极23~25可以是多晶硅。内部场电极23~25也可以是其他的导体。内部场电极23~25的一面在第2面S2露出。

内部沟槽31a、31b以及周围沟槽33还具有分别介于内部场电极23~25与外延层13的N-型半导体之间的绝缘膜41~43。内部沟槽31a具有的绝缘膜41也称为第1绝缘膜。周围沟槽33具有的绝缘膜42也称为第2绝缘膜。内部沟槽31b具有的绝缘膜43也称为第3绝缘膜。绝缘膜41~43可以包含电介质。内部沟槽31a、31b的内部场电极23、25分别隔着绝缘膜41、43而与外延层13的N-型半导体进行电容耦合。周围沟槽33的内部场电极24隔着绝缘膜42而与外延层13的N-型半导体进行电容耦合。

第2电极22的全部外周端22E位于周围沟槽33的内部场电极24露出的面上。换言之,在肖特基势垒二极管1的整周,在从上方观察时,第2电极22的外周侧的端(22E)位于从内部场电极24的外周侧的端24E到中央侧的端24I的范围。

内部场电极24以及绝缘膜42可以从第2面S2突出。内部场电极24以及绝缘膜42可以朝向肖特基势垒二极管1的外周侧,搭在周围沟槽33的外侧而延伸。内部场电极24以及绝缘膜42在周围沟槽33的外侧延伸时,第2电极22的外周端22E可以延伸为与内部场电极24的突出的部分重叠。绝缘膜42之中的搭在周围沟槽33的外侧的部分可以与周围沟槽33的内部的绝缘膜42同时形成。

第2电极22与内部沟槽31a、31b的内部场电极23、25电连接。通过内部场电极23、25,在被一对内部沟槽31a、31b夹着的N-型半导体的部分形成电场缓和区域。并且,在肖特基势垒二极管1的阻止状态下,在第1电极21与第2电极22之间被施加小于击穿电压的电压时,能够将整流器部分51a、51b、51c的肖特基势垒和电场缓和区域设为耗尽。由此,可减少肖特基势垒二极管1的反向漏电流。

第2电极22还与周围沟槽33的内部场电极24电连接。该电连接起到场板效应,缓和偏向于半导体层11的外周部的电场集中。周围沟槽33的内部场电极24在外延层13的厚度方向延伸。因此,基于周围沟槽33的场板效应在外延层13的厚度方向起作用,电场的峰值相比于不具备内部场电极24的情况而向周围沟槽33的底面侧移动。此外,周围沟槽33的内部场电极24的耐压侧的端部相比于第2电极22的端部,位于从整流器部分51a、51b、51c朝向耐压部分53的方向。因此,电场的峰值在从整流器部分51a、51b、51c朝向耐压部分53的方向移动。通过电场的峰值位置移动,从而电场集中被缓和,因此即便缩短耐压部分53的宽度,也能够得到期望的耐压性能。

为了将肖特基势垒二极管1的正向特性(正向电压VF等)维持在规定的值,不能减小整流器部分51a~51c的面积。但是,由于能够缩短耐压部分53的宽度,因此能够相应地减小肖特基势垒二极管1的芯片尺寸。

在本实施方式中,在第2面S2露出的内部场电极23、24的一面可以与外延层13的N-型半导体的第2面S2大致为一个面。在第2面S2露出的绝缘膜41、42的一面可以与外延层13的N-型半导体的第2面S2大致为一个面。换言之,第2面S2之中的至少从内部沟槽31a的中央侧的端部到内部场电极24的外周侧的端部的范围E1是平坦的。另外,在包含全部的内部沟槽31a、31b的范围E2,第2面S2可以是平坦的。因此,在第2面S2的范围E1、E2,没有其一部分向上方突出、或者产生阶梯的情况。由此,可提升在该范围E1、E2形成第2电极22时的阶梯覆盖(Step coverage)。

例如,为了电极从周围沟槽的内侧面形成到底部,需要将抗蚀剂在周围沟槽的底部成形为规定的形状。但是,在底部中,抗蚀剂的成形精度降低。因此,肖特基势垒二极管的成品率降低。在本实施方式中,第2电极22的加工精度不降低,能够提升成品率。

内部沟槽31a、31b的深度TRE

例如,若与内部沟槽的深度相比,周围沟槽的深度存在10%以上的不同,则将形成它们的工序单独设置等而工序数增加。本实施方式中,能够通过相同工序来形成内部沟槽31a、31b与周围沟槽33。

另外,如图3所示的变形例的肖特基势垒二极管1A那样,也可以内部沟槽31a、31b的深度与周围沟槽33的深度存在10%以上的不同。在使得周围沟槽33的深度比内部沟槽31a、31b深的情况下,能够提升肖特基势垒二极管1A相对于反向电压的耐压性能。

在将外延层13的厚度设为E

在将外延层13的厚度设为E

接下来,为了使说明变得容易,将两个内部沟槽31a、31b称为第1内部沟槽31a和第2内部沟槽31b。第2内部沟槽31b位于与第1内部沟槽31a相邻的位置,位于与周围沟槽33相反的一侧。也就是说,从第2面S2的中央侧向外周侧,按第2内部沟槽31b、第1内部沟槽31a以及周围沟槽33的这一顺序进行排列。第2内部沟槽31b相对于第1内部沟槽31a平行地延伸。第1内部沟槽31a的绝缘膜41与第2内部沟槽31b的绝缘膜43可以具有相同的厚度。在将第1内部沟槽31a与第2内部沟槽31b之间的距离设为W

周围沟槽33与第1内部沟槽31a相互平行地延伸。在将周围沟槽33与内部沟槽31a的距离设为W

在将第1内部沟槽31a的宽度设为W

另外,在实施方式中,表示了各种的沟槽的深度、宽度等的尺寸。这里所示的沟槽包含内部场电极以及绝缘膜。也就是说,所谓深度,是从第2面S2到沟槽内的绝缘膜之中最接近于半导体基板12的点的直线距离。此外,所谓宽度,是以绝缘膜的外缘为基准而决定的。图中将周围沟槽表示为最外周的沟槽,但是也可以在比周围沟槽更靠半导体层的外周侧设置其他的沟槽。

在实施方式中,作为本公开所涉及的半导体器件,以肖特基势垒二极管1为一例进行了说明。但是,本公开所涉及的半导体器件也可以是在半导体层的周边部具有沟槽构造的二极管、晶体管等。实施方式的肖特基势垒二极管1或者本公开所涉及的半导体器件可以被配备于各种的电子装置。电子装置例如可以是具有进行电力变换的电源电路的功率模块等。或者电子装置可以是各种的电子设备、电车、汽车等。

本实施方式的说明在全部的方面是例示,本发明并不限定于此。本公开只要相互没有矛盾,也可应用于适当进行了组合、变更、置换、附加、省略等的实施方式。并且,并未例示的无数的变形例可以理解为是没有脱离本发明的范围而能够想到的变形例。

产业上的可利用性

本发明能够利用于半导体器件以及电子装置。

符号说明

1 肖特基势垒二极管(半导体器件)

11 半导体层

12 半导体基板

13 外延层

21 第1电极

22 第2电极

22E 第2电极的外周端

31a内部沟槽(第1沟槽)

31b 内部沟槽(第3沟槽)

33 周围沟槽(第2沟槽)

51a、51b、51c 整流器部分

53 耐压部分

S1 第1面

S2 第2面

23 内部场电极(第3电极)

24 内部场电极(第4电极)

25 内部场电极(第5电极)

41 绝缘膜(第1绝缘膜)

42 绝缘膜(第2绝缘膜)

43 绝缘膜(第3绝缘膜)。

- 半导体器件、用于制造半导体器件的方法、固态成像元件、成像器件以及电子装置

- 一种半导体器件的制造方法、半导体器件和电子装置