具有电容耦合到浮栅的栅极的存储器单元的编程

文献发布时间:2023-06-19 10:32:14

本申请要求于2018年8月24日提交的美国临时申请第62/722,776号、于2018年10月17日提交的美国临时申请第62/746,962号以及于2018年12月12日提交的美国专利申请第16/217,916号的权益。

技术领域

本发明涉及非易失性存储器阵列。

背景技术

分裂栅极非易失性存储器单元和此类单元阵列是熟知的。例如,图1中示出了具有四个栅极的常规分裂栅极存储器单元10。每个存储器单元10包括形成于半导体衬底12中的源极区14和漏极区16,沟道区18在其间延伸。浮栅20形成在沟道区18的第一部分上方并且与其绝缘(并且控制其导电性),并且优选地形成在源极区14的一部分上方。选择栅22(也称为字线栅极)设置在沟道区18的第二部分上方并且与其绝缘(并且控制其导电性),并且还与浮栅20横向地相邻。控制栅28设置在浮栅20上方并且与其绝缘。擦除栅30设置在源极区14上方并且与其绝缘。优选地,存储器单元10成对形成,其中每对共享共同擦除栅30和共同源极区14,并且这些对首尾相接地布置,使得每个漏极区16由两个相邻的存储器单元对共享。

通过将高正电压置于擦除栅30上来擦除存储器单元10(其中从浮栅20去除电子),这导致浮栅20上的电子经由福勒-诺德海姆隧穿从浮栅20通过中间绝缘体遂穿到擦除栅30(在图1中通过从浮栅20延伸到擦除栅30的箭头以图形方式示出)。通过使擦除栅30中的凹口包绕浮栅20的上边缘来提高擦除效率。

通过在选择栅22、控制栅28、擦除栅30和源极区14上施加适当的正电压以及在漏极16上施加电流源来对存储器单元10进行编程(其中电子被放置在浮栅20上)。电子将沿着沟道区18从漏极16流动到源极14。当电子到达选择栅22和浮栅20之间的间隙时,电子将加速并且变热。由于来自浮栅20的吸引静电力(这是由于控制栅28上的正电压电容耦合到浮栅20而引起的),因此受热电子中的一些受热电子将被注入通过浮栅下方的栅极氧化物绝缘体并且注入到浮栅20上,如图1所示。该编程技术被称为热电子注入,并且在图1中通过沿着沟道区18延伸并且进入浮栅20的箭头以图形方式示出。

通过在漏极区16、选择栅22(其接通选择栅22下方的沟道区部分)和控制栅28(其电容耦合到浮栅20)上施加正读取电压来读取存储器单元10。如果浮栅20带正电(即,电子被擦除以及电容耦合到控制栅28上的正电压),则沟道区在浮栅20下方的部分也通过电容耦合电压被接通,并且电流将流过沟道区18,该沟道区被感测为擦除状态或“1”状态。如果浮栅20带负电(即,通过电子进行了编程),则沟道区在浮栅20下方的部分被大部分或完全关断(即,来自控制栅28的电容耦合电压不足以克服存储在浮栅20上的负电荷),并且电流将不会(或者有很少的电流)流过沟道区18,该沟道区被感测为编程状态或“0”状态。

还能够操作存储器单元10,使得其具有多个程序状态(称为多级单元(MLC),其中存储器单元10具有两种以上不同的程序状态,诸如存储两位信息的四个状态11、10、01和00)。还能够以模拟方式操作存储器单元10(即,不具有离散编程状态以产生一系列模拟读取信号值)。在这两种情况下,重要的是不对存储器单元进行过编程(即,在浮栅上放置太多电子),这是因为存储器单元稍后将不会产生恰当地反映预期程序状态的读取操作结果。但是,同样重要的是确保存储器单元10被充分编程,使得其程序状态稍后可在读取操作期间可靠地被检测。同样,对于多级单元或模拟单元应用,对存储器单元进行欠编程也不会产生期望的读取操作结果。因此,传统上,已知的是在离散脉冲中施加编程电压,其中在编程脉冲之间具有居间读取操作。具体地讲,将电压的编程脉冲施加到存储器单元,并且然后执行读取操作以确定沟道上的读取电流是否低于期望阈值。如果不是,则施加另一编程电压脉冲,并且执行另一读取操作以查看沟道上的读取电流是否低于阈值。该过程继续进行直到沟道上的读取电流低于阈值。为了防止过编程,脉冲相对较短,并且需要许多脉冲来充分编程存储器单元而不会过编程。事实上,典型的存储器单元可能需要介于10个和30个之间或甚至更多个编程电压脉冲,以将存储器单元恰当地编程到其期望的“0”状态。之所以如此,是因为对于期望的编程状态,每个编程脉冲不能以超过目标窗口(即,目标范围)的增量递增地改变存储器单元的编程状态(否则可能出现不期望的过编程水平)。该技术的优点在于,存储器单元被递增地编程,直到其相当精确地实现期望的程序状态(这将在读取操作期间提供期望的读取电流,使得可以可靠地检测程序状态)。该技术的缺点在于,执行由多个读取操作分开的如此多的编程电压脉冲需要花费相对较长的时间(例如,数十微秒)。

需要一种存储器单元编程技术,该技术能够在减少的时间量内准确地和可靠地对存储器单元进行编程而不会对存储器单元进行过编程。

发明内容

前述问题和需要通过存储器设备得到解决,该存储器设备包括按行和列布置的存储器单元和控制电路。存储器单元中的每个存储器单元包括:源极区和漏极区,该源极区和该漏极区形成在半导体衬底中,其中衬底的沟道区在源极区与漏极区之间延伸;浮栅,该浮栅设置在沟道区的第一部分上方并且与其绝缘,以用于控制沟道区的第一部分的导电性;选择栅,该选择栅设置在沟道区的第二部分上方并且与其绝缘,以用于控制沟道区的第二部分的导电性;控制栅,该控制栅设置在浮栅上方并且与其绝缘;和擦除栅,该擦除栅设置在源极区上方并且与其绝缘,并且设置成与浮栅相邻并且与其绝缘。该控制电路被配置为针对存储器单元中的一个存储器单元:将第一编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中第一编程电压脉冲包括施加到控制栅的第一电压;在施加第一编程电压脉冲之后执行读取操作,该读取操作包括针对施加到控制栅的不同电压检测通过沟道区的电流,以及使用对应于通过沟道区的目标电流的所检测到的电流来确定控制栅的目标电压;将第二编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中第二编程电压脉冲包括施加到控制栅的第二电压,该第二电压由第一电压、标称电压和目标电压确定;以及在施加第一编程电压脉冲和第二编程电压脉冲之后,通过将相应的读取电压施加到漏极区、选择栅和控制栅来确定一个存储器单元的程序状态,同时检测沟道区中的任何电流,其中读取电压包括施加到控制栅的标称电压。

存储器设备可包括按行和列布置的存储器单元和控制电路。存储器单元中的每个存储器单元包括:源极区和漏极区,该源极区和该漏极区形成在半导体衬底中,其中衬底的沟道区在源极区与漏极区之间延伸;浮栅,该浮栅设置在沟道区的第一部分上方并且与其绝缘,以用于控制沟道区的第一部分的导电性;选择栅,该选择栅设置在沟道区的第二部分上方并且与其绝缘,以用于控制沟道区的第二部分的导电性;控制栅,该控制栅设置在浮栅上方并且与其绝缘;和擦除栅,该擦除栅设置在源极区上方并且与其绝缘,并且设置成与浮栅相邻并且与其绝缘。控制电路被配置为针对存储器单元中的一个存储器单元:将第一编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中第一编程电压脉冲包括施加到擦除栅的第一电压;在施加第一编程电压脉冲之后执行读取操作,该读取操作包括针对施加到擦除栅的不同电压检测通过沟道区的电流,以及使用对应于通过沟道区的目标电流的所检测到的电流来确定擦除栅的目标电压;将第二编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中该第二编程电压脉冲包括施加到擦除栅的第二电压,该第二电压由第一电压、标称电压和目标电压确定;以及在施加第一编程电压脉冲和第二编程电压脉冲之后,通过将相应的读取电压施加到漏极区、选择栅、擦除栅和控制栅来确定一个存储器单元的程序状态,同时检测沟道区中的任何电流,其中读取电压包括施加到擦除栅的标称电压。

存储器设备可包括按行和列布置的存储器单元和控制电路。存储器单元中的每个存储器单元包括:源极区和漏极区,该源极区和该漏极区形成在半导体衬底中,其中衬底的沟道区在源极区与漏极区之间延伸;浮栅,该浮栅设置在沟道区的第一部分上方并且与其绝缘,以用于控制沟道区的第一部分的导电性;选择栅,该选择栅设置在沟道区的第二部分上方并且与其绝缘,以用于控制沟道区的第二部分的导电性;控制栅,该控制栅设置在浮栅上方并且与其绝缘;和擦除栅,该擦除栅设置在源极区上方并且与其绝缘,并且设置成与浮栅相邻并且与其绝缘。控制电路被配置为针对存储器单元中的一个存储器单元:将第一编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中第一编程电压脉冲包括施加到控制栅的第一电压和施加到擦除栅的第二电压;在施加第一编程电压脉冲之后执行读取操作,该读取操作包括针对施加到控制栅和擦除栅的不同电压检测通过沟道区的电流,以及使用对应于通过沟道区的目标电流的所检测到的电流来确定控制栅的第一目标电压和擦除栅的第二目标电压;将第二编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅(其中该第二编程电压脉冲包括施加到控制栅的第三电压和施加到擦除栅的第四电压,该第三电压由第一电压、第一标称电压和第一目标电压确定,该第四电压由第二电压、第二标称电压和第二目标电压确定);以及在施加第一编程电压脉冲和第二编程电压脉冲之后,通过将相应的读取电压施加到漏极区、选择栅、擦除栅和控制栅来确定一个存储器单元的程序状态,同时检测沟道区中的任何电流,其中读取电压包括施加到控制栅的第一标称电压和施加到擦除栅的第二标称电压。

一种操作存储器设备的方法,该存储器设备包括按行和列布置的存储器单元。存储器单元中的每个存储器单元包括:源极区和漏极区,该源极区和该漏极区形成在半导体衬底中,其中衬底的沟道区在源极区与漏极区之间延伸;浮栅,该浮栅设置在沟道区的第一部分上方并且与其绝缘,以用于控制沟道区的第一部分的导电性;选择栅,该选择栅设置在沟道区的第二部分上方并且与其绝缘,以用于控制沟道区的第二部分的导电性;控制栅,该控制栅设置在浮栅上方并且与其绝缘;和擦除栅,该擦除栅设置在源极区上方并且与其绝缘,并且设置成与浮栅相邻并且与其绝缘。该方法包括,针对存储器单元中的一个存储器单元:将第一编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中第一编程电压脉冲包括施加到控制栅的第一电压;在施加第一编程电压脉冲之后执行读取操作,该读取操作包括针对施加到控制栅的不同电压检测通过沟道区的电流,以及使用对应于通过沟道区的目标电流的所检测到的电流来确定控制栅的目标电压;将第二编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中第二编程电压脉冲包括施加到控制栅的第二电压,该第二电压由第一电压、标称电压和目标电压确定;以及在施加第一编程电压脉冲和第二编程电压脉冲之后,通过将相应的读取电压施加到漏极区、选择栅和控制栅来确定一个存储器单元的程序状态,同时检测沟道区中的任何电流,其中读取电压包括施加到控制栅的标称电压。

一种操作存储器设备的方法,该存储器设备包括按行和列布置的存储器单元。存储器单元中的每个存储器单元包括:源极区和漏极区,该源极区和该漏极区形成在半导体衬底中,其中衬底的沟道区在源极区与漏极区之间延伸;浮栅,该浮栅设置在沟道区的第一部分上方并且与其绝缘,以用于控制沟道区的第一部分的导电性;选择栅,该选择栅设置在沟道区的第二部分上方并且与其绝缘,以用于控制沟道区的第二部分的导电性;控制栅,该控制栅设置在浮栅上方并且与其绝缘;和擦除栅,该擦除栅设置在源极区上方并且与其绝缘,并且设置成与浮栅相邻并且与其绝缘。该方法包括,针对存储器单元中的一个存储器单元:将第一编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中第一编程电压脉冲包括施加到擦除栅的第一电压;在施加第一编程电压脉冲之后执行读取操作,该读取操作包括针对施加到擦除栅的不同电压检测通过沟道区的电流,以及使用对应于通过沟道区的目标电流的所检测到的电流来确定擦除栅的目标电压;将第二编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中该第二编程电压脉冲包括施加到擦除栅的第二电压,该第二电压由第一电压、标称电压和目标电压确定;以及在施加第一编程电压脉冲和第二编程电压脉冲之后,通过将相应的读取电压施加到漏极区、选择栅、擦除栅和控制栅来确定一个存储器单元的程序状态,同时检测沟道区中的任何电流,其中读取电压包括施加到擦除栅的标称电压。

一种操作存储器设备的方法,该存储器设备包括按行和列布置的存储器单元。存储器单元中的每个存储器单元包括:源极区和漏极区,该源极区和该漏极区形成在半导体衬底中,其中衬底的沟道区在源极区与漏极区之间延伸;浮栅,该浮栅设置在沟道区的第一部分上方并且与其绝缘,以用于控制沟道区的第一部分的导电性;选择栅,该选择栅设置在沟道区的第二部分上方并且与其绝缘,以用于控制沟道区的第二部分的导电性;控制栅,该控制栅设置在浮栅上方并且与其绝缘;和擦除栅,该擦除栅设置在源极区上方并且与其绝缘,并且设置成与浮栅相邻并且与其绝缘。该方法包括,针对存储器单元中的一个存储器单元:将第一编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅,其中第一编程电压脉冲包括施加到控制栅的第一电压和施加到擦除栅的第二电压;在施加第一编程电压脉冲之后执行读取操作,该读取操作包括针对施加到控制栅和擦除栅的不同电压检测通过沟道区的电流,以及使用对应于通过沟道区的目标电流的所检测到的电流来确定控制栅的第一目标电压和擦除栅的第二目标电压;将第二编程电压脉冲施加到源极区、选择栅、擦除栅和控制栅(其中该第二编程电压脉冲包括施加到控制栅的第三电压和施加到擦除栅的第四电压,该第三电压由第一电压、第一标称电压和第一目标电压确定,该第四电压由第二电压、第二标称电压和第二目标电压确定);以及在施加第一编程电压脉冲和第二编程电压脉冲之后,通过将相应的读取电压施加到漏极区、选择栅、擦除栅和控制栅来确定一个存储器单元的程序状态,同时检测沟道区中的任何电流,其中读取电压包括施加到控制栅的第一标称电压和施加到擦除栅的第二标称电压。

通过查看说明书、权利要求书和附图,本发明的其他目的和特征将变得显而易见。

附图说明

图1是4栅极非易失性存储器单元的侧面剖视图。

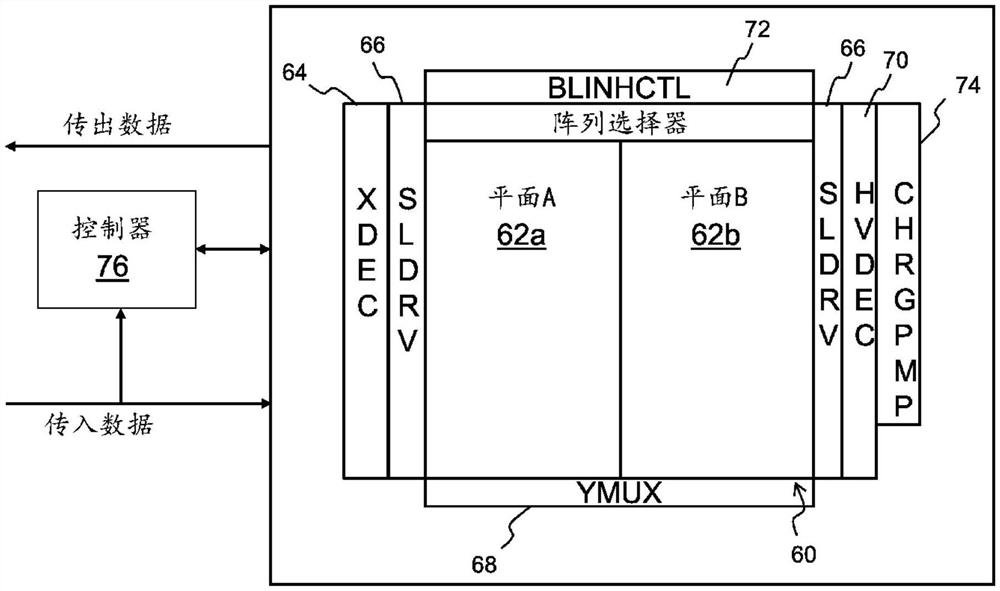

图2是存储器设备架构的平面图。

图3是存储器单元阵列的示意图/布局图(其中为简单起见未示出浮栅)。

具体实施方式

本发明涉及一种新的编程技术,该技术涉及少至两个编程电压脉冲以准确地编程存储器单元,而没有过编程的过度风险。该编程技术利用了以下事实:在编程期间施加到控制栅28的电压的大小强烈地决定了编程脉冲最终对存储器单元进行编程的程度。

该编程技术从将第一编程电压脉冲施加到正被编程的存储器单元开始,其中在该第一脉冲期间施加到控制栅28的电压是初始值V

V

其中V

还发现,在某些情况下,可省略第一编程脉冲和第二编程脉冲之间的擦除操作。具体地讲,如果确定如由等式1确定的V

在下表中提供了第一编程脉冲和第二编程脉冲的非限制性示例性电压和电流:

在下表中提供了用于读取和擦除存储器单元的非限制性示例性电压:

在上述两脉冲编程技术中,如果由第二读取操作确定未实现期望的编程状态,则存在若干选项。首先,如果由第二读取操作确定第二编程电压脉冲对存储器单元进行欠编程,则可使用通过确认读取操作分开的小增量编程脉冲的现有技术来递增地继续对存储器单元进行编程,直到实现期望的编程状态。然而,即使在这种情况下,与仅使用现有技术增量编程技术相比,编程脉冲的总体数量也大幅减少。其次,如果由第二读取操作确定未实现期望的编程状态,则可重复擦除操作并且可根据以下公式施加第三编程脉冲:

V

具体地讲,在施加第二编程脉冲并且确定存储器单元过编程或欠编程之后,执行第一扫读操作,其中在测量或检测通过沟道区18的读取电流时,控制栅28上的读取电压在值范围内扫过。该第二扫读操作的目的是确定控制栅上的第二目标电压V

在编程期间耦合到浮栅的电压不仅出现在控制栅和浮栅之间,而且出现在擦除栅和浮栅之间。因此,在第一另选实施方案中,能够在两脉冲编程技术中改变擦除栅而不是控制栅上的电压。具体地讲,到正被编程的存储器单元的第一编程电压脉冲将包括施加到擦除栅30的初始电压V

V

其中V

在下表中提供了对于该第一另选实施方案的用于读取和擦除存储器单元的非限制性示例性电压:

还发现,在某些情况下,对于该第一另选实施方案可省略第一编程脉冲和第二编程脉冲之间的擦除操作。具体地讲,如果确V

在第二另选实施方案中,在两脉冲编程技术中改变控制栅电压和擦除栅电压两者。具体地讲,到正被编程的存储器单元的第一编程电压脉冲将包括施加到擦除栅30的初始电压V

V

V

在下表中提供了对于该第二另选实施方案的第一编程脉冲和第二编程脉冲的非限制性示例性电压和电流:

在下表中提供了对于该第二另选实施方案的用于读取和擦除存储器单元的非限制性示例性电压:

还发现,在某些情况下,对于该第二另选实施方案可省略第一编程脉冲和第二编程脉冲之间的擦除操作。具体地讲,如果确定V

图2示出了示例性存储器设备的架构。存储器设备包括非易失性存储器单元的阵列60,该阵列可被分隔成两个单独的平面(平面A 62a和平面B 62b)。存储器单元可以是图1中所示的类型的存储器单元(即,存储器单元10),可以形成在单个芯片上,可以在半导体衬底12中按多行和多列布置。与非易失性存储器单元的阵列60相邻的是地址解码器(例如,XDEC 64(驱动字线的行解码器)、SLDRV 66(用于驱动源极线的源极线驱动器)、YMUX 68(驱动位线的列解码器)、HVDEC 70(高电压解码器)和位线控制器(BLINHCTL 72),其用于解码地址并且在所选存储器单元的读取操作、编程操作和擦除操作期间向各种存储器单元栅极和区供应各种电压。控制器76(包含控制电路)控制各种设备元件以实现目标存储器单元上的每个操作(编程、擦除、读取)(即,直接地或间接地提供电压和电流以操作如本文所讨论的存储器单元)。电荷泵CHRGPMP 74提供用于在控制器76的控制下读取、编程和擦除存储器单元的各种电压。

本发明的显著优点是对多个单元的编程可同时发生,并且相对于第一编程脉冲和第二编程脉冲以不同的粒度发生(即,涉及不同数量的存储器单元)。这相对于图3进行说明,图3示出了存储器阵列的架构(为简单起见未示出浮栅)。具体地讲,每个水平选择栅线22a将该行存储器单元10的所有选择栅22电连接在一起。每个水平控制栅线28a将该行存储器单元10的所有控制栅28电连接在一起。每个水平源极线14a将共享源极区14的两行存储器单元10的所有源极区14电连接在一起。每个位线16a将该列存储器单元10的所有漏极区16电连接在一起。每个擦除栅线30a将共享擦除栅30的两行存储器单元10的所有擦除栅30电连接在一起。因此,所有栅极线和源极线在水平(行)方向上伸展,并且位线在竖直(列)方向上伸展。

利用上述存储器阵列架构,可同时执行对多个单元的编程。具体地讲,第一编程脉冲和第二编程脉冲两者均可如下所述同时施加到多个存储器单元。首先,因为正被编程的每个存储器单元优选地使用第一编程脉冲的相同值来进行初始编程,所以不同行和不同列中的存储器单元可用第一编程脉冲同时进行编程。例如,可将第一程序脉冲施加到相同位线16a上的多个存储器单元10,包括经由控制栅线28a将V

第二程序脉冲也可同时施加到多个存储器单元10。具体地讲,在针对多个存储器单元10确定了V

相对于第一实施方案描述了使用第一编程脉冲和/或第二编程脉冲对多个存储器单元的同时编程,其中通过扫描控制栅电压来执行读取,并且基于确定适当的控制栅电压V

应当理解,本发明不限于上述的和在本文中示出的实施方案,而是涵盖在任何权利要求书的范围内的任何和所有变型形式。举例来说,本文中对本发明的提及并不意在限制任何权利要求书或权利要求术语的范围,而是仅参考可由这些权利要求中的一项或多项权利要求涵盖的一个或多个特征。上文所述的材料、工艺和数值的示例仅为示例性的,而不应视为限制权利要求书。材料的单个层可形成为此类材料或类似材料的多个层,并且反之亦然。最后,本发明对于不同的存储器单元应用(即多级单元(其中存储器单元除了未编程状态之外还具有两种或更多种不同的程序状态)和模拟(其中程序状态不限于离散步骤))是理想的。

应当指出的是,如本文所用,术语“在…上方”和“在…上”均包括性地包括“直接在…上”(之间没有设置中间材料、元件或空间)和“间接在…上”(之间设置有中间材料、元件或空间)。类似地,术语“相邻”包括“直接相邻”(之间没有设置中间材料、元件或空间)和“间接相邻”(之间设置有中间材料、元件或空间),“被安装到”包括“被直接安装到”(之间没有设置中间材料、元件或空间)和“被间接安装到”(之间设置有中间材料、元件或空间),并且“被电耦接到”包括“被直接电耦接到”(之间没有将元件电连接在一起的中间材料或元件)和“被间接电耦接到”(之间有将元件电连接在一起的中间材料或元件)。例如,“在衬底上方”形成元件可包括在两者间无中间材料/元件的情况下直接在衬底上形成该元件,以及在两者间有一种或多种中间材料/元件的情况下间接在衬底上形成该元件。

- 具有电容耦合到浮栅的栅极的存储器单元的编程

- 一种对具有单独擦除栅极的分栅式非易失性浮置栅极存储单元进行编程的方法