用于缓存控制的方法以及计算装置

文献发布时间:2023-06-19 11:05:16

技术领域

本公开的实施例总体涉及计算机领域,具体涉及用于缓存控制的方法以及计算装置。

背景技术

在计算机系统中,缓存通常位于计算单元和存储装置之间,用于减少计算单元访问存储装置获取数据的时间。缓存可以包括回写式(write back)缓存。对于回写式缓存而言,当计算单元要向存储装置中的某个地址写入数据时,它首先检查该地址在缓存中是否存在。如果在缓存中找到该地址(称为“命中”),则可以仅在缓存中更新数据并将缓存中的更新区域标记为脏,从而避免昂贵的存储装置访问。之后,在该更新区域准备好被替换时才将其中的数据写入存储装置。数据在缓存和存储装置之间进行交换更新时以缓存行(cacheline)作为最小单位进行交换。缓存行的大小例如包括但不限于32字节、64字节等。

缓存替换策略例如包括最近最少使用(LRU,Least Recently Used)、先进先出FIFO、后进先出LIFO等等。但是这种缓存替换策略导致在缓存刷新(flush)指令来到时已经积累了大量的脏缓存行,从而导致针对存储装置写入的拥塞。

发明内容

提供了一种用于缓存控制的方法以及计算装置,能够提高缓存刷新指令性能。

根据本公开的第一方面,提供了一种用于缓存控制的方法。该方法包括:如果确定从计算单元接收的存储指令中携带的地址与缓存中被标记为脏的缓存行相匹配,则:将存储指令中携带的数据写入缓存行;基于数据被写入到缓存行中的区域,更新与缓存行相关联的覆盖掩码,覆盖掩码用于指示缓存行中的多个区域的写入状态;以及如果确定所更新的覆盖掩码已满,则将缓存行中的数据写入存储装置,以及将缓存行标记为有效。

根据本公开的第二方面,提供了一种计算装置。该计算装置包括:计算单元;存储装置;缓存;以及缓存控制装置,与计算单元、存储装置和缓存相耦接,被配置为:如果确定从计算单元接收的存储指令中携带的地址与缓存中被标记为脏的缓存行相匹配,则:将存储指令中携带的数据写入缓存行;基于数据被写入到所述缓存行中的区域,更新与缓存行相关联的覆盖掩码,覆盖掩码用于指示缓存行中的多个区域的写入状态;以及如果确定所更新的覆盖掩码已满,则将缓存行中的数据写入存储装置,以及将缓存行标记为有效。

应当理解,本部分所描述的内容并非旨在标识本公开的实施例的关键或重要特征,也不用于限制本公开的范围。本公开的其它特征将通过以下的说明书而变得容易理解。

附图说明

结合附图并参考以下详细说明,本公开各实施例的上述和其他特征、优点及方面将变得更加明显。在附图中,相同或相似的附图标注表示相同或相似的元素。

图1是根据本公开的实施例的计算装置100的示意框图。

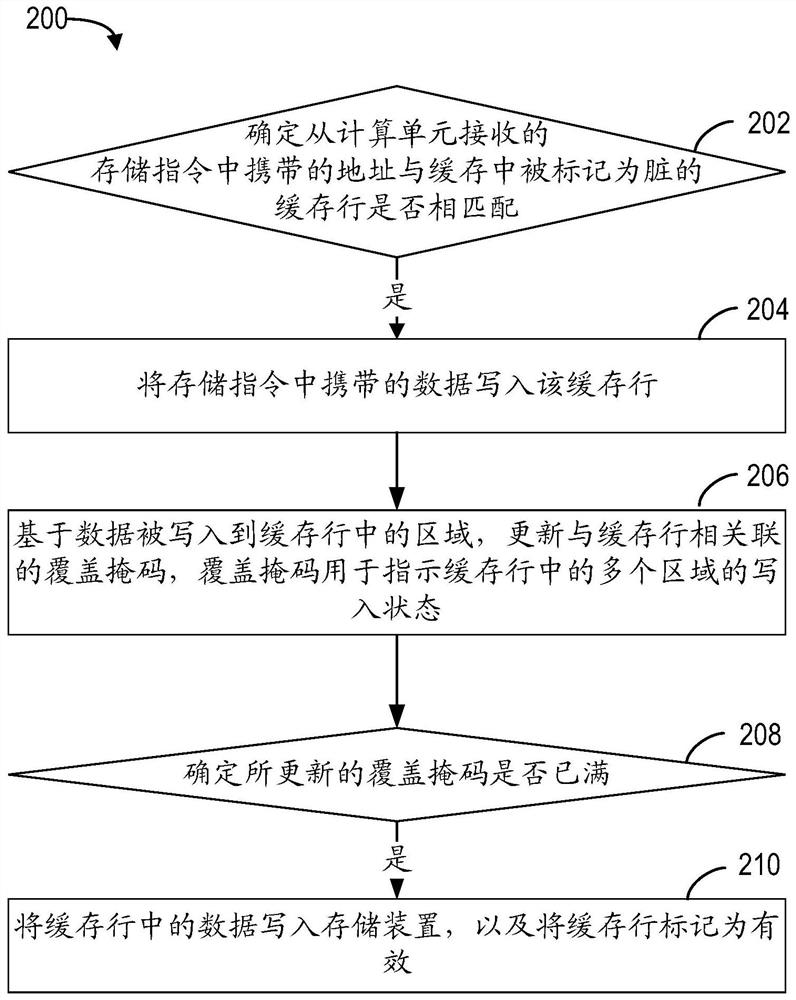

图2是根据本公开的实施例的用于缓存控制的方法200的示意图。

图3是根据本公开的实施例的用于更新与缓存行相关联的覆盖掩码的方法300的示意图。

图4是根据本公开的实施例的缓存行和覆盖掩码的对应关系400的示意图。

图5是根据本公开的另一实施例的缓存行和覆盖掩码的对应关系500的示意图。

具体实施方式

以下结合附图对本公开的示范性实施例做出说明,其中包括本公开实施例的各种细节以助于理解,应当将它们认为仅仅是示范性的。因此,本领域普通技术人员应当认识到,可以对这里描述的实施例做出各种改变和修改,而不会背离本公开的范围和精神。同样,为了清楚和简明,以下的描述中省略了对公知功能和结构的描述。

在本文中使用的术语“包括”及其变形表示开放性包括,即“包括但不限于”。除非特别申明,术语“或”表示“和/或”。术语“基于”表示“至少部分地基于”。术语“一个示例实施例”和“一个实施例”表示“至少一个示例实施例”。术语“另一实施例”表示“至少一个另外的实施例”。术语“第一”、“第二”等等可以指代不同的或相同的对象。下文还可能包括其他明确的和隐含的定义。

如上所述,当缓存刷新指令来到时已经累积了大量的脏缓存行,使得针对存储装置的写入发生拥塞。

为了解决上述问题,本公开提供了一种用于缓存控制的方法以及计算装置。

图1示出了根据本公开的实施例的计算装置100的示意框图。如图1所示,计算装置包括计算单元110、缓存控制装置120、缓存130和存储装置140。缓存控制装置120与计算单元110、缓存130和存储装置140相耦接。

关于计算单元110,其可以是各种具有处理和计算能力的通用和/或专用处理组件。计算单元110的一些示例包括但不限于中央处理单元(CPU)、图形处理单元(GPU)、各种专用的人工智能(AI)计算芯片、各种运行机器学习模型算法的计算单元、数字信号处理器(DSP)、以及任何适当的处理器、控制器、微控制器等。

计算单元110与缓存控制装置120之间可以连接有读信号线150、写信号线160、数据线170和地址线180。计算单元110可以向缓存控制装置120发送存储指令。存储指令可以通过写信号线160、数据线170和地址线180的形式来实现。例如计算单元110在写信号线160中发送写信号,在数据线170上发送待存储的数据,以及在地址线180上发送存储地址。

缓存控制装置120可以被配置为控制针对缓存130的数据存取。例如,缓存控制装置120可以被配置为接收来自计算单元110的存储指令,例如写信号线160上的写信号,数据线170上的数据以及地址线180上的地址,以及基于存储指令来控制针对缓存130的数据存储。缓存控制装置120可以采用任何合适的电路来实现。

缓存130是比存储装置140更快进行数据存取的存储器。作为一个示例,缓存130可以是静态随机存取存储器(SRAM)。缓存130可以包括多个缓存行1至n。缓存行作为缓存130和存储装置140之间进行数据交换的最小单位。缓存行可以包括多个区域。多个区域可以具有相同长度,长度例如为一个或多个字节。作为一个示例,缓存行可以包括128个字节。作为另一个示例,缓存行可以包括64个字节。

缓存行可以具有脏比特,用于指示缓存行中的部分数据可用但是数据尚未写入存储装置140。如果该比特被设置为预定值(例如设置为1),则确定该缓存行被标记为脏。

缓存行还可以具有有效比特,用于指示缓存行中的数据是否已经全部可用,也就是全部数据写入到存储装置140。如果该比特被设置为预定值(例如设置为1),则确定该缓存行被标记为有效。

存储装置140是比缓存130更慢进行存取的存储器。存储装置140包括下一级缓存或主存储装置。作为一个示例,主存储装置可以是动态随机存取存储器(DRAM)。

缓存控制装置120可以被配置为确定从计算单元110接收的存储指令中携带的地址(例如地址线180上的地址)是否与缓存130中被标记为脏的缓存行相匹配。

具体来说,缓存控制装置120可以被配置为确定从计算单元110接收的存储指令中携带的地址与缓存130中的缓存行是否相匹配。缓存控制装置120还可以被配置为如果确定从计算单元110接收的存储指令中携带的地址与缓存130中的缓存行相匹配,则确定缓存行是否被标记为脏。缓存控制装置120还可以被配置为如果确定缓存行被标记为脏,则确定从计算单元110接收的存储指令中携带的地址与缓存130中被标记为脏的缓存行相匹配。

缓存控制装置120还可以被配置为如果确定从计算单元110接收的存储指令中携带的地址与缓存130中被标记为脏的缓存行相匹配(也称为“命中”),则将存储指令中携带的数据(例如数据线170上的数据)写入该缓存行。

缓存控制装置120还可以被配置为基于数据被写入到缓存行中的区域,更新与缓存行相关联的覆盖掩码,覆盖掩码用于指示缓存行中的多个区域的写入状态。

在一些实施例中,覆盖掩码可以包括多个比特。覆盖掩码中的比特数量与缓存行中的区域数量相同。多个比特中的每个比特可以用于指示缓存行中的对应区域的写入状态。对于缓存130中的多个缓存行,可以存在多个覆盖掩码。覆盖掩码例如可以存储于缓存控制装置120内部,例如缓存控制装置120内的寄存器中,也可以存储于缓存130中,例如划出缓存130中的一部分用于存储覆盖掩码。

缓存行中的多个区域可以具有相同长度。长度例如为一个或多个字节。

作为一个示例,区域长度为一个字节。如图4所示,缓存行410可以具有128字节,也就是具有128个区域,覆盖掩码420可以具有128比特,覆盖掩码中的第i比特用于指示缓存行中的第i字节是否被写入,i大于等于1且小于等于128。

作为另一个示例,区域长度为双字节。如图5所示,缓存行510可以具有128字节,也就是具有64个区域,覆盖掩码520可以具有64比特,覆盖掩码中的第i比特用于指示缓存行中的第i个双字节(也就是第2i-1字节和第2i字节)是否被写入,i大于等于1且小于等于64。

在一些实施例中,缓存控制装置120可以被配置为确定数据被写入到缓存行中的区域,并且将覆盖掩码中与所确定的区域相对应的比特设置为预定值,例如1。

缓存控制装置120可以被配置为如果确定所更新的覆盖掩码已满,则将该缓存行中的数据写入(也称为驱逐)存储装置140,以及将该缓存行标记为有效。

在一些实施例中,缓存控制装置120还可以被配置为如果确定所更新的覆盖掩码中的多个比特均已被设置为预定值(例如1),则确定覆盖掩码已满。

由此,能够将缓存针对存储装置的写入流量进行平滑,在缓存刷新指令来到时极大地减少脏缓存行的数量,从而大大提高缓存刷新指令性能。

图2示出了根据本公开的实施例的用于缓存控制的方法200的示意图。例如,方法200可以由如图1所示的缓存控制装置120来执行。应当理解的是,方法200还可以包括未示出的附加框和/或可以省略所示出的框,本公开的范围在此方面不受限制。

在框202处,缓存控制装置120确定从计算单元110接收的存储指令中携带的地址与缓存130中被标记为脏的缓存行是否相匹配。

在一些实施例中,缓存控制装置120可以确定从计算单元110接收的存储指令中携带的地址与缓存130中的缓存行是否相匹配(也就是,地址是否命中缓存130中的缓存行),如果确定相匹配,则确定该缓存行是否被标记为脏,如果确定该缓存行被标记为脏(例如该缓存行的脏比特被设置为预定值,例如设置为1),则确定从计算单元110接收的存储指令中携带的地址与缓存130中被标记为脏的缓存行相匹配。

如果在框202处缓存控制装置120确定从计算单元110接收的存储指令中携带的地址与缓存130中被标记为脏的缓存行相匹配,则在框204处将存储指令中携带的数据写入该缓存行。

在框206处,缓存控制装置120基于数据被写入到缓存行中的区域,更新与缓存行相关联的覆盖掩码,覆盖掩码用于指示缓存行中的多个区域的写入状态。

在框208处,缓存控制装置120确定所更新的覆盖掩码是否已满。覆盖掩码已满也就表明了与该覆盖掩码相关联的缓存行已满。

在一些实施例中,缓存控制装置120可以确定所更新的覆盖掩码中的多个比特是否均已被设置为预定值,例如设置为1。如果缓存控制装置120确定所更新的覆盖掩码中的多个比特均已被设置为预定值,则确定覆盖掩码已满。

如果在框208处缓存控制装置120确定所更新的覆盖掩码已满,则在框210处将缓存行中的数据写入存储装置140,以及将缓存行标记为有效。

由此,能够将缓存针对存储装置的写入流量进行平滑,在缓存刷新指令来到时极大地减少脏缓存行的数量,从而大大提高缓存刷新指令性能。

图3示出了根据本公开的实施例的用于更新与缓存行相关联的覆盖掩码的方法300的示意图。例如,方法300可以由如图1所示的缓存控制装置120来执行。应当理解的是,方法300还可以包括未示出的附加框和/或可以省略所示出的框,本公开的范围在此方面不受限制。

在框302处,缓存控制装置120确定数据被写入到缓存行中的区域。这里被写入的区域可以是一个或多个。

在框304处,缓存控制装置120将覆盖掩码中与所确定的区域相对应的比特设置为预定值。

以区域长度是一个字节为例,如果数据被写入到缓存行中的第1-8字节,则将覆盖掩码中的第1-8比特设置为预定值,例如第1-8比特均设置为1。

以区域长度是双字节为例,如果数据被写入到缓存行中的第1-8字节,则将覆盖掩码中的第1-4比特设置为预定值,例如第1-4比特均设置为1。

由此,通过设置与区域相对应的比特值来更新覆盖掩码,以表示缓存行中的写入状态。

本领域技术人员可以理解,这里所描述的方法步骤不仅仅局限于附图中所示例性示出的顺序,而是可以按照任何其他可行的顺序来执行。

本文中以上描述的系统和技术的各种实施方式可以在数字电子电路系统、集成电路系统、场可编程门阵列(FPGA)、专用集成电路(ASIC)、专用标准产品(ASSP)、芯片上系统的系统(SOC)、负载可编程逻辑设备(CPLD)、计算机硬件、固件、软件、和/或它们的组合中实现。

本公开的以上描述用于使本领域的任何普通技术人员能够实现或使用本公开。对于本领域普通技术人员来说,本公开的各种修改都是显而易见的,并且本文定义的一般性原理也可以在不脱离本公开的精神和保护范围的情况下应用于其它变形。因此,本公开并不限于本文所述的实例和设计,而是与本文公开的原理和新颖性特性的最广范围相一致。

- 高速缓存控制器、控制高速缓存控制器的方法以及计算机系统

- 高速缓存控制器、高速缓存控制方法以及计算机系统