TDDB测试结构、TDDB测试系统及其测试方法

文献发布时间:2023-06-19 11:40:48

技术领域

本发明涉及半导体制造领域,特别涉及一种TDDB测试结构、TDDB测试系统及其测试方法。

背景技术

在半导体制造中,TDDB(Time Dependent Dielectric Breakdown,时间相关的电介质击穿)测试是一种重要的可靠性测试方法,可以用来预测半导体器件的使用寿命。

常规TDDB测试是在待测电介质样本的一端施加电压源,另一端接地端,持续监测通过待测电介质样本的电流,一旦待测电介质样本发生击穿引起电路短路,就会监测到突然跳变的大电流,记录此时的时间,就能评估出器件的使用寿命。

TDDB测试通常需要逐一对待测电介质样本进行测试。为了确保测试结果的统计学意义,同样类型的待测电介质样本数量一般为15个以上,而待测电介质样本又有多种类型,一次完整的TDDB测试耗时久,效率低。因此,需要一种能有效缩短测试时间的高效率的TDDB测试结构及其测试方法。

发明内容

本发明实施例提供了一种TDDB测试结构、TDDB测试系统及其测试方法,有效的缩短了测试时间,提高了测试效率。

为解决上述问题,本发明实施例提供一种TDDB测试结构,其特征在于,包括:在电压源和地端之间并联连接的多个测试单元,其中,所述多个测试单元的每一个包括:连接至所述地端的电介质测试样本,以及连接在所述电介质测试样本和所述电压源之间的控制模块,所述控制模块在使能信号下导通,在所述电介质测试样本击穿时关断。

可选的,所述电介质测试样本为电容器,所述电容器包括电介质。

可选的,所述控制模块包括:MOS晶体管,所述MOS晶体管包括用于加载使能信号的栅极、漏极以及连接至所述电介质测试样本的源极;连接在所述漏极与所述电压源之间的电阻器;连接在所述栅极与所述源极之间的延时单元,所述延时单元的输入端与所述源极连接,输出端与所述栅极连接。

可选的,所述延时单元是由偶数个反相器组成。

可选的,所述偶数个反相器串联连接。

可选的,所述电介质测试样本为N型测试样本,所述电压源用于提供正电压;或者,所述电介质测试样本为P型测试样本,所述电压源用于提供负电压。

可选的,所述多个测试单元的每个所述控制模块加载同一使能信号。

本发明实施例还提供一种TDDB测试系统,其特征在于,包括:如上所述的测试结构;与所述测试结构相连的电压源;向所述控制模块提供使能信号的使能信号源;以及连接在所述电压源和所述控制模块之间的检测设备,所述检测设备用于获得电压源和所述控制模块之间的电流-时间曲线。

可选的,所述检测设备是示波器。

本发明实施例还提供一种TDDB测试方法,其特征在于,包括:提供如上所述测试系统;向所述控制模块加载使能信号,使控制模块导通;通过检测设备测量电压源和所述控制模块之间的电流-时间曲线;根据电流增大时刻获得所述多个测试单元对应的多个击穿时间。

可选的,还包括:根据所述多个击穿时间,获得电介质测试样本中电介质的寿命。

与现有技术相比,本发明实施例的技术方案具有以下优点:

本发明实施例提供的技术方案中,在电压源和地端之间可以并联连接多个测试单元,其中,所述多个测试单元的每一个包括:连接至所述地端的电介质测试样本,以及连接在所述电介质测试样本和所述电压源之间的控制模块,所述控制模块在使能信号下导通,在所述电介质测试样本击穿时关断。当电介质测试样本击穿关断以后,其他测试单元的测试仍在继续。因此,可以同时测量多个测试单元,不需逐个进行测试,大大缩短了测试时间,提高了测试效率。

附图说明

图1是一种TDDB测试结构的示意图。

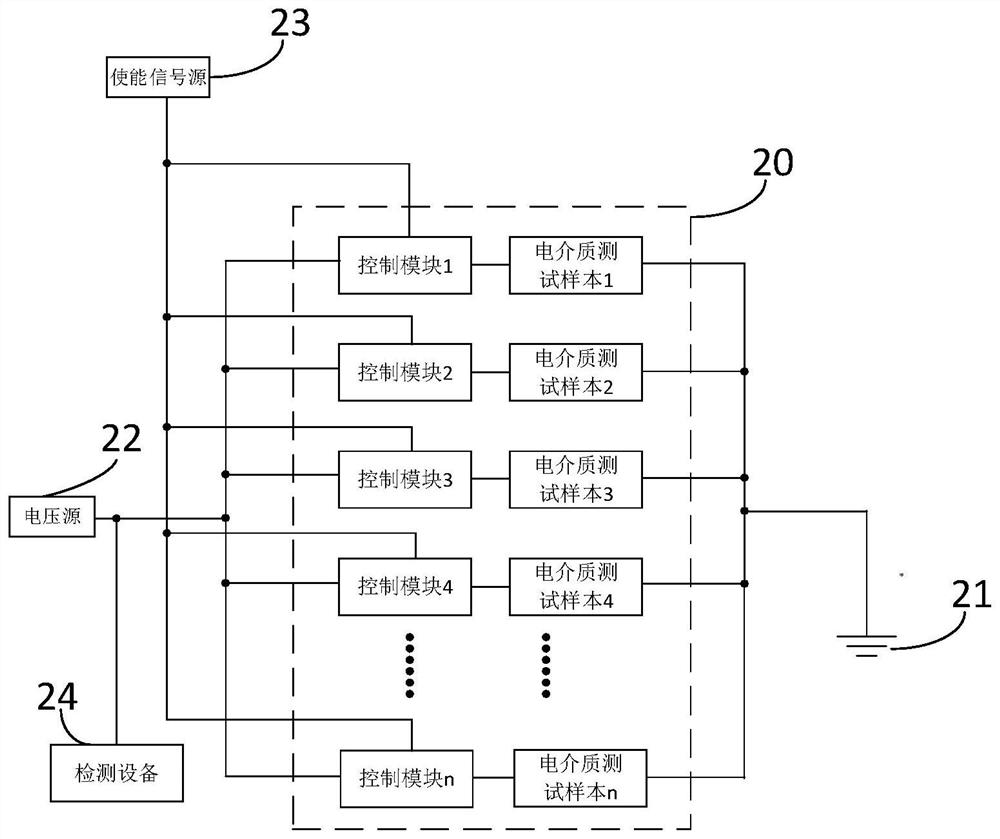

图2是本发明实施例的一种TDDB测试系统与测试结构示意图。

图3是本发明实施例的一种TDDB测试结构中的控制模块示意图。

图4是本发明实施例的一种TDDB测试结构下测试过程中的电流-时间曲线。

图5是本发明实施例的一种TDDB测试方法的流程图。

具体实施方式

由背景技术可知,现有技术中的TDDB测试结构及其测试方法耗时过久,效率有待提高。现结合TDDB测试结构及其方法分析问题的原因。

图1示出了一种TDDB测试结构的示意图。

参考图1,所述TDDB测试结构包括并联连接的多个测试单元10,所述多个测试单元10的每一个包括电介质测试样本,所述电介质测试样本的一端接地端,另一端接SMU(Source Measure Unit,源测量单元),每个所述电介质样本对应一个SMU。SMU给所述电介质样本施加持续电压并测量电流随时间变化,当所述电介质样本发生击穿时,电流跳变,此时将电流跳变时间记录为击穿时间。此时,TDDB测试受到测试仪中SMU的数量限制,通常测试仪中的SMU只有4~6个,因此只能同时测试4~6个所述电介质样本。然而,一次完整的TDDB测试需要测试的电介质样本数量较多,只能同时测试4~6个电介质样本导致测试耗时久,效率低。

为解决上述问题,本发明提供一种TDDB测试结构,包括:在电压源和地端之间并联连接的多个测试单元,其中,所述多个测试单元的每一个包括:连接至所述地端的电介质测试样本,以及连接在所述电介质测试样本和所述电压源之间的控制模块,所述控制模块在使能信号下导通,在所述电介质测试样本击穿时关断。当电介质测试样本击穿关断以后,其他测试单元的测试仍在继续。因此,可以同时测量多个测试单元,没有数量限制,不需逐个进行测试,大大缩短了测试时间,提高了测试效率。

为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

图2是本发明实施例的一种TDDB测试系统示意图。所述测试系统包括:测试结构,与所述测试结构相连的电压源22;向控制模块提供使能信号的使能信号源23;以及连接在所述电压源22和所述控制模块之间的检测设备24,所述检测设备24用于获得电压源22和所述控制模块之间的电流-时间曲线。

结合参考图3,示意了本发明实施例一种TDDB测试结构示意图,所述测试结构包括:在电压源22和地端21之间并联连接多个(N个)测试单元20,其中,所述多个测试单元20的每一个包括:连接至所述地端21的电介质测试样本,以及连接在所述电介质测试样本和所述电压源22之间的控制模块30,所述控制模块30在使能信号源23下导通,在所述电介质测试样本击穿时关断。

在本实施例中,所述电介质测试样本为电容器34,所述电容器34包括电介质,为本发明测试系统与测试结构的测试对象。在其他实施例中,所述电介质测试样本还可以是包括电介质的PN结电容器或MOS电容器等。

所述控制模块30包括:MOS晶体管31,所述MOS晶体管31包括连接至所述使能信号源23的栅极G、连接至所述电介质测试样本的源极S、以及漏极D。

所述MOS晶体管31在所述使能信号源23的作用下导通,使得所述电压源22提供的电压对所述电容器34进行充电,从而开始进行TDDB测试;经过一段时间的充电,当所述电容器34击穿时,所述电容器34中的介质层无法起到绝缘作用,从而产生短路大电流,通过记录所述短路大电流产生的时刻,可以获得电容器34的击穿时刻。这样,可以测试所述电容器34开始充电到所述电容器34击穿的时间,进而获得所述电容器中电介质层击穿寿命。

所述控制模块30还包括:连接在所述漏极D与所述电压源22之间的电阻器32,所述电阻器32起到分压作用,可以使得所述MOS晶体管31的所述源极S电平被拉低。

具体的,在TDDB测试刚刚开始的一段时间中,所述电阻器32的电阻相对于所述电容器34而言为可以忽略不计的小电阻,因此,所述电阻器32的分压作用较小。

当TDDB测试到一段时间使所述电容器34中的介质层击穿时,所述电容器34的电阻大幅度减小,此时,所述电阻器32的电阻器相对于所述电容器34而言为大电阻,可以起到较大的分压作用。

电压源22提供的电压被所述电阻器32分压之后,降低了所述MOS晶体管31的源极S的电平。

如图3所示,所述控制模块30还包括:连接在所述栅极G与所述源极S之间的延时单元33,其中所述源极S连接至所述延时单元33的输入端,所述栅极G连接至所述延时单元33的输出端。

电容器34中的介质层击穿时,经过电阻器32分压形成的低电平信号传输至所述延时单元33的输入端,所述低电平信号经过延时单元的延迟后到达所述MOS晶体管31的所述栅极G,使所述MOS晶体管31关断,进而使得所述电压源22与所述电容器34断开,当前测试单元的击穿测试单元的测试结束。

与此同时,电介质还未击穿的其他测试单元仍在继续测试,因此,本发明实施例可以同时测量多个测试单元,不需逐个进行测试,大大缩短了测试时间,提高了测试效率。

本实施例中,所述延时单元33包括两个串联的反相器,低电平信号经过一次反向,又经过一次反向之后仍然为低电平信号。到达所述MOS晶体管31的所述栅极G的低电平小于所述MOS晶体管31的开启电压,因此,所述MOS晶体管31被关断。

需要说明的是,在本发明的其他实施例中,所述延时单元33还可以由其他偶数个反相器组成,并均是串联连接的。所述偶数个反相器串起到整形和延时功能。

继续参考图2,本实施例TDD测试系统还包括:

电压源22,用于向提供恒定电压。

具体地,所述电介质测试样本为N型测试样本,所述电压源用于提供正电压;或者,所述电介质测试样本为P型测试样本,所述电压源用于提供负电压。

使能信号源23,用于控制所述控制模块,使其处于导通状态,本实施例中,所述控制模块包括MOS管,所述使能信号为电压信号,具体的,所述使能信号源提供的电压大于所述MOS管的开启电压。

在其他实施例中,所述控制模块还可以是电流控制模块,具体地,所述使能信号还可以为电流信号。

本实施例TDDB测试系统还包括:检测设备24,所述检测设备24用于测量所述电压源22和所述地端21之间的电流-时间曲线。

参考图4,图4为本发明实施例TDDB测试结构获得的电流-时间曲线。其中横坐标为时间,纵坐标为电流信号强度。

如图4所示,随着时间的变化,曲线中会有电流信号突然增大的时刻TBD1、TBD2、TBD3……TBDN,产生瞬时大电流的时刻即为其中一测试结构的电介质被击穿的时刻。

本实施例中,所述检测设备24为滤波器,滤波器为常用信号观测仪器,除了可以形成电流电压数据外,还可以通过滤波器显示屏幕对信号的变化进行观察。

参考图2和图3,所述多个测试单元20的每个所述控制模块共用一个所述使能信号源23。本发明提供的TDDB测试系统包含一个所述电压源22,一个所述使能信号源23,一个所述检测设备24,不需要更换其他设备,节省了测试时间,提高了测试效率。

相应的,本发明还提供一种TDDB测试方法,图5示出了本发明实施例的一种TDDB测试方法的流程图。

参考图5,基于如上所述测试系统的测试方法,包括:

步骤50,向所述控制模块加载使能信号,使控制模块导通;

步骤51,通过检测设备测量电压源和所述控制模块之间的电流-时间曲线;

步骤52,根据电流增大时刻获得所述多个测试单元对应的多个击穿时间。

下面结合图2、图3及图4,具体说明本实施例测试方法的流程:

首先,通过使能信号源23向所述控制模块加载使能信号,使所述控制模块导通;具体的,所述控制模块30包括:MOS晶体管31,所述MOS晶体管31包括连接至所述使能信号源23的栅极G、连接至所述电介质测试样本的源极S、以及漏极D。所述使能信号源23提供的电压大于所述MOS管的开启电压,因此,所述MOS晶体管导通,使得所述电压源22提供的电压对所述电容器34进行充电。

具体的,所述控制模块30还包括:连接在所述漏极D与所述电压源22之间的电阻器32,在TDDB测试刚刚开始的一段时间中,所述电阻器32的电阻相对于所述电容器34的电阻而言为可以忽略不计的小电阻,因此,所述电阻器32的分压作用非常微小,不影响加载到所述电容器34上的电压。

在加载所述使能信号的同时,开始通过检测设备24测量电压源22和所述控制模块30之间的电流-时间之间的关系;经过一段时间的充电,当所述电容器34击穿时,根据电流增大时刻获得所述多个测试单元20对应的多个击穿时间。

具体的,当所述电容器34被击穿时,所述电容器34中的介质层无法起到绝缘作用,从而产生短路大电流,此时,所述电阻器32的电阻器相对于所述电容器34而言为大电阻,可以起到较大的分压作用,可以使得所述MOS晶体管31的所述源极S电平被拉低。

如图3所示,所述控制模块还包括:连接在所述栅极G与所述源极S之间的延时单元33,其中所述源极S连接至所述延时单元33的输入端,所述栅极G连接至所述延时单元33的输出端。本实施例中,所述延时单元33包括两个串联的反相器,低电平信号经过一次反向,又经过一次反向之后仍然为低电平信号。两个反相器传亮起到了整形和延时的功能,使得所述源极S的低电平信号经过延时单元33的延迟后到达所述MOS晶体管31的所述栅极G,所述低电平信号低于所述MOS晶体管31的开启电压,因此所述MOS晶体管31关断,进而使得所述电压源22与所述电容器34断开,当前测试单元的击穿测试单元的测试结束。

本实施例中,利用示波器测量所述电压源22与所述地端21之间的电流-时间曲线。参考图4,曲线中会有电流信号突然增大的时刻TBD1、TBD2、TBD3……TBDN,产生瞬时大电流的时刻即为其中一测试结构的电介质被击穿的时刻,获得所述多个击穿时间,通过统计学方法获得电介质测试样本中电介质的寿命。

综上,本发明方案中的所述控制模块在使能信号源下导通,在所述电介质测试样本击穿时关断。当电介质测试样本击穿关断以后,其他测试单元的测试仍在继续测量。因此,可以同时测量多个测试单元,没有数量限制,不需逐个进行测试,大大缩短了测试时间,提高了测试效率。

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

- TDDB测试结构、TDDB测试系统及其测试方法

- 用于评估栅氧层TDDB极性差异的测试结构及测试方法