一种实现干扰滤除功能的电路模块和集成电路系统

文献发布时间:2023-06-19 11:45:49

技术领域

本发明涉及信号干扰消除技术领域,尤其涉及一种实现干扰滤除功能的电路模块和集成电路系统。

背景技术

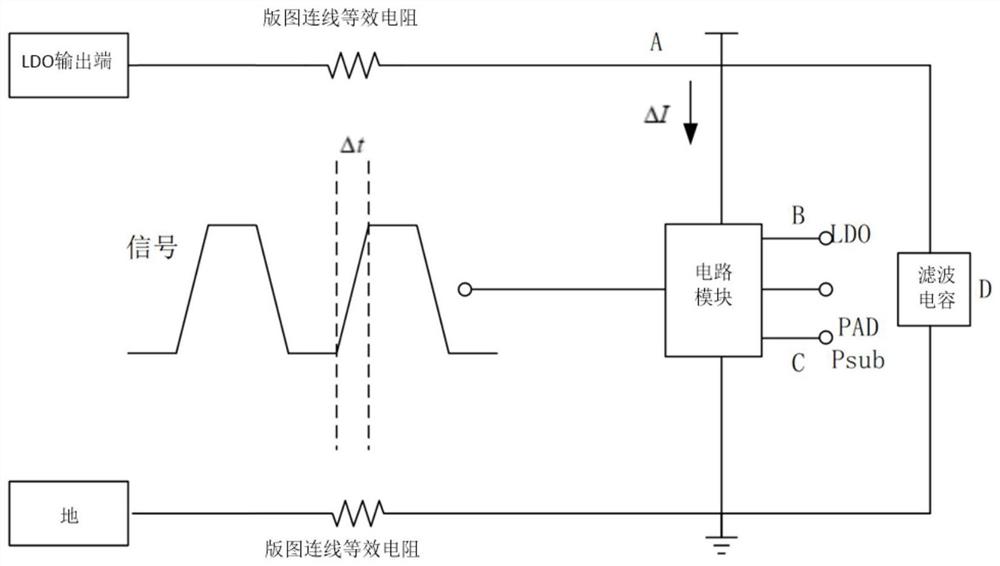

传统的电路模块框图如图1所示,电路模块的第一端连接上一级电路即LDO(低压差线性稳压器)的输出端,电路模块的另一端接地,电路模块还有一信号输入端,信号输入端若输入的是非理想的方波信号,例如图2所示的一种实例电路模块,方波信号上升沿缓慢上升,下降沿缓慢下降,当信号缓慢上升和缓慢下降经过MP1(P型氧化物半导体)和MN1(N型氧化物半导体)时,会导致MP1和MN1打开,产生一个瞬间电流,由于LDO驱动能力有限,在电路模块的第一端即A点会产生干扰。当MP1和MN1的沟道长度和宽度越大,产生的瞬间电流越大,产生的干扰就越大,产生的干扰会通过电源、地和衬底等干扰到集成在一起的其它模块的性能,并且还会影响到自身的电路性能和功能。

发明内容

本发明提供一种实现干扰滤除功能的电路模块和集成电路系统,旨在解决不增加成本和不影响性能的前提下滤除干扰等技术问题。

一种实现干扰滤除功能的电路模块,电路模块的第一端与上一级的低压差线稳压器的输出端连接,电路模块的第二端接地,电路模块具有至少一PMOS器件;其特征在于,PMOS器件的衬底分别与低压差线稳压器的输出端连接。

进一步的,电路模块还至少包括一个NMOS器件,NMOS器件的衬底分别连接一接触垫。

进一步的,接触垫安装在电路模块所在的底板上。

进一步的,电路模块还包括:

一滤波电容,滤波电容连接在电路模块的第一端和第二端之间。

进一步的,滤波电容靠近电路模块安装。

进一步的,电路模块是反相器或者触发器。

一种集成电路系统,其特征在于,包括如前述的一种实现干扰滤除功能的电路模块。

本发明的有益技术效果:本发明在不增加成本的情况下,减少了电路模块的干扰源,提高电路模块的性能。

附图说明

图1为现有技术中电路模块的框图结构;

图2为现有技术中一种具体实施方式的电路模块的框图结构;

图3为本发明中电路模块的框图结构;

图4为本发明中一种具体实施方式的电路模块的框图结构。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

下面结合附图和具体实施例对本发明作进一步说明,但不作为本发明的限定。

参见图3-4,本发明提供一种实现干扰滤除功能的电路模块,电路模块的第一端与上一级的低压差线稳压器的输出端连接,电路模块的第二端接地,电路模块具有至少一PMOS器件;其特征在于,PMOS器件的衬底分别与低压差线稳压器的输出端连接。

进一步的,电路模块还至少包括一个NMOS器件,NMOS器件的衬底分别连接一接触垫。

进一步的,接触垫安装在电路模块所在的底板上。

进一步的,电路模块还包括:

一滤波电容,滤波电容连接在电路模块的第一端和第二端之间。

进一步的,滤波电容靠近电路模块安装。

进一步的,电路模块是逻辑电路。

进一步的,电路模块是反相器或者触发器。

本发明还提供一种集成电路系统,其特征在于,包括如前述的一种实现干扰滤除功能的电路模块。

进一步的,PMOS器件为耗尽型。

进一步的,NMOS器件为耗尽型。

如图2所示,假设方波信号中缓慢上升和缓慢下降的时间为Δt,MP1和MN1打开的同时时会产生一个瞬间电流为ΔI,在A点产生的干扰为Δv:

其中,C

ΔV

C

其中,C

W是指MP1或者MN1的沟道的宽度;

L是指MP1或者MN1的沟道的长度。

结合上述公式可知:

可见,电路模块中产生的瞬间电流ΔI与MOS管沟道的长度、宽度、电压差以及上升或者下降的时间有关。

如果非理想的方波信号中上升或下降的时间的Δt不变,W、L越大产生的瞬间电流越大,在做版图时导线存在寄生电容R

Δv=ΔI×R

因此,

产生的干扰比较大时,会通过电源、地和衬底等影响到集成在一起的其它模块的性能,并且还会影响到自身的电路性能和功能。

如图3-4所示,本发明通过在将PMOS管的N衬底连接到LDO的输出端,为NMOS管的P衬底Psub额外增加一个接触垫PAD与之接触,PAD直接封装在底板上,避免与集成电路内部的衬底之间的接触。此外,在电路模块增加一个滤波电容,通过控制滤波电容的大小实现抑制和滤除干扰效果,

做版图时由于导线会存在寄生电阻R固定,结合公式4和6可知:

对比加完滤波电容的前后效果,由公式5和公式6可知:

由公式8可知,Δv

因此,本发明通过为电路模块增加滤波电容,预先在电路模块附近存储一定电荷,在电路模块需要瞬间补充或者泄放电荷时,由滤波电容进行补充或者泄放电荷,避免了电路模块上的干扰。

本发明的电路模块可以是逻辑电路,包括简单逻辑电路例如与门、非门、或门等。通过本发明的三种手段将干扰滤除,在不增加集成电路的成本的情况下尽可能的滤除干扰,提高电路模块的性能,集成电路集成了大规模的电路模块时,减少模块和模块之间的干扰。

以上仅为本发明较佳的实施例,并非因此限制本发明的实施方式及保护范围,对于本领域技术人员而言,应当能够意识到凡运用本发明说明书及图示内容所作出的等同替换和显而易见的变化所得到的方案,均应当包含在本发明的保护范围内。

- 一种实现干扰滤除功能的电路模块和集成电路系统

- 在集成电路芯片上实现信号处理功能的方法及逻辑模块