半导体结构及其制造方法和存储器

文献发布时间:2023-06-19 12:21:13

技术领域

本申请涉及半导体领域,具体涉及一种半导体结构及其制造方法和存储器。

背景技术

随着技术进步和需求增长,如电脑等的电子产品通常需要大容量的存储器,例如动态随机存储器。为了提高存储器可存储容量,存储器内部的存储单元尺寸越来越小。半导体结构一般是以在衬底上定义出的有源层为基础,往上形成不同层的元件结构。以存储器的存储单元为例,多个元件单元会在预定的元件区域以规则排列的方式构成阵列,一个元件单元最后形成一个存储单元,此外,在存储单元周围还有周边电路。由于半导体元件排列十分紧密,产生的应力等可能导致元件和周边电路损坏。

发明内容

为解决上述现有技术的问题,本申请提供一种能够克服或改善现有技术问题的半导体结构及其制造方法和存储器。

本申请的一个方面提供一种半导体结构,包括衬底、有源层和绝缘层。所述有源层位于所述衬底上,包括元件结构和围绕所述元件结构的边界结构,所述元件结构包括多个间隔设置的元件单元,所述边界结构包括边界部、从所述边界部向内凸起的凸出部和分支部。所述绝缘层包括位于所述边界结构内的第一绝缘结构和位于所述边界结构外侧的第二绝缘结构,所述第一绝缘结构设置在所述多个元件单元和所述边界结构之间以使所述多个元件单元之间绝缘,所述第二绝缘结构用于将所述边界结构和外部的有源区域之间绝缘。在平行于所述边界部和所述凸出部相连的一侧的边缘的方向上,所述分支部的宽度小于所述凸出部的宽度。

本申请的一些实施例中,所述元件单元具有朝向预设方向延伸的条状结构,所述分支部具有朝向所述预设方向延伸的条状结构,多个所述元件单元以及所述分支部间隔地设置在平行于所述预设方向的一条或多条直线上,所述预设方向和所述边界部的边缘所在方向不相平行。

本申请的一些实施例中,在垂直于所述预设方向的方向上,所述元件单元的宽度和所述分支部的宽度相等,或所述元件单元的宽度小于所述分支部的宽度,或所述元件单元的宽度大于所述分支部的宽度。

本申请的一些实施例中,在和所述预设方向垂直的方向上,相邻的元件单元之间交错设置,所述分支部和邻近的所述元件单元交错设置。

本申请的一些实施例中,所述分支部中的一个或多个和所述凸出部相连接,或,所述凸出部中的一个或多个和所述分支部连接。

本申请的一些实施例中,所述分支部包括连接所述边界部的第一分支部和连接所述凸出部的第二分支部。

本申请的一些实施例中,所述凸出部和所述分支部邻近所述边界部的相对的两侧设置,在同一侧边界部上,所述第一分支部和所述第二分支部交替设置;或所述第二分支部间隔设置。

本申请的一些实施例中,所述第一分支部沿预设方向的长度大于或等于所述第二分支部沿预设方向的长度。

本申请的一些实施例中,在预设方向上,所述第二分支部在所述边界部的相对两侧交错设置。

本申请的一些实施例中,所述凸出部沿所述预设方向延伸。

本申请的一些实施例中,在垂直于所述边界部和所述凸出部相连的一侧的边缘的方向上,所述边界部的宽度小于或等于所述凸出部的宽度。

本申请的一些实施例中,所述边界部是连续围绕所述多个元件单元;或所述边界部包括多个具有间隔的子边界部,所述多个子边界部共同围绕所述多个元件单元,所述凸出部和所述子边界部相连。

本申请的一些实施例中,所述元件单元和所述边界结构间隔设置。

本申请的一些实施例中,所述绝缘层包括沟道绝缘层。

本申请的一个方面提供一种半导体结构的制造方法,包括:提供一衬底;图案化所述衬底的顶部,以形成一有缘层,所述有源层包括元件结构和围绕所述元件结构的边界结构,所述元件结构包括多个间隔设置的元件单元,所述边界结构包括边界部、从所述边界部向内凸起的凸出部和分支部;其中,在平行于所述边界部和所述凸出部相连的一侧的边缘的方向上,所述分支部的宽度小于所述凸出部的宽度;形成一绝缘层,所述绝缘层包括位于边界结构内的第一绝缘结构和位于所述边界结构外侧的第二绝缘结构,所述第一绝缘结构设置在所述多个元件单元和所述边界结构之间以使所述多个元件单元之间绝缘,所述第二绝缘结构用于将所述边界结构和外部的有源区域之间绝缘。

本申请的一个方面提供一种存储器,包括上述的半导体结构。本申请的半导体结构及其制造方法和存储器通过在边界部设置凸出部和分支部,能够较好阻挡外部绝缘层产生的应力,并且还能够较好减少元件单元之间在端部产生的应力不均。

附图说明

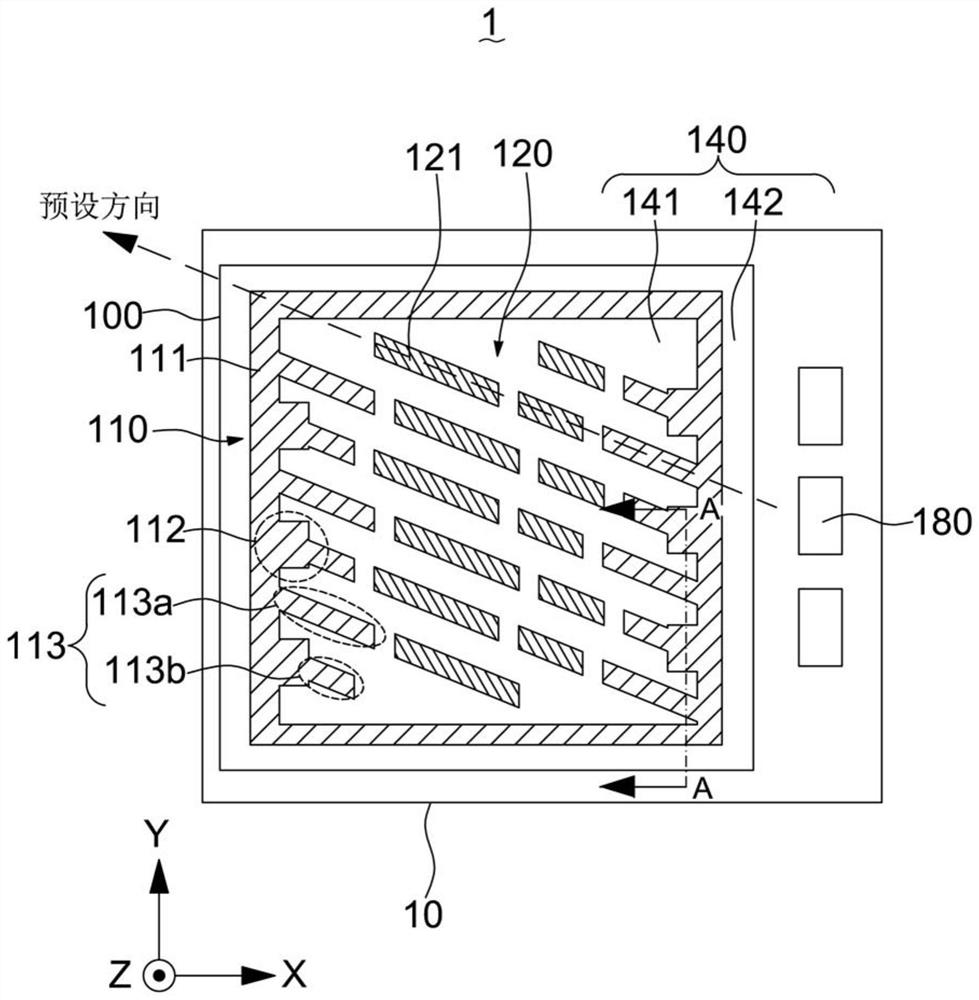

图1是根据本申请的一个实施例的半导体结构的部分俯视示意图;

图2是图1所示的半导体结构的沿A-A线的截面示意图;

图3是本申请的半导体结构的一个实施例的部分俯视示意图;

图4是本申请的半导体结构的一个实施例的部分俯视示意图;

图5是本申请一种半导体结构的制造方法的一个实施例的流程示意图。

具体实施方式

为了使本申请的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本申请进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本申请,并不用于限定本申请。

在本申请的描述中,需要说明的是,除非另有明确的规定或限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体化连接;可以是机械连接,也可以是电连接或相互通信;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件之间的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本申请中的具体含义。本申请的公开提供了许多不同的实施方式或示例用来实现本申请的不同结构。为了简化本申请的公开,下文仅对特定例子的部件和设定进行描述。当然,它们仅仅为示例,并且目的不在于限制本申请。此外,本申请可以在不同例子中重复使用参考数字和/或参考字母,这种重复使用是为了简化和清楚地表述本发明,其本身不指示所讨论的各种实施方式和/或设定之间的特定关系。

请参阅图1,是根据本申请的一个实施例的半导体结构1的部分俯视示意图。请一并参阅图2,是图1所示的半导体结构1的沿A-A线的截面示意图。

所述半导体结构1包括衬底10、有源层100和绝缘层140。所述有源层100位于所述衬底10上,其包括元件结构120和围绕所述元件120 结构的边界结构110。所述元件结构120包括多个间隔设置的元件单元121,所述边界结构110包括边界部111、从所述边界部111向内凸起的凸出部112和分支部113。一些实施例中,所述有源层100实际是由所述衬底10的顶部经过图案化而形成。

所述绝缘层140包括位于所述边界结构110的内侧的第一绝缘结构 141和位于所述边界结构110的外侧的第二绝缘结构142。例如但不限于地,所述边界结构110的靠近所述元件单元121的一侧为所述边界结构110的内侧,所述边界结构110的远离所述元件单元121的一侧为所述边界结构110的外侧。所述第一绝缘结构141设置在所述多个元件单元121和所述边界结构110之间,以使所述多个元件单元121之间彼此绝缘。所述第二绝缘结构142可以用于将所述边界结构110和外部的有源区域180之间绝缘。在平行于所述边界部111与所述凸出部112相连的一侧的边缘的方向上,所述分支部113的宽度小于所述凸出部112的宽度。

可选地,在一些实施例中,所述第一绝缘结构141和第二绝缘结构 142可以例如但不限于为氧化硅或其他绝缘材料。

示例而非限定地,图1中所示Y方向可以为平行于所述边界部111 与所述凸出部112相连的一侧的边缘的方向。所述边界部111的沿X方向的两侧与所述凸出部112相连。图1中A-A线可以为平行于所述边界部111与所述凸出部112相连的一侧的边缘的方向。。

本申请的实施例中,所述元件单元121具有朝向预设方向延伸的条状结构,所述分支部113同样具有朝向所述预设方向延伸的条状结构。多个所述元件单元121以及所述分支部113间隔地设置在平行于所述预设方向的一条或多条直线上,所述预设方向和所述边界部111的边缘所在方向不相平行。

可选地,一些实施例中,在垂直于所述预设方向的方向上,所述元件单元121的宽度和所述分支部113的宽度大致相等。当然,可变更地,本申请的一些实施例中,所述元件单元121的宽度可以小于所述分支部 113的宽度,或所述元件单元121的宽度可以大于所述分支部113的宽度。本申请的实施例对此不作限定。

可选地,一些实施例中,在和所述预设方向垂直的方向上,相邻的元件单元121之间交错设置,且,所述分支部113和邻近的所述元件单元121交错设置。

可选地,一些实施例中,所述分支部113中的一个或多个和所述凸出部112相连接。另一些实施例中,所述凸出部112中的一个或多个和所述分支部113连接。如图1所示,所述分支部113包括第一分支部113a 和第二分支部113b,所述第一分支部113a连接所述边界部111,所述第二分支部113b连接所述凸出部112。进一步地,所述第二分支部113b 可以由所述凸出部112的部分朝向所述边界部111的内侧沿所述预设方向延伸。由于截面位置关系,图2所示截面图出仅示意出了第一分支部 113a。

所述凸出部112和所述分支部113设置在所述边界部111的相对的两侧。可选地,在一些实施例中,在同一侧的边界部111上,所述第一分支部113a和所述第二分支部113b交替设置。

可选地,在一些实施例中,在同一侧的边界部111上,第二分支部 113b间隔设置,位于所述边界部111的同一侧的相邻的两个第二分支部 113b之间可以设置多个所述第一分支部113a。

本申请实施例中,所示元件单元121和所示边界结构100是间隔设置的,所述第一绝缘结构141设置在所述元件单元121之间以及所述元件单元121和所述边界结构100之间。

本实施例中所述的半导体结构1通过在边界部111内侧设置凸出部 112和分支部113,能够较好阻挡外围大区域的浅沟道绝缘层(第二绝缘结构142)所产生的应力作用,并且还能够较好减少有源层(元件单元121)之间在端部产生的应力不均。示例而非限定地,所述边界部111 在垂直于所述边界部111和所述凸出部112相连的一侧的边缘的方向上,所述边界部111的宽度小于或等于所述凸出部112的宽度。

可选地,在一些实施例中,在所述预设方向上,所述凸出部112和与其连接的第二分支部113b在所述边界部111的相对两侧交错设置,从而分别连接在所述边界部111的两侧的第二分支部113b不会位于平行于所述预设方向的同一条直线上。这样的话,在保证较好应力阻挡效果的时候可以获得较高的元件密度。

本申请实施例中,所述第一分支部113a沿所述预设方向的长度大于或等于所述第二分支部113b沿所述预设方向的长度。这样的话,所述第一分支部113a和相邻的所述凸出部112、第二分支部113b之间可以具有较好的应力平衡。

请参阅图3,是本申请的半导体结构的一个实施例的部分俯视示意图。图3所示的实施例和图1所示的实施例在结构上基本相同,主要区别在于,所述边界部111的部分沿平行于所述预设方向的直线向内凸出形成所述凸出部112,也即所述凸出部112沿所述预设方向延伸。所述凸出部112的和所述边界部111相连的边缘平行于所述预设方向。

请参阅图4,是本申请的半导体结构的一个实施例的部分俯视示意图。图4所示的实施例和图3所示的实施例在结构上基本相同,主要区别在于,图3中所示的实施例的边界部111是连续围绕所述多个元件单元121;图4所示的实施例中,边界结构110包括多个具有间隔的子边界部111a,所述多个子边界部111a共同围绕所述多个元件单元121。由于采用多个子边界部111a,对于浅沟道绝缘层所述产生的应力能够起到较好的阻挡。

进一步地,应当理解,对于凸出部112的不经过创造性劳动的变形、替换、扩展、增删等得到的实施例,均属于本申请保护范围。

请参阅图5,本申请提供了一种半导体结构的制造方法。所述半导体结构的制造方法包括:

步骤S1,提供一衬底。所述衬底可以为半导体衬底。

步骤S2,图案化所述衬底的顶部,以形成一有缘层,所述有源层包括元件结构和围绕所述元件结构的边界结构,所述元件结构包括多个间隔设置的元件单元,所述边界结构包括边界部、从所述边界部向内凸起的凸出部和分支部;其中,在平行于所述边界部和所述凸出部相连的一侧的边缘的方向上,所述分支部的宽度小于所述凸出部的宽度。

步骤S3,形成一绝缘层,所述绝缘层包括位于边界结构内的第一绝缘结构和位于所述边界结构外侧的第二绝缘结构,所述第一绝缘结构设置在所述多个元件单元和所述边界结构之间以使所述多个元件单元之间绝缘,所述第二绝缘结构用于将所述边界结构和外部的有源区域之间绝缘。

采用本申请的半导体结构的制造方法的半导体结构能够较好的减少应力不均造成的器件损坏。本申请还提供一种存储器,包括本申请实施例所述的半导体结构。所述存储器例如但不限于为动态随机存取存储器(Dynamic Random Access Memory,DRAM)。由于所述半导体结构具有较好的抗应力性,因此本申请的存储器具有较好的可靠性。尽管已经相对于一个或多个实现方式示出并描述了本申请,但是本领域技术人员基于对本说明书和附图的阅读和理解将会想到等价变型和修改。本申请包括所有这样的修改和变型,并且仅由所附权利要求的范围限制。特别地关于由上述组件执行的各种功能,用于描述这样的组件的术语旨在对应于执行所述组件的指定功能(例如其在功能上是等价的)的任意组件(除非另外指示),即使在结构上与执行本文所示的本说明书的示范性实现方式中的功能的公开结构不等同。此外,尽管本说明书的特定特征已经相对于若干实现方式中的仅一个被公开,但是这种特征可以与如可以对给定或特定应用而言是期望和有利的其他实现方式的一个或多个其他特征组合。进一步地,应当理解的是,在本文中提及的“多个”是指两个或两个以上。对于本文中提及的步骤,其通过数字后缀仅仅是为了清晰表述实施例,便于理解,并不完全代表步骤执行的先后顺序,应当以逻辑关系的先后设定为思考。

以上所述仅为本申请的实施例,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所作的等效结构或等效流程变换,例如各实施例之间技术特征的相互结合,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。

- 非易失性半导体存储器晶体管、非易失性半导体存储器及非易失性半导体存储器的制造方法

- 强电介质膜的形成方法、强电介质存储器、强电介质存储器的制造方法、半导体装置及半导体装置制造方法