一种双向稳压静电浪涌全芯片保护集成电路

文献发布时间:2023-06-19 10:24:22

技术领域

本发明涉及集成电路的静电放电防护及抗浪涌领域,具体涉及一种双向稳压静电浪涌全芯片保护集成电路。

背景技术

电子产品在使用过程中,静电放电或浪涌是使其失效的主要原因。随着集成电路按缩比规律向超深亚微米及纳米方向发展,器件栅氧化物越来越薄,沟道长度越来越短,集成电路对静电与浪涌的损伤越来越敏感。根据对电子产品失效机理的分析统计,一半以上电子元件的失效是由浪涌(EOS)和静电放电(ESD)引起。尤其伴随集成电路制造工艺的不断发展以及电子系统复杂度的不断提升,多系统集成复杂SOC的EOS/ESD防护需求日益增多,集成电路的EOS/ESD防护设计难度也在不断的增大。

电子产品在实际应用过程中,在IC内部或板级电路的I/O端、电源或热插拔接口都有可能遭受ESD或EOS损伤,由于ESD或EOS放电方向具有不确定性,通常需要对IC内部或板级电路的相应端口设计具有正反向ESD或EOS抑制功能的电路保护单元。

目前常见EOS/ESD的基本保护单元主要有二极管(Diode)、双极型晶体管(BJT)、金属氧化物半导体场效应晶体管(MOSFET)、横向与纵向扩散MOSFET(LDMOS/VDMOS)以及可控硅整流器(SCR)等。SCR作为单向的防护器件,虽然具有结构简单,快速导通,强鲁棒性的突出特点,但其在反向ESD作用下仅表现为一个普通二极管,传统单向的ESD/TVS保护网络已不能广泛为IC以及板级电路的I/O端、电源或热插拔接口提供全模式的EOS/ESD防护功能。

发明内容

鉴于背景技术的不足,本发明是提供了一种双向稳压静电浪涌全芯片保护集成电路,所要解决的技术问题是现有单向ESD防护应用中器件占用芯片面积过大,防护效能低下的状况,不能为IC以及板级电路的I/O端、电源或热插拔接口提供全模式的EOS/ESD防护功能。

为解决以上技术问题,本发明提供了如下技术方案:

实施方式一,一种双向稳压静电浪涌全芯片保护集成电路,包括P型衬底,P型衬底的上表面分别设有第一P阱、第一N阱和第二N阱,第一P阱的左侧面与第一N阱的右侧面连接,第一N阱的左侧面与P型衬底的左侧面齐平,第一N阱上设有第一P+注入区,第一P+注入区的右侧间隔设有第一N+注入区,第一N+注入区分别在第一N阱和第一P阱上;

第一P阱的右侧面与第二N阱的左侧面连接,第二N阱的右侧面与P型衬底的右侧面齐平,第二N阱上设有第五P+注入区,第五P+注入区的左侧间隔设有第三N+注入区,第三N+注入区分别在第一P阱和第二N阱上;

第一P阱在第一N+注入区和第三N+注入区之间设有第二P+注入环。

实施方式二,在实施方式一的基础上,第一N阱和第二N阱在第二P+注入环的两侧对称设置。

实施方式三,在实施方式二的基础上,第一P+注入区和第五P+注入区在第二P+注入环的两侧对称设置。

实施方式四,在实施方式三的基础上,第二P+注入环的左侧面与第一N+注入区的右侧面的间距和第二P+注入环的右侧面与第三N+注入区的左侧面的间距相同。

实施方式五,在实施方式一至四任一种实施方式的基础上,第三P阱在第二P+注入环内设有第三N阱,第三N阱上沿纵向设有工字型的第二N+注入区,第三N阱在第二N+注入区的两横部之间设有第三P+注入区和第四P+注入区,第三P+注入区和第四P+注入区关于第二N+注入区的纵部对称设置。

实施方式六,在实施方式一至四任一种实施方式的基础上,第三P阱在第二P+注入环内分别设有第三N阱和第一N+注入环,第一N+注入环分别在第三N阱和第一P阱上,第三N阱在第一N+注入环内设有第六P+注入区,第六P+注入区的左侧面与第一N+注入环的间距和第六P+注入区的右侧面与第一N+注入环的间距相同,第六P+注入区的前侧面与第一N+注入环的间距和第六P+注入区的后侧面与第一N+注入环的间距相同。

实施方式七,在实施方式一至四任一种实施方式的基础上,第三P阱在第二P+注入环内设有第三N阱,第三N阱在第二P+注入环内沿横向设有日字型的第四N+注入区,第四N+注入区的四侧边分别在第三P阱和第三N阱上,第四N+注入区的左N+环和右N+环对称设置,第三N阱在左N+环内设有第七P+注入区、在右N+环内设有第八P+注入区,第七P+注入区和第八P+注入区对称设置。

实施方式八,在实施方式一至三任一种实施方式的基础上,第一N+注入区为L型形状,第一N+注入区的纵部分别在第一N阱和第一P阱上,第三N+注入区为倒L型形状,第三N+注入区的纵部分别在第二N阱和第一P阱上;第一P阱在第一N+注入区的横部与第三N+注入区的纵部之间设有第九P+注入区、在第二N+注入区的横部与第一N+注入区的纵部之间设有第十P+注入区,第九P+注入区的后侧面与第二P+注入环的前侧面连接,第十P+注入区的前侧面与第二P+注入环的后侧面连接;第二P+注入环的左侧面与第一N+注入区的纵部的间距和第二P+注入环的右侧面与第三N+注入区的纵部的间距相同,第二P+注入环的前侧面与第一N+注入区的横部的间距和第二P+注入环的后侧面与第三N+注入区的横部的间距相同;第三P阱在第二P+注入环内分别设有第三N阱和第一N+注入环,第一N+注入环分别在第三N阱和第一P阱上,第三N阱在第一N+注入环内设有第六P+注入区,第六P+注入区的左侧面与第一N+注入环的间距和第六P+注入区的右侧面与第一N+注入环的间距相同,第六P+注入区的前侧面与第一N+注入环的间距和第六P+注入区的后侧面与第一N+注入环的间距相同。

本发明与现有技术相比所具有的有益效果是:在实施方式一中,第一P+注入区、第一N阱和第一P阱103构成PNP管T1,第一N阱102、第一P阱103、第二N阱105和第三N+注入区112构成NPN管T2,PNP管T1和NPN管T2构成SCR结构的正反馈网络,提高双向稳压静电浪涌全芯片保护IC EOS/ESD鲁棒性。另外第一N+注入区107和第二P+注入环108构成稳压二极管D1,第一P阱103和第三N+注入区112构成正偏二极管D2,稳压二极管D1与正偏二极管D2形成稳压二极管触发路径,可调控双向稳压静电浪涌全芯片保护IC的工作电压及其电压拑制能力。

在实施方式五中,第一N阱102、第一P阱103、第三N阱104和第二工形N+注入区110构成NPN管T3,PNP管T1和NPN管T3构成的SCR结构的正反馈网络,提高了双向稳压静电浪涌全芯片保护IC的VSS至I/O端的电流泄放能力,第一P阱103、第二P+注入环108和第二工形N+注入区110构成正偏二极管D3,稳压二极管D1与正偏二极管D3形成稳压二极管触发路径,稳压二极管触发路径与SCR路径并联,降低了双向稳压静电浪涌全芯片保护IC的寄生电容,提高ESD/EOS鲁棒性;另外第三P+注入区109、第三N阱104、第一P阱103构成PNP管T4,第四P+注入区111、第三N阱104、第一P阱103构成PNP管T5,PNP管T4、T5并联,且与NPN管T3组成的正反馈网络构成SCR电流泄放路径,降低寄生电容并提高ESD/EOS鲁棒性。

在实施方式六中,第一N+注入环301与第二P+注入环108之间形成的稳压二极管,可增强I/O到VSS,以及I/O到VDD之间的电压钳制能力,增强双向稳压静电浪涌全芯片保护IC的EOS/ESD鲁棒性。

在实施方式七中,日字型的第四N+注入区401、第七P+注入区402和第八P+注入区403形成两个并接的PNP型三极管,可以增强电流导通均匀性和电压钳制能力。

在实施方式八中,由于第三N+注入区112为倒L型形状且和第十P+注入区504设置一定间距,可以提高电压钳制能力,增强正反向电学应力作用下的电学对称特性。

附图说明

本发明有如下附图:

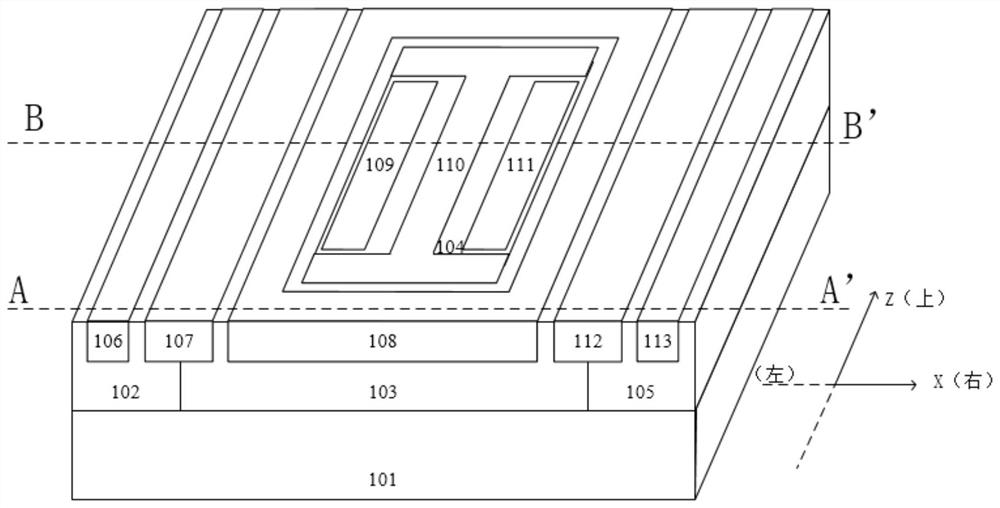

图1为实施例一中的本发明的结构示意图;

图2为实施例一中的本发明的金属连线图;

图3为实施例一中的本发明在SD模式下的等效电路图;

图4为实施例一中的本发明在NS模式下的等效电路图;

图5为实施例二中的本发明的结构图;

图6为实施例三中的本发明的结构图;

图7为实施例四中的本发明的结构图。

具体实施方式

现在结合附图对本发明作进一步详细的说明。这些附图均为简化的示意图,仅以示意方式说明本发明的基本结构,因此其仅显示与本发明有关的构成。

实施例一

如图1所示,一种双向稳压静电浪涌全芯片保护集成电路,包括P型衬底101,P型衬底101的上表面分别设有第一P阱103、第一N阱102和第二N阱105,第一P阱103的左侧面与第一N阱102的右侧面连接,第一N阱102的左侧面与P型衬底101的左侧面齐平,第一N阱102上设有第一P+注入区106,第一P+注入区106的右侧间隔设有第一N+注入区107,第一N+注入区107分别在第一N阱102和第一P阱103上;

第一P阱103的右侧面与第二N阱105的左侧面连接,第二N阱105的右侧面与P型衬底101的右侧面齐平,第二N阱105上设有第五P+注入区113,第五P+注入区113的左侧间隔设有第三N+注入区112,第三N+注入区112分别在第一P阱103和第二N阱105上;

第一P阱10在第一N+注入区107和第三N+注入区112之间设有第二P+注入环108。

可选地,第一N阱102和第二N阱105在第二P+注入环108的两侧对称设置。

可选地,第一P+注入区106和第五P+注入区113在第二P+注入环108的两侧对称设置。

可选地,第二P+注入环108的左侧面与第一N+注入区107的右侧面的间距和第二P+注入环108的右侧面与第三N+注入区112的左侧面的间距相同,第一N+注入区107和第三N+注入区112在第二P+注入环108的两侧对称设置。

另外,第三P阱103在第二P+注入环108内设有第三N阱104,第三N阱104上沿纵向设有工字型的第二N+注入区110,第三N阱104在第二N+注入区110的两横部之间设有第三P+注入区109和第四P+注入区111,第三P+注入区109和第四P+注入区11关于第二N+注入区110的纵部对称设置。

如图2所示,本实施例中,第一N+注入区107和第一P+注入区106均与第一金属201相连,第三P+注入区109、第二工形N+注入区110和第四P+注入区111均与第二金属202相连,第三N+注入区112和第五P+注入区113均与第三金属203相连。在实际使用时可以从从第一金属201引出一电极,用作IC的VSS PAD;可以从第二金属202引出一电极,用作IC的I/OPAD;可以从第三金属203引出一电极,用作IC的VDD PAD。

本实施例中,本发明有以下6种工作模式:

1)PS模式:I/O接高电位,VSS接低电位,VDD浮空;

2)PD模式:I/O接高电位,VDD接低电位,VSS浮空;

3)NS模式:I/O接低电位,VSS接高电位,VDD浮空;

4)ND模式:I/O接低电位,VDD高电位,VSS浮空;

5)DS模式:VDD接高电位,VSS接低电位,I/O浮空;

6)SD模式:VDD接低电位,VSS接高电位,I/O浮空。

本发明在SD模式与DS模式的电流泄放路径均呈双向全对称特性,以对SD模式为例,本发明工作在SD模式下的等效电路如图3所示,在A-A’剖面上,第一P+注入区106、第一N阱102和第一P阱103构成PNP管T1,第一N阱102、第一P阱103、第二N阱105和第三N+注入区112构成NPN管T2,PNP管T1和NPN管T2构成SCR结构的正反馈网络,提高双向稳压静电浪涌全芯片保护IC EOS/ESD鲁棒性。另外第一N+注入区107和第二P+注入环108构成稳压二极管D1,第一P阱103和第三N+注入区112构成正偏二极管D2,稳压二极管D1与正偏二极管D2形成稳压二极管触发路径,可调控双向稳压静电浪涌全芯片保护IC的工作电压及其电压拑制能力。

本发明在PS模式与NS模式、PD模式与ND模式、PD模式与PS模式、NS模式与ND模式中,双向稳压静电浪涌全芯片保护IC内部电流泄放路径呈电学双向对称特性,以对NS模式与PS模式为例,本发明工作在NS模式下的等效电路如图4所示,在B-B’剖面上,第一N阱102、第一P阱103、第三N阱104和第二工形N+注入区110构成NPN管T3,PNP管T1和NPN管T3构成的SCR结构的正反馈网络,提高了双向稳压静电浪涌全芯片保护IC的VSS至I/O端的电流泄放能力,第一P阱103、第二P+注入环108和第二工形N+注入区110构成正偏二极管,稳压二极管D1与正偏二极管形成稳压二极管触发路径,稳压二极管触发路径与SCR路径并联,降低了双向稳压静电浪涌全芯片保护IC的寄生电容,提高ESD/EOS鲁棒性;

在PS模式下,第三P+注入区109、第三N阱104、第一P阱103构成第一PNP管,第四P+注入区111、第三N阱104、第一P阱103构成第二PNP管,第一PNP管和第二PNP管并联,且与NPN管T3组成的正反馈网络构成SCR电流泄放路径,降低寄生电容并提高ESD/EOS鲁棒性。

在实际使用时,可按实际工艺规则调节第二工形N+注入区110与第二P+注入环108的间距,使第二工形N+注入区110与第二P+注入环108构成稳压二极管D4,即在PS模式下,存在与SCR路径并联的稳压二极管触发路径,实现静电浪涌保护IC的双向全芯片保护。

实施例二

如图5所示,本实施例中P型衬底101、第一P阱103、第一N阱102、第二N阱105、第一P+注入区106、第一N+注入区107、第五P+注入区113、第三N+注入区112和第二P+注入环108之间的结构关系参照实施例一。

具体的,第三P阱103在第二P+注入环108内分别设有第三N阱104和第一N+注入环301,第一N+注入环301分别在第三N阱104和第一P阱103上,第三N阱104在第一N+注入环301内设有第六P+注入区302,第六P+注入区302的左侧面与第一N+注入环301的间距和第六P+注入区302的右侧面与第一N+注入环301的间距相同,第六P+注入区302的前侧面与第一N+注入环301的间距和第六P+注入区302的后侧面与第一N+注入环301的间距相同。

在实际使用时,第一N+注入环301与第二P+注入环108之间形成的稳压二极管,可增强I/O到VSS,以及I/O到VDD之间的电压钳制能力,增强双向稳压静电浪涌全芯片保护IC的EOS/ESD鲁棒性。

实施例三

如图6所示,本实施例中P型衬底101、第一P阱103、第一N阱102、第二N阱105、第一P+注入区106、第一N+注入区107、第五P+注入区113、第三N+注入区112和第二P+注入环108之间的结构关系参照实施例一。

具体地,第三P阱103在第二P+注入环108内设有第三N阱104,第三N阱104在第二P+注入环108内沿横向设有日字型的第四N+注入区401,第四N+注入区401的四侧边分别在第三P阱103和第三N阱104上,第四N+注入区401的左N+环和右N+环对称设置,第三N阱104在左N+环内设有第七P+注入区402、在右N+环内设有第八P+注入区403,第七P+注入区402和第八P+注入区403对称设置。

在实际使用时,日字型的第四N+注入区401、第七P+注入区402和第八P+注入区403形成两个并接的PNP型三极管,可以增强电流导通均匀性和电压钳制能力。

实施例四

如图7所示,本实施例中P型衬底101、第一P阱103、第一N阱102、第二N阱105、第一P+注入区106和第五P+注入区113之间的结构关系参照实施例一。

具体地,第一N+注入区107为L型形状,第一N+注入区107的纵部分别在第一N阱102和第一P阱103上,第三N+注入区112为倒L型形状,第三N+注入区112的纵部分别在第二N阱105和第一P阱103上;第一P阱103在第一N+注入区107的横部与第三N+注入区112的纵部之间设有第九P+注入区502、在第二N+注入区112的横部与第一N+注入区107的纵部之间设有第十P+注入区504,第九P+注入区502的后侧面与第二P+注入环108的前侧面连接,第十P+注入区504的前侧面与第二P+注入环108的后侧面连接;第二P+注入环108的左侧面与第一N+注入区107的纵部的间距和第二P+注入环108的右侧面与第三N+注入区112的纵部的间距相同,第二P+注入环108的前侧面与第一N+注入区107的横部的间距和第二P+注入环108的后侧面与第三N+注入区112的横部的间距相同,即第一N+注入区107和第三N+注入区112关于第二P+注入环108中心对称;第三P阱103在第二P+注入环108内分别设有第三N阱104和第一N+注入环301,第一N+注入环301分别在第三N阱104和第一P阱103上,第三N阱104在第一N+注入环301内设有第六P+注入区302,第六P+注入区302的左侧面与第一N+注入环301的间距和第六P+注入区302的右侧面与第一N+注入环301的间距相同,第六P+注入区302的前侧面与第一N+注入环301的间距和第六P+注入区302的后侧面与第一N+注入环301的间距相同。

在实际使用时,由于第三N+注入区112为倒L型形状且和第十P+注入区504设置一定间距,可以提高电压钳制能力,增强正反向电学应力作用下的电学对称特性。

需要注意的是,在所有附图中,P-Sub代表P型衬底,PW代表P阱,NW代表N阱,P+代表P+注入区,N+代表N+注入区。

结合所有的实施例,本发明在不同实施例中的结构中心对称设置,在PS模式和PD模式下工作的电流泄放路径完全相同,在NS模式与ND模式下工作的电流泄放路径完全相同,在DS模式与SD模式下的电流泄放路径双向完全相同,在PS、PD、NS、ND、DS、SD六种工作模式中均有稳压二极管辅助SCR触发特征。本发明在全芯片EOS/ESD防护模式下,在I/O、VSS与VDD任意两端口之间均有对称正反向EOS/ESD保护特性,可减小芯片设计面积和寄生电容,降低导通电阻,增强EOS/ESD鲁棒性。

上述依据本发明为启示,通过上述的说明内容,相关工作人员完全可以在不偏离本项发明技术思想的范围内,进行多样的变更以及修改。本项发明的技术性范围并不局限于说明书上的内容,必须要根据权利要求范围来确定其技术性范围。

- 一种双向稳压静电浪涌全芯片保护集成电路

- 一种双向低压静电浪涌全芯片保护集成电路