一种微显示驱动芯片结构及其制作工艺

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及微显示驱动芯片技术领域,尤其涉及一种微显示驱动芯片结构及其制作工艺。

背景技术

目前基于硅基MOSFET(金属-氧化物半导体场效应晶体管)的显示技术,借助单晶硅高载流子迁移率(1350cm

发明内容

为了解决上述技术问题,本发明提供了一种微显示驱动芯片结构及其制作工艺,通过在场效应晶体管的制备中引入多晶硅薄膜晶体管模块,制备组合驱动芯片,工艺简单,驱动能力强,可避免漏电流大导致的显示异常问题,可降低发热和功耗。

为实现上述目的,本发明解决其技术问题所采用的技术方案是:所述微显示驱动芯片结构,包括半导体衬底及其上设置的MOSFET模块和多晶硅薄膜晶体管模块,所述半导体衬底上设置有单晶硅有源区,所述单晶硅有源区上设置所述MOSFET模块,所述单晶硅有源区的两侧分别设置有浅沟道隔离结构,其中一个浅沟道隔离结构的上方设置多晶硅有源区,所述多晶硅有源区上设置所述多晶硅薄膜晶体管模块。

进一步地,所述MOSFET模块包括栅叠层、主侧墙和源漏区Ⅰ,所述主侧墙环绕所述栅叠层,所述源漏区Ⅰ嵌于所述单晶硅有源区中且对准于所述主侧墙的两侧。

进一步地,所述栅叠层包括由下而上依次设置的栅介质层Ⅰ、栅导体层Ⅰ和盖帽,所述栅导体层Ⅰ由是掺杂或未掺杂的多晶硅材料制作。

进一步地,所述多晶硅薄膜晶体管模块包括源漏区Ⅱ、栅介质层Ⅱ和栅导体层Ⅱ,所述源漏区Ⅱ设置在所述多晶硅有源区的上端两侧,所述多晶硅有源区的上方覆盖所述栅介质层Ⅱ,所述栅介质层Ⅱ的上方中部设置所述栅导体层Ⅱ。

进一步地,所述栅导体层Ⅱ设置为金属栅极层或多晶硅栅极层。

进一步地,所述多晶硅有源区的下端设置所述浅沟道隔离结构,所述MOSFET模块的上端覆盖所述栅介质层Ⅱ,所述栅介质层Ⅱ的上端设置有介质层Ⅰ;所述介质层Ⅰ内贯穿设置有与所述源漏区Ⅰ和源漏区Ⅱ相对的多个导通孔,所述导通孔内填充有导电金属,所述导通孔的上端沉积有金属层。

进一步地,所述MOSFET模块和所述浅沟道隔离结构的上方设置有介质层Ⅱ,所述介质层Ⅱ的上端设置所述多晶硅薄膜晶体管模块,所述多晶硅薄膜晶体管模块的上端设置有介质层Ⅲ;所述介质层Ⅱ和介质层Ⅲ内贯穿设置有与所述源漏区Ⅰ和源漏区Ⅱ相对的多个导通孔,所述导通孔内填充有导电金属,所述导通孔的上端沉积有金属层。

一种所述的微显示驱动芯片结构的制作工艺,包括以下步骤:

1)制备半导体衬底,在半导体衬底上刻蚀成槽、在槽中填充氧化物和氧化物平坦化后形成浅沟道隔离结构;

2)在半导体衬底的单晶硅有源区上依次制备栅介质层Ⅰ和栅导体层Ⅰ,在所述浅沟道隔离结构上沉积多晶硅形成多晶硅有源区;

3)LDD注入、两个主侧墙形成和源漏离子注入;

4)在两个主侧墙两侧的单晶硅有源区上分别沉积金属硅化物形成源漏区Ⅰ,在两个主侧墙之间的栅导体层Ⅰ上沉积金属硅化物形成盖帽;

5)在步骤4)形成的芯片结构的上表面覆盖栅介质层Ⅱ,在多晶硅有源区上方的栅介质层Ⅱ上沉积栅导体层Ⅱ,源漏离子注入所述栅介质层Ⅱ内形成所述源漏区Ⅱ;

6)在步骤5)形成的芯片结构的上表面沉积介质层Ⅰ,并进行化学机械研磨;

7)在介质层Ⅰ内刻蚀与所述源漏区Ⅰ和源漏区Ⅱ相对的多个导通孔,并在导通孔内填充导电金属,对导通孔上端的导电金属进行化学机械研磨,在导通孔上端沉积金属层。

一种所述的微显示驱动芯片结构的制作工艺,包括以下步骤:

1)制备半导体衬底,在半导体衬底上刻蚀成槽、在槽中填充氧化物和氧化物平坦化后形成浅沟道隔离结构;

2)在半导体衬底的单晶硅有源区上依次制备栅介质层Ⅰ和栅导体层Ⅰ;

3)LDD注入、两个主侧墙形成和源漏离子注入;

4)在两个主侧墙两侧的单晶硅有源区上分别沉积金属硅化物形成源漏区Ⅰ,在两个主侧墙之间的栅导体层Ⅰ上沉积金属硅化物形成盖帽;

5)在步骤4)形成的芯片结构的上表面沉积介质层Ⅱ,并进行化学机械研磨;

6)在介质层Ⅱ上表面沉积多晶硅形成多晶硅有源区,对多晶硅有源区图形化;

7)在步骤6)形成的芯片结构上覆盖栅介质层Ⅱ,在多晶硅有源区上方的栅介质层Ⅱ上沉积栅导体层Ⅱ,源漏离子注入所述栅介质层Ⅱ内形成所述源漏区Ⅱ;

8)在步骤5)形成的芯片结构的上表面沉积介质层Ⅲ,并进行化学机械研磨;

9)在介质层Ⅱ和介质层Ⅲ内刻蚀与所述源漏区Ⅰ和源漏区Ⅱ相对的多个导通孔,并在导通孔内填充导电金属,对导通孔上端的导电金属进行化学机械研磨,在导通孔上端沉积金属层。

本发明的有益效果是:

1、本发明通过在MOSFET中引入多晶硅薄膜晶体管模块,制备组合驱动芯片,工艺简单,其结合了MOSFET的高载流子迁移率和强驱动能力,以及多晶硅薄膜晶体管的低漏电特性,解决了单纯多晶硅薄膜晶体管驱动能力差,不满足高分辨率需求的问题,同时也能够解决MOSFET漏电流大导致的显示异常问题,降低发热和功耗,拓展移动便携式应用。

2、本发明设计了两种组合驱动芯片结构,一种结构中包括一个介质层,整体结构更简单,制作工艺简单,另一种结构是包括两个介质层,可引入多个多晶硅薄膜晶体管,而不占用半导体衬底,使半导体衬底的利用率更高。

综上,本发明通过在场效应晶体管中引入多晶硅薄膜晶体管模块,制备组合驱动芯片,工艺简单,驱动能力强,可避免漏电流大导致的显示异常问题,可降低发热和功耗。

附图说明

下面对本发明说明书各幅附图表达的内容及图中的标记作简要说明:

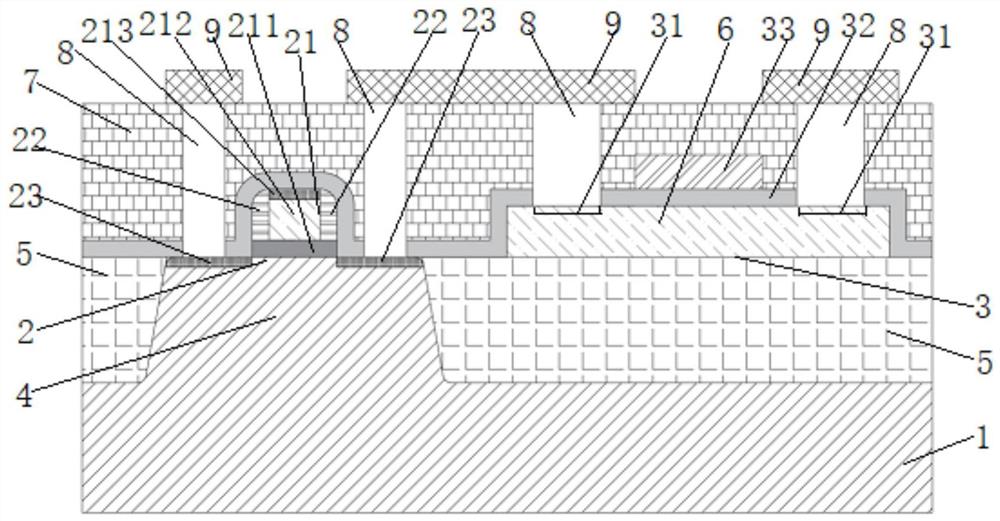

图1为本发明中实施例1的结构示意图;

图2为图1中的驱动芯片结构的制备工艺流程图;

图3为本发明中实施例2的结构示意图;

图4为图3中的驱动芯片结构的制备工艺流程图;

上述图中的标记均为:1.半导体衬底,2.MOSFET模块,21.栅叠层,211.栅介质层Ⅰ,212.栅导体层Ⅰ,213.盖帽,22.主侧墙,23.源漏区Ⅰ,3.多晶硅薄膜晶体管模块,31.源漏区Ⅱ,32.栅介质层Ⅱ,33.栅导体层Ⅱ,4.单晶硅有源区,5.浅沟道隔离结构,6.多晶硅有源区,7.介质层Ⅰ,8.导通孔,9.金属层,10.介质层Ⅱ,11.介质层Ⅲ。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对实施例中的技术方案进行清楚、完整地描述,以下实施例用于说明本发明,但不用来限制本发明的范围。

在本发明的描述中,需要说明的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

本发明具体的实施方案为:如图1和图3所示,一种微显示驱动芯片结构,包括半导体衬底1及其上设置的MOSFET模块2和多晶硅薄膜晶体管模块3,半导体衬底1上设置有单晶硅有源区4,单晶硅有源区4上设置MOSFET模块2,单晶硅有源区4的两侧分别设置有浅沟道隔离结构5,其中一个浅沟道隔离结构5的上方设置多晶硅有源区6,多晶硅有源区6上设置多晶硅薄膜晶体管模块3,通过在MOSFET中引入多晶硅薄膜晶体管模块3,制备组合驱动芯片,该组合驱动芯片的MOSFET模块用于驱动电路的ADC(模数转换),DAC(数模转换),OSC(振荡器),SRAM(存储器),栅极驱动电路,源极驱动电路等,和像素电路的驱动管和部分开关管,利用了MOSFET模块的高载流子迁移率和强驱动能力,解决单纯多晶硅薄膜晶体管驱动能力差,不满足高分辨率需求的问题。组合驱动芯片的多晶硅薄膜晶体管模块3用于像素电路的部分开关管,利用了多晶硅薄膜晶体管的低漏电特性,能够解决MOSFET漏电流大导致的显示异常问题,降低发热和功耗,拓展移动便携式应用。

实施例1:

如图1所示,其中的MOSFET模块2包括栅叠层21、主侧墙22和源漏区Ⅰ

23,主侧墙22环绕栅叠层21,源漏区Ⅰ23嵌于单晶硅有源区4中且对准于主侧墙22的两侧。其中的栅叠层21包括由下而上依次设置的栅介质层Ⅰ211、栅导体层Ⅰ212和盖帽213,栅介质层Ⅰ211可以由普通介质材料(例如SiO

其中的多晶硅薄膜晶体管模块3包括源漏区Ⅱ31、栅介质层Ⅱ32和栅导体层Ⅱ33,源漏区Ⅱ31设置在多晶硅有源区6的上端两侧,多晶硅有源区6的上方覆盖栅介质层Ⅱ32,栅介质层Ⅱ32为多晶硅栅极氧化层,栅介质层Ⅱ32的上方中部设置栅导体层Ⅱ33,该栅导体层Ⅱ33设置为金属栅极层或多晶硅栅极层,使用的材料可以是掺杂或未掺杂的多晶硅,或金属(如Ti、Co、Ni、Al或W中的一种或其组合)等。

其中的多晶硅有源区6的下端设置浅沟道隔离结构5,MOSFET模块2的上端覆盖栅介质层Ⅱ32,栅介质层Ⅱ32的上端设置有介质层Ⅰ7,介质层Ⅰ7一般选用氧化硅、氮化硅等材料制成,介质层Ⅰ7内贯穿设置有与源漏区Ⅰ23和源漏区Ⅱ31相对的多个导通孔8,导通孔8内填充有导电金属钨,导通孔8的上端沉积有金属层9,可将MOSFET模块2和多晶硅薄膜晶体管模块3按照设计电路电连接。

如图2所示,上述微显示驱动芯片结构的制作工艺,包括以下步骤:

1)制备半导体衬底1,在半导体衬底1上刻蚀成槽、在槽中填充氧化物和氧化物平坦化后形成浅沟道隔离结构5;

2)在半导体衬底1的单晶硅有源区4上依次制备栅介质层Ⅰ211和栅导体层Ⅰ212,在浅沟道隔离结构5上沉积多晶硅形成多晶硅有源区6;

3)在步骤2)形成的芯片结构的上表面进行LDD注入、两个主侧墙22形成和源漏离子注入;

4)在两个主侧墙22两侧的单晶硅有源区4上分别沉积金属硅化物形成源漏区Ⅰ23,在两个主侧墙22之间的栅导体层Ⅰ212上沉积金属硅化物形成盖帽213;

5)在步骤4)形成的芯片结构的上表面覆盖栅介质层Ⅱ32,在多晶硅有源区6上方的栅介质层Ⅱ32上沉积栅导体层Ⅱ33,源漏离子注入栅介质层Ⅱ32内形成源漏区Ⅱ31;

6)在步骤5)形成的芯片结构的上表面沉积介质层Ⅰ7,并进行化学机械研磨;

7)在介质层Ⅰ7内刻蚀与源漏区Ⅰ23和源漏区Ⅱ31相对的多个导通孔8,并在导通孔8内填充导电金属钨,对导通孔8上端的导电金属进行化学机械研磨,在导通孔8上端沉积金属层9,将MOSFET模块2和多晶硅薄膜晶体管模块3按照设计电路电连接。

实施例2:

如图3所示,与实施例1中的微显示驱动芯片结构不同的是:MOSFET模块2和浅沟道隔离结构5的上方设置有介质层Ⅱ10,介质层Ⅱ10的上端设置多晶硅薄膜晶体管模块3,多晶硅薄膜晶体管模块3的上端设置有介质层Ⅲ11;介质层Ⅱ10和介质层Ⅲ11内贯穿设置有与源漏区Ⅰ23和源漏区Ⅱ31相对的多个导通孔8,导通孔8内填充有导电金属,导通孔8的上端沉积有金属层9,可将MOSFET模块2和多晶硅薄膜晶体管模块3按照设计电路电连接。其中的介质层Ⅱ10和介质层Ⅲ11的材质与实施例1中的介质层Ⅰ7的材质相同,一般选用氧化硅、氮化硅等材料制成,当然根据需要也可设置3层或3层以上的介质层,多层介质层之间由多晶硅薄膜晶体管模块3分割,可引入多个多晶硅薄膜晶体管,而不占用半导体衬底1,使半导体衬底1的利用率更高。

如图4所示,上述微显示驱动芯片结构的制作工艺,包括以下步骤:

1)制备半导体衬底1,在半导体衬底1上刻蚀成槽、在槽中填充氧化物和氧化物平坦化后形成浅沟道隔离结构5;

2)在半导体衬底1的单晶硅有源区4上依次制备栅介质层Ⅰ211和栅导体层Ⅰ212;

3)在步骤2)形成的芯片结构的上表面进行LDD注入、两个主侧墙22形成和源漏离子注入;

4)在两个主侧墙22两侧的单晶硅有源区4上分别沉积金属硅化物形成源漏区Ⅰ23,在两个主侧墙22之间的栅导体层Ⅰ212上沉积金属硅化物形成盖帽213;

5)在步骤4)形成的芯片结构的上表面沉积介质层Ⅱ10,并进行化学机械研磨;

6)在介质层Ⅱ10上表面沉积多晶硅形成多晶硅有源区6,对多晶硅有源区6图形化;

7)在步骤6)形成的芯片结构上覆盖栅介质层Ⅱ32,在多晶硅有源区6上方的栅介质层Ⅱ32上沉积栅导体层Ⅱ33,源漏离子注入栅介质层Ⅱ32内形成源漏区Ⅱ31;

8)在步骤5)形成的芯片结构的上表面沉积介质层Ⅲ11,并进行化学机械研磨;

9)在介质层Ⅱ10和介质层Ⅲ11内刻蚀与所述源漏区Ⅰ23和源漏区Ⅱ31相对的多个导通孔8,并在导通孔8内填充导电金属,对导通孔8上端的导电金属进行化学机械研磨,在导通孔8上端沉积金属层9,将MOSFET模块2和多晶硅薄膜晶体管模块3按照设计电路电连接。

综上,本发明通过在场效应晶体管中引入多晶硅薄膜晶体管模块,制备组合驱动芯片,工艺简单,驱动能力强,可避免漏电流大导致的显示异常问题,可降低发热和功耗。

以上所述,只是用图解说明本发明的一些原理,本说明书并非是要将本发明局限在所示所述的具体结构和适用范围内,故凡是所有可能被利用的相应修改以及等同物,均属于本发明所申请的专利范围。

- 一种微显示用组合驱动芯片结构及其制作工艺

- 一种具有抗光电效应的微显示驱动芯片结构