一种基于SiP的可编程信号处理模块

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及系统级封装与信号处理系统,特别是一种应用于光纤陀螺等宇航电子产品中的基于SiP的可编程信号处理模块。

背景技术

以光纤陀螺为代表的微光机电产品,在陆基交通导航、机器人控制等民用领域,无线电导航、直升机瞄准等军事应用领域,以及卫星导航、惯性制导等航天应用领域,都有着广阔的市场前景,正朝着高精度、轻小型和低成本这三个方向发展。电路模块集成化,尤其是对信号处理电路的核心器件进行集成,是目前该类产品提高集成度、缩小体积、降低成本,并且为产品升级换代提供技术支撑的有效路径。

当前信号处理电路一般采用FPGA+DSP架构,利用FPGA来控制时序、DSP实现非常复杂的滤波算法,是以比较理想的数据处理方案,但体积大、结构复杂,对于光纤陀螺的小型化需求不是特别适用。而卫星平台对核心部组件的微小型化需求非常迫切,特别是对于敏感器等部件的一体化和微型化提出了非常高的要求,因此,进一步提升光纤陀螺等微光机电产品信号处理系统的集成度、灵活性、通用性势在必行。

发明内容

针对上述相关现有技术不足,本申请提供一种基于SiP的可编程信号处理模块,通过SiP技术实现系统级集成,采用FPGA+ADC+DAC架构,该系统灵活性强、集成度高、实现了小型化,可应用于光纤陀螺等宇航器件。

为了实现本发明的目的,拟采用以下方案:

一种基于SiP的可编程信号处理模块,包括基于SiP技术集成封装于一体的核心处理芯片、模数转化单元、数模转化单元、刷新芯片;

模数转化单元,用于将采集到的模拟量转化成数字量,以供核心处理芯片计算处理,模数转化单元包括高速并行ADC芯片和低速串行ADC芯片;

核心处理芯片,包括FPGA芯片,用于完成时序信号的产生与闭环算法设计,并用于计算处理模数转化单元转换的数字量,并将处理后的数字量输入到数模转化单元;

数模转化单元,包括高速并行DAC芯片,用于将核心处理芯片输入的数字量转换为模拟量后向外输出;

刷新芯片,用于在核心处理芯片发生单粒子翻转时,对核心处理芯片进行实时刷新,以使核心处理芯片快速恢复运行。

进一步,高速并行ADC芯片有两片、低速串行ADC芯片有一片、高速并行DAC芯片有一片、刷新芯片有一片,分别连接FPGA芯片。

进一步,所述处理模块集成封装于一封装基体,封装基体为双腔结构,其一面具有上腔体,另一面具有下腔体,FPGA芯片设置于上腔体,高速并行ADC芯片、低速串行ADC芯片、高速并行DAC芯片、刷新芯片设置于下腔体,下腔体内设有解耦电容。

进一步,封装基体采用陶瓷管壳,其一面向内凹陷形成上腔体,上腔体通过第一盖板封闭,第一盖板贴于封装基体一面设置;封装基体另一面设置有柯伐环,下腔体位于柯伐环中间,下腔体通过第二盖板封闭,第二盖板贴于柯伐环顶面设置。

进一步,封装基体具有信号叠层,位于信号叠层的数字信号布线层与模拟信号布线层之间依次具有数字地层、数字电源层、数字地层、模拟电源层,模拟信号布线层另一侧有模拟地层。

更进一步,封装基体具有信号叠层,信号叠层包括从封装基体一面向另一面依次设置的13层:L1表层、L2数字地层、L3芯片键合外层、L4芯片键合内层、L5数字电源层、L6芯片安装层、L7数字信号布线层、L8数字地层、L9数字电源层、L10数字地层、L11模拟电源层、L12模拟信号布线层、L13模拟地层。

进一步,FPGA芯片为300万门级的SRAM型。

进一步,在配置FPGA芯片时,通过设置刷新芯片选择JTAG直接配置FPGA芯片,或通过外部PROM上电后自动配置FPGA芯片。

进一步,所述处理模块应用于光纤陀螺的姿态控制,高速并行ADC芯片用于实现光纤模拟输入电压的采集并转化为数字量,低速串行ADC芯片用于实现温度、电压、电流中至少一种遥测量的采集并转化为数字量,FPGA芯片用于根据高速并行ADC芯片和低速串行ADC芯片采集并转化的数字量进行姿态解算并生成姿态控制数字阶梯波信号,高度并行DAC芯片用于将数字阶梯波信号转换为模拟阶梯波信号,以产生光电调制器驱动电压,并反馈到光纤陀螺实现姿态闭环控制。

本发明的有益效果:

1、基于陶瓷封装SiP技术集成可编程FPGA、ADC、DAC、刷新芯片等大量资源为一个较为完备的独立模块/系统,具有集成度高、高性能等特点,无需

外接电路或者只需简单的外围电路即可实现信号处理;与PCB板级系统相比,集成度提高、尺寸缩小,降低了板级电路复杂度与风险,提高了其可靠性;内部集成了解耦电容,实现器件级解耦;

2、基于300万门级的SRAM型FPGA芯片实现,包含了可编程逻辑模块CLB、通用输入输出模块IOB以及各种IP资源,可通过内JTAG、串行模式或并行模式现场配置,可通过复杂的数学算法实现高性能数字信号处理,灵活实现各种所需功能;

3、刷新芯片可对FPGA芯片进行实施刷新,同时在配置FPGA芯片时,可以通过设置刷新芯片选择JTAG直接配置FPGA芯片或通过外部PROM上电后自动配置FPGA芯片;刷新芯片可为宇航SRAM型FPGA空间应用的单粒子翻转问题提供实时刷新应用解决方案,不需外接电路即可在FPGA芯片出现单粒子翻转通过刷新使其快速回复运行,降低了应用风险,大幅度降低刷新系统设计的难度和复杂度;

4、内部FPGA芯片可灵活实现多种所需功能,用户既可单独使用SiP模块对信号进行处理,也可将FPGA芯片定义为通信接口,与外部处理器组成系统来完成特定的使用需求;SiP可单独配置每一片ADC或DAC,完成ADC的信号检测功能或DAC的信号输出功能;

5、封装基体一面凹陷/挖腔形成上腔体,用于容纳FPGA芯片,另一面在平整表面通过设置柯伐环来形成下腔体,并用于容纳其他芯片及解耦电容,相比于PCB板级系统,集成度更高尺寸更缩小;并缩短了布线,可将13层信号叠层设于封装基体,并采用为“数字信号布线层-数字地层-数字电源层-数字地层-模拟电源层-模拟信号布线层-模拟地层”的信号叠层,有效隔离数字信号和模拟信号;上腔体通过挖腔凹陷形成来布置一个耐高温PFGA,利于进一步缩小封装体积,下腔体通过柯伐环构建,可以满足下腔体需要安装多个芯片对腔体表面平整度的要求,还可以保护下腔体内不耐高温的电容。

附图说明

本文描述的附图只是为了说明所选实施例,而不是所有可能的实施方案,更不是意图限制本发明的范围。

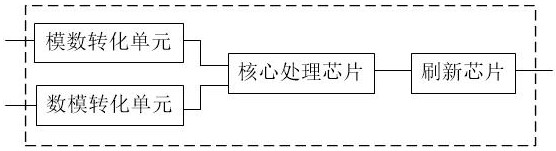

图1示出了本申请实施例的可编程信号处理模块结构框图

图2示出了本申请实施例的可编程信号处理模块电气原理图。

图3示出了本申请实施例的应用方案一原理框图。

图4示出了本申请实施例的应用方案二原理框图。

图5示出了本申请实施例的可编程信号处理模块实体结构侧视图。

图6示出了本申请实施例的封装基体信号叠层示意图。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面结合附图对本发明的实施方式进行详细说明,但本发明所描述的实施例是本发明一部分实施例,而不是全部的实施例。

本实例提供一种基于SiP的可编程信号处理模块,通过SiP技术实现系统集成,采用FPGA+ADC+DAC架构,如图1所示,包括封装于一体的核心处理芯片、模数转化单元、数模转化单元、刷新芯片。

如图2所示的原理图:

模数转化单元用于将采集到的模拟量转化成数字量,以供核心处理芯片计算处理,模数转化单元包括高速并行ADC芯片和低速串行ADC芯片。

核心处理芯片包括FPGA芯片,用于完成时序信号的产生与闭环算法设计,可以满足光纤陀螺产品的计算和控制要求;并用于计算处理模数转化单元转换的数字量,并将处理后的数字量输入到数模转化单元。

数模转化单元包括高速并行DAC芯片,用于将核心处理芯片输入的数字量转换为模拟量后向外输出。

刷新芯片用于在核心处理芯片发生单粒子翻转时,对核心处理芯片进行实时刷新,以使核心处理芯片快速恢复运行。刷新芯片采用对SRAM型FPGA的配置存储器进行刷新的电路,如BSV2CQRH型,配置该刷新芯片,可以满足本实例模块的高可靠宇航应用需求,其支持主串、从串,可利用JTAG接口进行刷新、接口简单且不占用IOB资源,可采用盲刷方式、覆盖除BRAM内容以外的所有配置码流,刷新控制简洁、仅需用户提供刷新时钟信号和刷新使能信号。

具体的,FPGA芯片为300万门级的SRAM型,包含了可编程逻辑模块CLB、通用输入输出模块IOB以及各种IP资源,可通过内JTAG、串行模式或并行模式现场配置,可通过复杂的数学算法实现高性能数字信号处理,灵活实现各种所需功能。用户既可单独使用SiP模块对信号进行处理,也可将FPGA芯片定义为通信接口,与外部处理器组成系统来完成特定的使用需求。

具体的,高速并行ADC芯片有两片、低速串行ADC芯片有一片、高速并行DAC芯片有一片、刷新芯片有一片,分别连接FPGA芯片,通过SIP技术集成为一个较为完备的独立模块/系统,无需外接电路或者只需简单的外围电路即可实现信号处理。与PCB板级系统相比,集成度提高、尺寸缩小,降低了板级电路复杂度与风险,提高了其可靠性。

本实例采用SiP技术,集成为一个器件,如图5所示,为器件实体结构侧视图,具体的,本实例的处理模块集成封装于一封装基体1。

封装基体1为双腔结构,极大缩小器件体积,其一面具有上腔体4,另一面具有下腔体5。上腔体4的芯片放置区2,用于设置FPGA芯片;下腔体5的芯片放置区2,用于设置高速并行ADC芯片、低速串行ADC芯片、高速并行DAC芯片、刷新芯片。下腔体5内还设有解耦电容3,用于实现器件级解耦。

具体的,封装基体1可以采用陶瓷管壳,上腔体4是在其一面向内凹陷形成,且上腔体4通过第一盖板6封闭,第一盖板6贴于封装基体1一面设置。封装基体另一面设置有柯伐环7,下腔体5位于柯伐环7中间,下腔体5通过第二盖板8封闭,第二盖板8贴于柯伐环7顶面设置。

通过上述的方向将本实例模块的各器件合理布局于双腔结构的封装基体1中,将其形成为具备完整功能的系统,实现系统级封装,区别于若干单芯片在PCB板级形成系统,该模块实现“系统整合”,在板级,只需配备简单外围电路即可实现信号处理功能,同时将风险提前到“器件”,降低了板级设计风险,同时双腔结构,相比于单面平铺结构,进一步缩小了器件尺寸,实现小型化。

作为更加具体的实施方式,本实例的模块封装基体1具有信号叠层,如图6所示为信号叠层示意图,信号叠层包括从封装基体1一面向另一面依次设置的13层:L1表层、L2数字地层、L3芯片键合外层、L4芯片键合内层、L5数字电源层、L6芯片安装层、L7数字信号布线层、L8数字地层、L9数字电源层、L10数字地层、L11模拟电源层、L12模拟信号布线层、L13模拟地层;从而通过此种布线,使得数字信号布线层与模拟信号布线层之间依次具有数字地层、数字电源层、数字地层、模拟电源层,解决了本实例的模块中既有模拟信号又有数字信号可能存在干扰等问题,能够有效的隔离数字信号和模拟信号,有效保证模拟信号的质量。

本实例可应用于光纤陀螺的姿态控制。高速并行ADC芯片,采样率选择3MSPS,主要采集光纤陀螺信号,用于实现光纤模拟输入电压的采集与转化,低速串行ADC芯片,采样率为1MSPS,主要采集温度或电压基准等遥测模拟量,用于实现温度、电压、电流中至少一种遥测量的采集与转化。

FPGA芯片用于根据高速并行ADC芯片和低速串行ADC芯片采集并转化的数字量进行姿态解算并生成姿态控制数字阶梯波信号,高度并行DAC芯片用于将数字阶梯波信号转换为模拟阶梯波信号,以产生光电调制器驱动电压,并反馈到光纤陀螺实现姿态闭环控制。

具体的,在配置FPGA芯片时可以通过设置刷新芯片选择JTAG直接配置FPGA芯片或通过外部PROM上电后自动配置FPGA,刷新芯片为BSV2CQRH型,可为宇航SRAM型FPGA芯片空间应用的单粒子翻转问题提供实时刷新应用解决方案,大幅度降低刷新系统设计的难度和复杂度,这由刷新芯片上i_pause及i_rst的引脚电平决定。刷新芯片的i_pause引脚为高电平则其处于刷新工作状态,反之i_pause引脚为低电平则其处于待机状态不进行配置位刷新。刷新芯片的i_rst引脚为其复位信号,i_rst为低电平时复位,刷新芯片处于配置状态,此时电路仅能完成配置功能;i_rst为高电平时,刷新芯片在FPGA芯片配置完成后DONE信号变高后,开始进行盲刷操作。刷新过程中,如检测到DONE信号变低,则意味着FPGA芯片发生单粒子功能中断,会立即给FPGA施加复位脉冲,进行重新配置。

表1 刷新芯片工作状态真值表

本实例的FPGA可灵活实现多种所需功能,因此用户既可单独使用该系统对信号进行处理,也可将FPGA定义为通信接口,与外部处理器组成系统来完成特定的使用需求。两种典型应用方案框图如图3及图4所示。

在图3所示的应用方案一中,本实例的模块可单独配置每一片ADC芯片或DAC芯片,完成ADC的信号检测功能或DAC的信号输出功能。此外,本实例的模块可用于更复杂的应用方案,如在光纤陀螺产品中,用于负责陀螺的姿态控制,首先由并行ADC芯片接收到光路信号,由FPGA内部算法完成姿态解算及姿态控制,最终由并行DAC芯片将光路控制信号反馈到陀螺实现姿态的闭环控制。

在图4所示的应用方案二中,本实例的模块与外部处理器组成信号处理系统。在追求运算速度的应用方案中,本实例的模块可只负责信号采集及信号传输,信号处理由外部处理器完成。

以上仅为本发明的优选实施例,并不表示是唯一的或是限制本发明。本领域技术人员应理解,在不脱离本发明的范围情况下,对本发明进行的各种改变或同等替换,均属于本发明保护的范围。

- 一种基于SiP的可编程信号处理模块

- 一种可编程高集成度阵列信号处理SIP芯片