一种单级滤波器

文献发布时间:2023-06-19 11:02:01

技术领域

本发明涉及滤波器领域,特别是涉及一种单级滤波器。

背景技术

电磁干扰滤波器的作用是允许设备正常工作所需的频率(通常市电为50/60Hz)进出设备,而对电磁干扰频率有较大的衰减作用。功率因数校正(PowerFactor Correction,PFC)电路中,差模电感通常采用铁粉芯/磁粉芯以避免磁饱和,铁粉芯/磁粉芯相对磁导率通常小于150H/M,工作时漏磁很大。

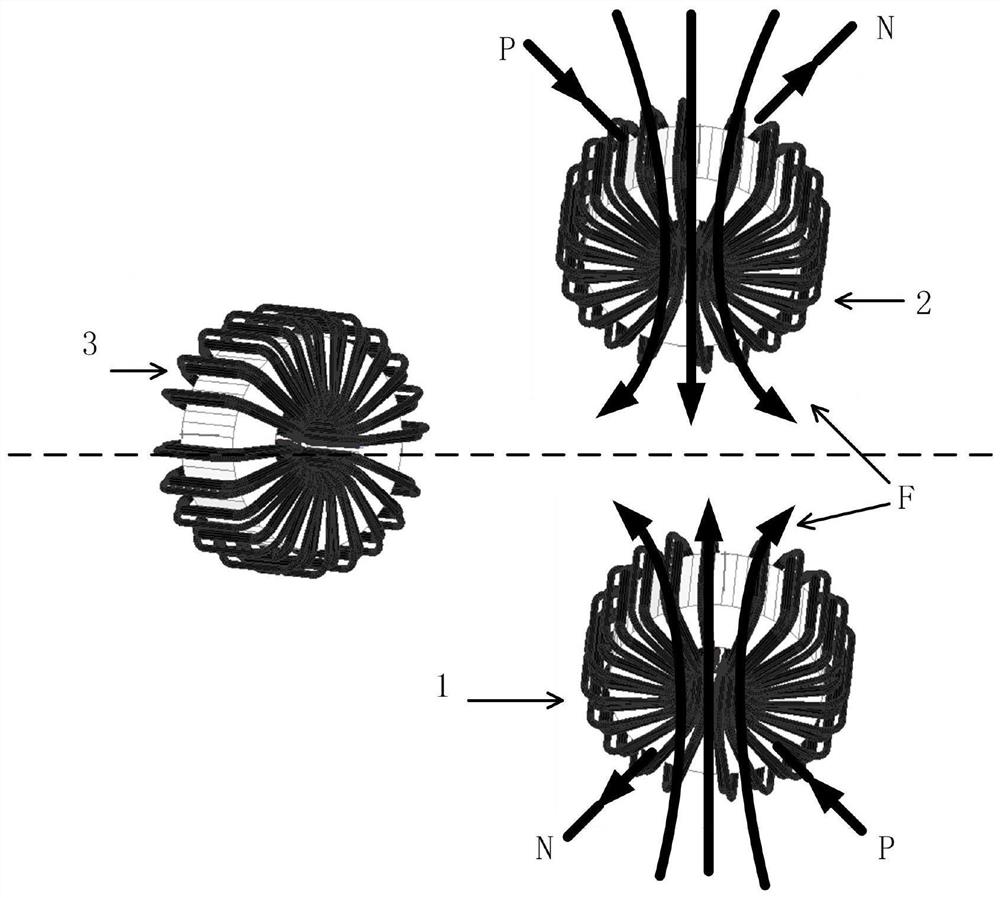

滤波器共模扼流线圈铁芯相对磁导率通常在2000H/M以上,在PCB电路有限的空间布局中,功率因数校正电感的漏磁容易与滤波器共模扼流线圈铁芯形成磁回路和磁耦合导致扼流圈感应干扰电压,导致滤波器性能变差,现有的大功率产品设计中,常用交错式PFC电路作为谐波抑制和功率变换的方案。电路上利用IGBT、大功率二极管、PFC电感进行电路拓扑,控制输出电压和谐波问题,钽电容起储能和滤波作用。现有技术中多关注的是PFC电感与PFC电感之间的漏磁耦合,布局如图1所示,N代表电流的输出,P代表电流的输入,F为电感产生的漏磁通方向,第一PFC电感(第一功率因数校正电感1)与共模扼流线圈C的模扼流圈磁体面垂直布置,俩PFC的环形磁芯面的方向互相垂直的方式,其原理是使得PFC产生的漏磁通互相垂直减少PFC产生的漏磁通穿过其他磁体,减少感应电流(电磁干扰)产生,降低器件间的耦合。但这种实施方式却忽略对共模扼流线圈的影响,由于器件布局紧凑,第二PFC电感(第二功率因数校正电感2)漏磁通会穿过共模扼流线圈的磁体面,在磁体面产生的电磁干扰,总会使得一个PFC电感的漏磁通对共模扼流线圈产生影响,降低其滤波性能。

发明内容

本发明的目的是提供一种单级滤波器,用于减少磁性器件间的近场耦合效应,增强滤波器的衰减性能,进而增强滤波器的滤波性能。

为实现上述目的,本发明提供了如下方案:

一种单级滤波器,包括:滤波电路和与所述滤波电路连接的功率因数校正电路;

所述功率因数校正电路包括第一功率因数校正电感和第二功率因数校正电感;所述第一功率因数校正电感和所述第二功率因数校正电感均与所述滤波电路连接;所述第一功率因数校正电感和所述第二功率因数校正电感对称设置,使得所述第一功率因数校正电感产生的漏磁通与所述第二功率因数校正电感产生的漏磁通相互抵消;所述滤波电路位于所述第一功率因数校正电感和所述第二功率因数校正电感的对称轴上。

可选的,所述第一功率因数校正电感和所述第二功率因数校正电感之间的距离大于或等于20厘米。

可选的,所述滤波电路包括:共模扼流线圈,所述共模扼流线圈的环心位于所述对称轴上。

可选的,所述共模扼流线圈与所述第一功率因数校正电感之间的距离大于或等于40厘米,所述共模扼流线圈与所述第二功率因数校正电感之间的距离大于或等于40厘米。

可选的,还包括:整流桥,所述滤波电路和所述功率因数校正电路之间连接所述整流桥。

可选的,所述滤波电路还包括:第一X电容和第二X电容,所述第一X电容的一端与所述共模扼流线圈的第一线圈的输入端连接,所述第一X电容的另一端与所述共模扼流线圈的第二线圈的输入端连接,所述第二X电容的一端分别与所述第一线圈的输出端、所述第一功率因数校正电感的输入端和所述第二功率因数校正电感的输入端连接,所述第一功率因数校正电感的输出端和所述第二功率因数校正电感的输出端均与电源的正极连接,所述第二X电容的另一端和所述第二线圈的输出端均与所述电源的负极连接。

可选的,所述滤波电路还包括:第一Y电容和第二Y电容,所述第一Y电容的一端分别与所述第一线圈的输出端、所述第二X电容的一端和所述第一功率因数校正电感的输入端连接,所述第二Y电容的一端分别与所述第二线圈的输出端和所述负极连接,所述第一Y电容的另一端与所述第二Y电容的另一端均接地。

可选的,所述功率因数校正电路还包括:第一钽电容和第二钽电容;所述第一钽电容的一端分别与所述第一功率因数校正电感的输出端、所述第二功率因数校正电感的输出端和所述正极连接,所述第一钽电容的另一端分别与所述第二X电容的另一端和所述负极连接;所述第二钽电容的一端分别与所述第一钽电容的一端和所述正极连接,所述第二钽电容的另一端分别与所述第一钽电容的另一端与所述负极连接。

可选的,所述功率因数校正电路还包括:第一IGBT和第二IGBT;所述第一IGBT的源极与所述第一功率因数校正电感的输出端连接,所述第一IGBT的漏极分别与所述第二X电容的另一端和所述第一钽电容的另一端连接;所述第二IGBT的源极与所述第二功率因数校正电感的输出端连接,所述第二IGBT的漏极分别与所述第一IGBT的漏极和所述第一钽电容的另一端连接。

可选的,所述第一功率因数校正电感的线圈和所述第二功率因数校正电感的线圈均为半结构绕法绕制的线圈。

根据本发明提供的具体实施例,本发明公开了以下技术效果:本发明中第一功率因数校正电感和第二功率因数校正电感对称设置,使得第一功率因数校正电感产生的漏磁通与第二功率因数校正电感产生的漏磁通相互抵消,减少了第一功率因数校正电感和第二功率因数校正电感对共模扼流线圈的近场耦合干扰,增强滤波器的衰减性能,进而增强滤波器的滤波性能。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

图1为现有滤波器中共模扼流线圈和PFC电感的位置关系图;

图2为漏磁耦合原理示意图;

图3为本发明实施例提供的共模扼流线圈和PFC电感的位置关系图;

图4为本发明实施例提供的共模扼流线圈和PFC电感的最佳位置关系图;

图5为本发明实施例提供的漏磁耦合最小点的原理示意图;

图6为本发明实施例提供的单级滤波器的电路原理图;

图7为本发明实施例提供的单级滤波器的具体电路图;

图8为本发明实施例提供的PFC电感对半绕法的结构示意图;

图9为本发明实施例提供的对半绕法降低寄生电容效应示意图;

图10为本发明实施例提供的对半绕法降低寄生电容效应示意图;

图11为应用图1布局的外机控制器的高频和低频的测试结果图;

图12为应用图3布局的外机控制器的高频和低频的测试结果图。

符号说明:

1-第一功率因数校正电感、2-第二功率因数校正电感、3-共模扼流线圈、4-滤波电路、5-整流桥、6-功率因数校正电路、7-第一X电容、8-第二X电容、9-第一Y电容、10-第二Y电容、11-第一IGBT、12-第二IGBT、13-第一钽电容、14-第二钽电容、15-第一线圈、16-第二线圈、17-第一二极管、18-第二二极管、L-零线、N火线、PE-地线、DC+电源正极、DC-电源负极、P-输入、N-输出、F-漏磁通方向。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

漏磁耦合原理如图2所示:IGBT拓扑驱动导通信号时,在PFC电感(图2右边的环形)的环形磁体面会产生漏磁(漏磁方向与磁体面垂直),当漏磁穿过另一磁体面时(如PFC电感、共模扼流线圈(图2左边的环形)),该磁体会产生感应电流(图2中左边环形内的箭头代表感应电流的方向)、电磁干扰。基于上述原理本实施例提供了一种单级滤波器,包括:滤波电路4和与所述滤波电路4连接的功率因数校正电路6。

所述功率因数校正电路6包括第一功率因数校正电感1和第二功率因数校正电感2;所述第一功率因数校正电感1和所述第二功率因数校正电感2均与所述滤波电路4连接;如图3所示,所述第一功率因数校正电感1和所述第二功率因数校正电感2对称设置,使得所述第一功率因数校正电感1产生的漏磁通与所述第二功率因数校正电感2产生的漏磁通相互抵消,从而减少PFC电感产生的漏磁通与滤波电路4的共模扼流线圈3产生耦合;所述滤波电路4位于所述第一功率因数校正电感1和所述第二功率因数校正电感2的对称轴上。

如图4所示,作为一种可选的实施方式,所述第一功率因数校正电感1和所述第二功率因数校正电感2之间的距离大于或等于20厘米,否则磁体间的漏磁会互相干扰。

作为一种可选的实施方式,所述滤波电路4包括:共模扼流线圈3,如图5所示,共模扼流线圈3放置在两个PFC电感(图5右边的两个环形)的漏磁通抵消、最小耦合位置,大致是扼流圈的中线与两PFC距离的中线重叠的位置即所述共模扼流线圈3的环心位于所述对称轴上。最小耦合点和漏磁是空间存在的,PFC的漏磁总会在共模扼流线圈3的磁体面产生感应电流,当俩PFC电感产生相反方向的漏磁通,在共模扼流线圈3磁体面则会产生两种感应电流,如图5左边环形内的箭头所示,并且等大反向并抵消。

作为一种可选的实施方式,所述共模扼流线圈3与所述第一功率因数校正电感1之间的距离大于或等于40厘米,所述共模扼流线圈3与所述第二功率因数校正电感2之间的距离大于或等于40厘米,间距过小,PFC电感的漏磁耦合越大,共模扼流线圈3产生的感应干扰电流将导致共模扼流线圈3的电磁抑制效果变得非常差。

作为一种可选的实施方式,如图6所示,单级滤波器还包括:整流桥5,所述滤波电路4和所述功率因数校正电路6之间连接所述整流桥5。其中输入为零线L、火线N和地线PE;输出为电源正极DC+和电源负极DC-。单相交流输入经过该滤波电路4,通过整流桥5,进入功率因数校正电路6后直流输出。

如图7所示,作为一种可选的实施方式,所述滤波电路4还包括:第一X电容7和第二X电容8,所述第一X电容7的一端与所述共模扼流线圈3的第一线圈15的输入端连接,所述第一X电容7的另一端与所述共模扼流线圈3的第二线圈16的输入端连接,所述第二X电容8的一端分别与所述第一线圈15的输出端、所述第一功率因数校正电感1的输入端和所述第二功率因数校正电感2的输入端连接,所述第一功率因数校正电感1的输出端和所述第二功率因数校正电感2的输出端均与电源的正极连接,所述第二X电容8的另一端和所述第二线圈16的输出端均与所述电源的负极连接。

作为一种可选的实施方式,所述滤波电路4还包括:第一Y电容9和第二Y电容10,所述第一Y电容9的一端分别与所述第一线圈15的输出端、所述第二X电容8的一端和所述第一功率因数校正电感1的输入端连接,所述第二Y电容10的一端分别与所述第二线圈16的输出端和所述负极连接,所述第一Y电容9的另一端与所述第二Y电容10的另一端均接地。

作为一种可选的实施方式,所述功率因数校正电路6还包括:第一钽电容13和第二钽电容14;所述第一钽电容13的一端分别与所述第一功率因数校正电感1的输出端、所述第二功率因数校正电感2的输出端和所述正极连接,所述第一钽电容13的另一端分别与所述第二X电容8的另一端和所述负极连接;所述第二钽电容14的一端分别与所述第一钽电容13的一端和所述正极连接,所述第二钽电容14的另一端分别与所述第一钽电容13的另一端与所述负极连接,利用钽电容的金属材料特性,可布局1-2个钽电容在共模扼流线圈3与PFC电感之间,屏蔽磁性器件间形成的漏磁耦合路径,从而增强滤波电路4的性能,此方法仅在PCB空间较大时可以使用。

作为一种可选的实施方式,所述功率因数校正电路6还包括:第一IGBT11和第二IGBT12;所述第一IGBT11的源极与所述第一功率因数校正电感1的输出端连接,所述第一IGBT11的漏极分别与所述第二X电容8的另一端和所述第一钽电容13的另一端连接;所述第二IGBT12的源极与所述第二功率因数校正电感2的输出端连接,所述第二IGBT12的漏极分别与所述第一IGBT11的漏极和所述第一钽电容13的另一端连接。

作为一种可选的实施方式,所述功率因数校正电路6还包括:第一二极管17和第二二极管18,第一二极管17的正极连接第一功率因数校正电感1的输出端,第一二极管17的负极连接电源正极;第二二极管18的正极连接第二功率因数校正电感2的输出端,第二二极管18的负极连接电源正极。

作为一种可选的实施方式,如图8-图10所示,PFC电感采用环形磁芯,磁芯竖装,所述第一功率因数校正电感1的线圈和所述第二功率因数校正电感2的线圈均为半结构绕法绕制的线圈,因为线圈与线圈之间可以看作是两个环形平面,根据电流流通的方向,在两个平面间产生矢量寄生电容,当绕线向上、再回绕向下时,在两个平面间产生等大反向的矢量电容效应会互相抵消,可以减少匝间寄生电容,增强电感的高频特性。

在某一变频空调测试中,外机控制器采用图1的布置,测试结果如图11所示,发现在低频测试超标,高频部分测试较差结果;同样方案,更改采用图3的布置,测试结果如图12所示,在低频和高频的问题均得到改善。

根据本发明提供的具体实施例,本发明公开了以下技术效果:

1、本实施例两个PFC电感的环形磁芯面相对,通过控制PFC电感的输入端子,使得分别在两个PFC磁芯面上产生的漏磁通方向大小相同,方向相反,并可以互相抵消,从而减少PFC电感产生的漏磁通与滤波电路的共模扼流线圈产生耦合。

2、钽电容的金属材料特性是可以将PFC电感的漏磁进行吸收,阻隔其漏磁传播至共模扼流线圈,从而增强共模扼流线圈的滤波性能,利用钽电容的金属材料特性,在PFC电感漏磁传递方向进行阻隔,减少漏磁线穿过共模扼流线圈,使得共模扼流线圈耦合电磁干扰变小,变相增强了滤波器的性能。

3、PFC电感采用环形磁芯,磁芯竖装,采用对半结构绕法,减少匝间寄生电容,可以增强电感的高频特性。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

- 一种单级滤波器

- 1×2单级隔离器与WDM滤波器叠加的混合器件