半导体标记制作方法及半导体标记

文献发布时间:2023-06-19 11:06:50

技术领域

本发明涉及半导体技术领域,尤其涉及一种半导体标记制作方法及半导体标记。

背景技术

在半导体制作过程中,尤其是DRAM(Dynamic Random Access Memory)的制作过程中,需要利用半导体标记辅助实现半导体结构与机台的对准等。相关技术中针对半导体标记的制作没有较为统一的方式,且整体制作效率较低。

发明内容

本发明提供一种半导体标记制作方法及半导体标记,以提高半导体标记的制作效率。

根据本发明的第一个方面,提供了一种半导体标记制作方法,包括:

提供周向边缘经OPC修正后的图形;

在图形上裁剪出多个独立的对准段;

拼接多个对准段,以形成周向边缘经OPC修正的半导体标记。

在本发明的一个实施例中,对准段包括经OPC修正的原始边缘和未经OPC修正的裁剪边缘;

其中,多个对准段的相应的裁剪边缘相拼接以形成半导体标记。

在本发明的一个实施例中,多个对准段包括:

第一对准段,第一对准段包括一个裁剪边缘;

第二对准段,第二对准段包括一个裁剪边缘,第一对准段与第二对准段相对接以形成第一半导体标记;

其中,第一对准段和第二对准段通过裁剪图形相对的两侧获得。

在本发明的一个实施例中,形成第一半导体标记后,半导体标记制作方法还包括:

将第一半导体标记依次裁剪为第一段、第二段以及第三段;

对接第一段和第三段,以形成第二半导体标记。

在本发明的一个实施例中,形成第一半导体标记后,半导体标记制作方法还包括:

将第一半导体标记裁剪为第一段和第二段;

将第一段和第二段相对且间隔设置,以形成第一填充区域;

在第一填充区域内填充第一补偿图形段,以形成第三半导体标记;

其中,第一补偿图形段在填充之前经OPC修正,或第一补偿图形段在填充之后经OPC修正。

在本发明的一个实施例中,多个独立的对准段包括:

第一对准段,第一对准段包括一个裁剪边缘;

第二对准段,第二对准段包括一个裁剪边缘;

将第一对准段和第二对准段相对且间隔设置,以形成第二填充区域;

在第二填充区域内填充第二补偿图形段,以形成第四半导体标记;

其中,将图形由中部剪开以获得第一对准段和第二对准段,第二补偿图形段在填充之前经OPC修正,或第二补偿图形段在填充之后经OPC修正。

在本发明的一个实施例中,多个独立的对准段包括:

第一对准段,第一对准段包括两个裁剪边缘;

第二对准段,第二对准段包括两个裁剪边缘;

第三对准段,第三对准段包括两个裁剪边缘;

第四对准段,第四对准段包括两个裁剪边缘;

将第一对准段、第二对准段、第三对准段以及第四对准段相对接,以形成第五半导体标记,第五半导体标记的面积小于图形的面积;

其中,第一对准段、第二对准段、第三对准段以及第四对准段通过裁剪图形的四个对角获得。

在本发明的一个实施例中,多个独立的对准段包括:

第一对准段,第一对准段包括两个裁剪边缘;

第二对准段,第二对准段包括两个裁剪边缘;

第三对准段,第三对准段包括两个裁剪边缘;

第四对准段,第四对准段包括两个裁剪边缘;

将第一对准段、第二对准段、第三对准段以及第四对准段相对接,以形成第五半导体标记,第五半导体标记的面积小于图形的面积;

其中,将图形沿相垂直的两个方向裁剪为四部分,然后分别进行二次裁剪以获得第一对准段、第二对准段、第三对准段以及第四对准段。

在本发明的一个实施例中,多个独立的对准段包括:

第一对准段,第一对准段包括两个裁剪边缘;

第二对准段,第二对准段包括两个裁剪边缘;

第三对准段,第三对准段包括两个裁剪边缘;

第四对准段,第四对准段包括两个裁剪边缘;

将第一对准段、第二对准段、第三对准段以及第四对准段相对且间隔设置,以形成第三填充区域;

在第三填充区域内填充第三补偿图形段,以形成第六半导体标记;

其中,将图形沿相垂直的两个方向裁剪以获得第一对准段、第二对准段、第三对准段以及第四对准段,第三补偿图形段在填充之前经OPC修正,或第三补偿图形段在填充之后经OPC修正。

在本发明的一个实施例中,多个独立的对准段包括:

第一对准段,第一对准段包括两个裁剪边缘,第一对准段呈L形;

第二对准段,第二对准段包括两个裁剪边缘,第二对准段呈直线形;

第三对准段,第三对准段包括两个裁剪边缘,第三对准段呈直线形;

将第二对准段与第一对准段相对接,第三对准段与第一对准段相对接,以形成第七半导体标记;

其中,第二对准段的长度等于第一对准段的一个裁剪边缘的长度,第三对准段的长度等于第一对准段的另一个裁剪边缘的长度。

在本发明的一个实施例中,多个独立的对准段包括:

第一对准段,第一对准段包括两个裁剪边缘,第一对准段呈L形;

第二对准段,第二对准段包括两个裁剪边缘,第二对准段呈直线形;

第三对准段,第三对准段包括两个裁剪边缘,第三对准段呈直线形;

将第二对准段与第一对准段相对接,第三对准段与第一对准段相对接,以形成第七半导体标记;

其中,第二对准段的长度等于第一对准段的一个裁剪边缘的长度,第三对准段的长度等于第一对准段的另一个裁剪边缘的长度减去第二对准段的宽度。

在本发明的一个实施例中,第一对准段和第二对准段由同一个图形上裁剪获得,第三对准段由另一个图形上裁剪获得。

在本发明的一个实施例中,第一对准段、第二对准段以及第三对准段均由同一个图形上裁剪获得,在裁剪获得第一对准段和第二对准段之后,对剩余的图形进行OPC修正,以裁剪获得第三对准段。

在本发明的一个实施例中,第一对准段、第二对准段以及第三对准段均由同一个图形上裁剪获得,在裁剪获得第一对准段和第二对准段之后,裁剪剩余的图形获得一裁剪段,对裁剪段进行OPC修正以获得第三对准段。

根据本发明的第二个方面,提供了一种半导体标记,包括根据上述的半导体标记制作方法获得的半导体标记。

本发明的半导体标记制作方法通过对周向边缘经OPC修正后的图形进行裁剪后拼接,以此获得周向边缘经OPC修正的半导体标记,即可以在多个对准段拼接后即可形成周向边缘经OPC修正的半导体标记,省去了形成半导体标记后再进行OPC修正的时间,以此提高半导体标记的制作效率。

附图说明

通过结合附图考虑以下对本发明的优选实施方式的详细说明,本发明的各种目标,特征和优点将变得更加显而易见。附图仅为本发明的示范性图解,并非一定是按比例绘制。在附图中,同样的附图标记始终表示相同或类似的部件。其中:

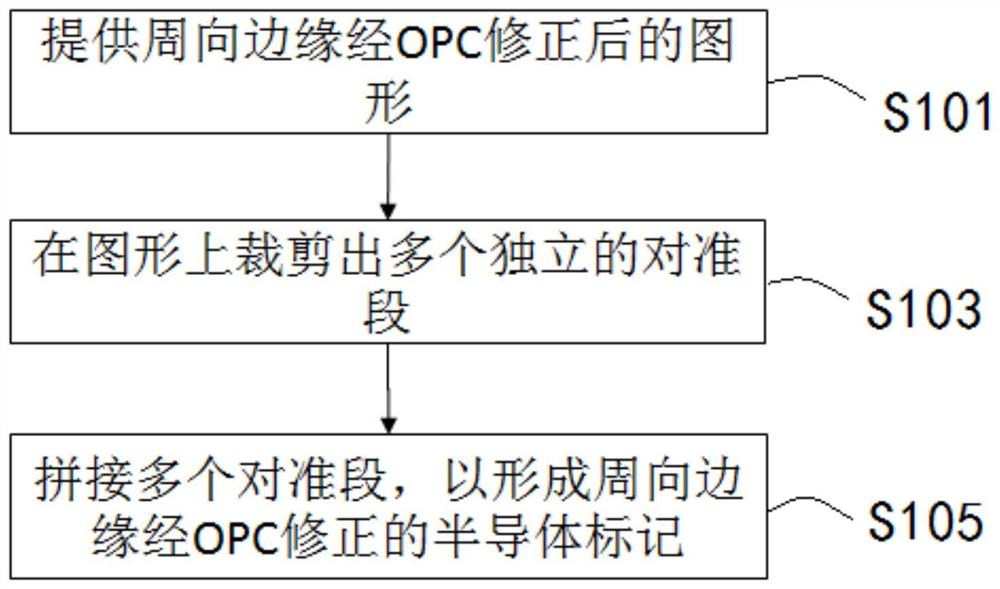

图1是根据一示例性实施方式示出的一种半导体标记制作方法的流程示意图;

图2是根据第一个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图3是根据第二个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图4是根据第三个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图5是根据第四个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图6是根据第五个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图7是根据第六个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图8是根据第七个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图9是根据第八个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图10是根据第九个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图11是根据第十个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图12是根据第十一个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图13是根据第十一个示例性实施方式示出的一种半导体标记制作方法的流程结构简易示意图;

图14是根据第十二个示例性实施方式示出的一种半导体标记制作方法的流程结构示意图;

图15是根据第十二个示例性实施方式示出的一种半导体标记制作方法的流程结构简易示意图。

附图标记说明如下:

10、图形;11、原始边缘;12、裁剪边缘;

13、第一对准段;14、第二对准段;20、第一半导体标记;

21、第一段;22、第二段;23、第三段;30、第二半导体标记;

24、第一段;25、第二段;1、第一填充区域;40、第三半导体标记;

131、第一对准段;141、第二对准段;2、第二填充区域;50、第四半导体标记;

16、第一对准段;17、第二对准段;18、第三对准段;19、第四对准段;60、第五半导体标记;

161、第一对准段;171、第二对准段;181、第三对准段;191、第四对准段;3、第三填充区域;70、第六半导体标记;

101、第一对准段;102、第二对准段;103、第三对准段;80、第七半导体标记。

具体实施方式

体现本发明特征与优点的典型实施例将在以下的说明中详细叙述。应理解的是本发明能够在不同的实施例上具有各种的变化,其皆不脱离本发明的范围,且其中的说明及附图在本质上是作说明之用,而非用以限制本发明。

在对本发明的不同示例性实施方式的下面描述中,参照附图进行,附图形成本发明的一部分,并且其中以示例方式显示了可实现本发明的多个方面的不同示例性结构,系统和步骤。应理解的是,可以使用部件,结构,示例性装置,系统和步骤的其他特定方案,并且可在不偏离本发明范围的情况下进行结构和功能性修改。而且,虽然本说明书中可使用术语“之上”,“之间”,“之内”等来描述本发明的不同示例性特征和元件,但是这些术语用于本文中仅出于方便,例如根据附图中的示例的方向。本说明书中的任何内容都不应理解为需要结构的特定三维方向才落入本发明的范围内。

本发明的一个实施例提供了一种半导体标记制作方法,请参考图1,半导体标记制作方法包括:

S101,提供周向边缘经OPC修正后的图形10;

S103,在图形10上裁剪出多个独立的对准段;

S105,拼接多个对准段,以形成周向边缘经OPC修正的半导体标记。

本发明一个实施例的半导体标记制作方法通过对周向边缘经OPC修正后的图形10进行裁剪后拼接,以此获得周向边缘经OPC修正的半导体标记,即可以在多个对准段拼接后即可形成周向边缘经OPC修正的半导体标记,省去了形成半导体标记后再进行OPC修正的时间,以此提高半导体标记的制作效率。

需要说明的是,光学邻近修正(Optical Proximity Correction,OPC)技术就是通过对图形做系统的改变,补偿图形的扭曲和偏移,使在晶片衬底上最终形成的曝光图形达到电路图形的设计要求。而本实施例中,通过选用经OPC修正后的图形10再对其进行裁剪,即裁剪出的至少部分的对准段经OPC修正,因此将多个对准段拼接后可以形成周向边缘经OPC修正的半导体标记。

在一个实施例中,对准段包括经OPC修正的原始边缘11和未经OPC修正的裁剪边缘12;其中,多个对准段的相应的裁剪边缘12相拼接以形成半导体标记。即待拼接的对准段按照相应的裁剪边缘12进行拼接,而经OPC修正的原始边缘11围成了半导体标记的周向边缘,因此最终形成的半导体标记是周向边缘经OPC修正的半导体标记。

在一个实施例中,多个对准段包括:第一对准段13,第一对准段13包括一个裁剪边缘12;第二对准段14,第二对准段14包括一个裁剪边缘12,第一对准段13与第二对准段14相对接以形成第一半导体标记20;其中,第一对准段13和第二对准段14通过裁剪图形10相对的两侧获得,即获得的第一对准段13和第二对准段14的相应的两个拐角处均是经OPC修正过的。

可选地,第一对准段13和第二对准段14可以通过裁剪图形10相对的两个对角形成。即裁剪图形10相对的两侧包括裁剪图形10的上下两侧,左右两侧,或者是相对的两个拐角。

在一些实施例中,如图2所示,半导体标记制作方法包括:

如图2(a)所示,提供一周向边缘经OPC修正后的图形10;

如图2(b)所示,剪切图形10上下两侧,以得到第一对准段13与第二对准段14;

如图2(c)所示,将第一对准段13的裁剪边缘12与第二对准段14的裁剪边缘12相对接形成第一半导体标记20。

在一些实施例中,如图5所示,半导体标记制作方法包括:

如图5(a)所示,提供一周向边缘经OPC修正后的图形10;

如图5(b)所示,剪切图形10左右两侧,以得到第一对准段13与第二对准段14;

如图5(c)所示,将第一对准段13的裁剪边缘12与第二对准段14的裁剪边缘12相对接形成第一半导体标记20。

在一些实施例中,在得到图2(b)或者如图5(b)所示的第一对准段13与第二对准段14后,可以将第一对准段13与第二对准段14的中间段切除后进行拼接,即将第一对准段13与第二对准段14剪短,以此拼接出来的半导体标记要比第一半导体标记20短。

在一个实施例中,形成第一半导体标记20后,半导体标记制作方法还包括:将第一半导体标记20依次裁剪为第一段21、第二段22以及第三段23;对接第一段21和第三段23,以形成第二半导体标记30。即通过将第一半导体标记20的中间部分去除,可以得到一个比第一半导体标记20短的第二半导体标记30。

在一些实施例中,如图3所示,半导体标记制作方法包括:

如图3(a)所示,形成一周向边缘经OPC修正后的第一半导体标记20;

如图3(b)所示,将第一半导体标记20剪切为三段,以得到第一段21、第二段22以及第三段23;

如图3(c)所示,将第一段21的裁剪边缘12和第三段23的裁剪边缘12相对接形成第二半导体标记30,即去除了第二段22。

在一些实施例中,如图6所示,半导体标记制作方法包括:

如图6(a)所示,形成一周向边缘经OPC修正后的第一半导体标记20;

如图6(b)所示,将第一半导体标记20剪切为三段,以得到第一段21、第二段22以及第三段23;

如图6(c)所示,将第一段21的裁剪边缘12和第三段23的裁剪边缘12相对接形成第二半导体标记30,即去除了第二段22。

需要说明的是,图3中的第一半导体标记20由图2的半导体标记制作方法获得,而图6中的第一半导体标记20由图5的半导体标记制作方法获得。

在一个实施例中,形成第一半导体标记20后,半导体标记制作方法还包括:将第一半导体标记20裁剪为第一段24和第二段25;将第一段24和第二段25相对且间隔设置,以形成第一填充区域1;在第一填充区域1内填充第一补偿图形段,以形成第三半导体标记40;其中,第一补偿图形段在填充之前经OPC修正,或第一补偿图形段在填充之后经OPC修正。即通过将第一半导体标记20由中间剪开,以此进行加长处理,从而得到一个比第一半导体标记20长的第三半导体标记40。

需要说明的是,第一补偿图形段是补充在第一段24和第二段25之间,因此在对其进行OPC修正时只是进行直边的修正,而不用进行拐角处修正,整个修正难度较低,因此修正的效率会相对较高。

在一些实施例中,如图4所示,半导体标记制作方法包括:

如图4(a)所示,形成一周向边缘经OPC修正后的第一半导体标记20;

如图4(b)所示,将第一半导体标记20剪切为两段,以得到第一段24和第二段25,且将第一段24的裁剪边缘12与第二段25的裁剪边缘12拉开后在二者之间形成了第一填充区域1;

如图4(c)所示,向第一填充区域1填充第一补偿图形段后得到了第三半导体标记40。

在一些实施例中,如图7所示,半导体标记制作方法包括:

如图7(a)所示,形成一周向边缘经OPC修正后的第一半导体标记20;

如图7(b)所示,将第一半导体标记20剪切为两段,以得到第一段24和第二段25,且将第一段24的裁剪边缘12与第二段25的裁剪边缘12拉开后在二者之间形成了第一填充区域1;

如图7(c)所示,向第一填充区域1填充第一补偿图形段后得到了第三半导体标记40。

需要说明的是,图4中的第一半导体标记20由图2的半导体标记制作方法获得,而图7中的第一半导体标记20由图5的半导体标记制作方法获得。

在一个实施例中,多个独立的对准段包括:第一对准段131,第一对准段131包括一个裁剪边缘12;第二对准段141,第二对准段141包括一个裁剪边缘12;将第一对准段131和第二对准段141相对且间隔设置,以形成第二填充区域2;在第二填充区域2内填充第二补偿图形段,以形成第四半导体标记50;其中,将图形10由中部剪开以获得第一对准段131和第二对准段141,第二补偿图形段在填充之前经OPC修正,或第二补偿图形段在填充之后经OPC修正。即通过将图形10由中间剪开,以此进行加长处理,从而得到一个比图形10长的第四半导体标记50。

在一些实施例中,如图8所示,半导体标记制作方法包括:

如图8(a)所示,提供一周向边缘经OPC修正后的图形10;

如图8(b)所示,将图形10剪切为两段,以得到第一对准段131和第二对准段141,且将第一对准段131的裁剪边缘12与第二对准段141的裁剪边缘12拉开后在二者之间形成了第二填充区域2;

如图8(c)所示,向第二填充区域2填充第二补偿图形段后得到了第四半导体标记50。

在一些实施例中,在图8的基础上,可以将图形10剪切为左右两段,然后依据上述制作方法得到一半导体标记。

在一个实施例中,多个独立的对准段包括:第一对准段16,第一对准段16包括两个裁剪边缘12;第二对准段17,第二对准段17包括两个裁剪边缘12;第三对准段18,第三对准段18包括两个裁剪边缘12;第四对准段19,第四对准段19包括两个裁剪边缘12;将第一对准段16、第二对准段17、第三对准段18以及第四对准段19相对接,以形成第五半导体标记60,第五半导体标记60的面积小于图形10的面积。

可选地,第一对准段16、第二对准段17、第三对准段18以及第四对准段19通过裁剪图形10的四个对角获得。即将图形10的中间部分进行去除,从而通过图形10的四个对角段拼接得到一个相对较小的第五半导体标记60。

在一些实施例中,如图9所示,半导体标记制作方法包括:

如图9(a)所示,提供一周向边缘经OPC修正后的图形10;

如图9(b)所示,剪切图形10的四个拐角段,以得到第一对准段16、第二对准段17、第三对准段18以及第四对准段19;

如图9(c)所示,将第一对准段16的一个裁剪边缘12与第二对准段17的一个裁剪边缘12相对接,第一对准段16的另一个裁剪边缘12与第三对准段18的一个裁剪边缘12相对接,第二对准段17的另一个裁剪边缘12与第四对准段19的一个裁剪边缘12相对接,第三对准段18的另一个裁剪边缘12与第四对准段19的另一个裁剪边缘12相对接,以形成第五半导体标记60。

可选地,将图形10沿相垂直的两个方向裁剪为四部分,然后分别进行二次裁剪以获得第一对准段16、第二对准段17、第三对准段18以及第四对准段19。即先将图形10裁剪为四部分,然后在将裁剪出来的四部分剪小以此得到相对较小的第一对准段16、第二对准段17、第三对准段18以及第四对准段19。

在一些实施例中,如图10所示,半导体标记制作方法包括:

如图10(a)所示,提供一周向边缘经OPC修正后的图形10;

如图10(b)所示,将图形10裁剪为四部分,以得到第一对准段161、第二对准段171、第三对准段181以及第四对准段191;

如图10(c)所示,对第一对准段161、第二对准段171、第三对准段181以及第四对准段191分别进行裁剪,得到第一对准段16、第二对准段17、第三对准段18以及第四对准段19;

如图10(d)所示,将第一对准段16的一个裁剪边缘12与第二对准段17的一个裁剪边缘12相对接,第一对准段16的另一个裁剪边缘12与第三对准段18的一个裁剪边缘12相对接,第二对准段17的另一个裁剪边缘12与第四对准段19的一个裁剪边缘12相对接,第三对准段18的另一个裁剪边缘12与第四对准段19的另一个裁剪边缘12相对接,以形成第五半导体标记60。

在一个实施例中,多个独立的对准段包括:第一对准段161,第一对准段161包括两个裁剪边缘12;第二对准段171,第二对准段171包括两个裁剪边缘12;第三对准段181,第三对准段181包括两个裁剪边缘12;第四对准段191,第四对准段191包括两个裁剪边缘12;将第一对准段161、第二对准段171、第三对准段181以及第四对准段191相对且间隔设置,以形成第三填充区域3;在第三填充区域3内填充第三补偿图形段,以形成第六半导体标记70;其中,将图形10沿相垂直的两个方向裁剪以获得第一对准段161、第二对准段171、第三对准段181以及第四对准段191,第三补偿图形段在填充之前经OPC修正,或第三补偿图形段在填充之后经OPC修正。即通过将图形10裁剪为四部分,并在其中间填充第三补偿图形,以此得到一个面积较大的第六半导体标记70。

在一些实施例中,如图11所示,半导体标记制作方法包括:

如图11(a)所示,提供一周向边缘经OPC修正后的图形10;

如图11(b)所示,将图形10裁剪为四部分,以得到第一对准段161、第二对准段171、第三对准段181以及第四对准段191,且将第一对准段161的一个裁剪边缘12与第二对准段171的一个裁剪边缘12相对且间隔设置,第一对准段161的另一个裁剪边缘12与第三对准段181的一个裁剪边缘12相对且间隔设置,第二对准段171的另一个裁剪边缘12与第四对准段191的一个裁剪边缘12相对且间隔设置,第三对准段181的另一个裁剪边缘12与第四对准段191的另一个裁剪边缘12相对且间隔设置,即在第一对准段161、第二对准段171、第三对准段181以及第四对准段191之间形成了第三填充区域3;

如图11(c)所示,向第三填充区域3填充第三补偿图形段后得到了第六半导体标记70。

需要说明的是,图2至图11中得到的半导体标记可以为叠对精准测量标识(overlay,OVL mark)。

在一个实施例中,多个独立的对准段包括:第一对准段101,第一对准段101包括两个裁剪边缘12,第一对准段101呈L形;第二对准段102,第二对准段102包括两个裁剪边缘12,第二对准段102呈直线形;第三对准段103,第三对准段103包括两个裁剪边缘12,第三对准段103呈直线形;将第二对准段102与第一对准段101相对接,第三对准段103与第一对准段101相对接,以形成第七半导体标记80,即通过裁剪出一L形的第一对准段101后,在对接第二对准段102和第三对准段103时第一对准段101形成了一个对准标准,从而可以提高对接效率。

可选地,第二对准段102的长度等于第一对准段101的一个裁剪边缘12的长度,第三对准段103的长度等于第一对准段101的另一个裁剪边缘12的长度,即在形成第七半导体标记80后,第二对准段102和第三对准段103的部分相重叠。

在一些实施例中,如图12所示,半导体标记制作方法包括:

如图12(a)所示,提供一个或多个周向边缘经OPC修正后的图形10;

如图12(b)所示,在一个或多个图形10的四周裁剪出第一对准段101、第二对准段102以及第三对准段103;

如图12(c)所示,将第一对准段101的一个裁剪边缘12与第二对准段102的一个裁剪边缘12相对接,第一对准段101的另一个裁剪边缘12与第三对准段103的一个裁剪边缘12相对接,以形成第七半导体标记80,其中,第二对准段102和第三对准段103在第一对准段101的拐角处相重叠。

结合图13可以看出,如图13(a)所示,裁剪图形10的两侧侧部,从而形成了L形的第一对准段101。如图13(b)所示,裁剪图形10的第三个侧部,从而形成了直线形的第二对准段102。如图13(c)所述,裁剪图形10的第四个侧部,从而形成了直线形的第三对准段103。其中,第二对准段102的长度等于第一对准段101的一个裁剪边缘12的长度,第三对准段103的长度等于第一对准段101的另一个裁剪边缘12的长度。

需要说明的是,图13所示实施例中,第一对准段101、第二对准段102以及第三对准段103至少通过两个图形10裁剪获得。在一些实施例中,在裁剪出第一对准段101、第二对准段102以及第三对准段103后可以将其进行二次裁剪,即可以去掉中间段,或者可以将其由中部剪开,进行加长,此处不作限定可以根据实际需求进行调整。

可选地,第二对准段102的长度等于第一对准段101的一个裁剪边缘12的长度,第三对准段103的长度等于第一对准段101的另一个裁剪边缘12的长度减去第二对准段102的宽度,即在形成第七半导体标记80后,第二对准段102和第三对准段103的部分正好对接。

在一些实施例中,如图14所示,半导体标记制作方法包括:

如图14(a)所示,提供一个或多个周向边缘经OPC修正后的图形10;

如图14(b)所示,在一个或多个图形10的四周裁剪出第一对准段101、第二对准段102以及第三对准段103;

如图14(c)所示,将第一对准段101的一个裁剪边缘12与第二对准段102的一个裁剪边缘12相对接,第一对准段101的另一个裁剪边缘12与第三对准段103的一个裁剪边缘12相对接,以形成第七半导体标记80,其中,第二对准段102和第三对准段103在第一对准段101的拐角处正好对接,不存在重叠部分。

结合图15可以看出,如图15(a)所示,裁剪图形10的两侧侧部,从而形成了L形的第一对准段101。如图15(b)所示,裁剪图形10的第三个侧部,从而形成了直线形的第二对准段102。如图15(c)所述,裁剪图形10的第四个侧部,从而形成了直线形的第三对准段103。其中,第二对准段102的长度等于第一对准段101的一个裁剪边缘12的长度,第三对准段103的长度等于第一对准段101的另一个裁剪边缘12的长度。

需要说明的是,图15所示实施例中,第一对准段101、第二对准段102以及第三对准段103至少通过两个图形10裁剪获得。在一些实施例中,在裁剪出第一对准段101、第二对准段102以及第三对准段103后可以将其进行二次裁剪,即可以去掉中间段,或者可以将其由中部剪开,进行加长,此处不作限定可以根据实际需求进行调整。

在一个实施例中,第一对准段101和第二对准段102由同一个图形10上裁剪获得,第三对准段103由另一个图形10上裁剪获得,即由图形10上直接裁剪即可获得分别具有两个裁剪边缘12的第一对准段101、第二对准段102以及第三对准段103。

可选地,第一对准段101、第二对准段102以及第三对准段103均由同一个图形10上裁剪获得,在裁剪获得第一对准段101和第二对准段102之后,对剩余的图形10进行OPC修正,以裁剪获得第三对准段103。在由一个图形10上裁剪获得第一对准段101、第二对准段102以及第三对准段103时,则可以先裁剪获得第一对准段101和第二对准段102,继续裁剪时,则需要对裁剪后的图形10进行OPC修正,保证其某一个拐角经过OPC修正,从而使得裁剪获得的第三对准段103也仅包括两个裁剪边缘12。

可选地,第一对准段101、第二对准段102以及第三对准段103均由同一个图形10上裁剪获得,在裁剪获得第一对准段101和第二对准段102之后,裁剪剩余的图形10获得一裁剪段,对裁剪段进行OPC修正以获得第三对准段103。即在由一个图形10上裁剪获得第一对准段101、第二对准段102以及第三对准段103时,则可以先裁剪获得第一对准段101和第二对准段102,然后继续裁剪得到一个具有三个裁剪边缘12的裁剪段,并对其拐角进行OPC修正,从而得到仅包括两个裁剪边缘12的第三对准段103。

需要说明的是,对于由一个图形10上裁剪获得第一对准段101、第二对准段102以及第三对准段103的实施例,需要考虑具体半导体标记的长度,当然在某些情况下可以通过添加补偿图形段即可。

需要说明的是,图12至图15中得到的半导体标记可以为切割标识(Dicing mark)。

本发明的一个实施例还提供了一种半导体标记,包括根据上述的半导体标记制作方法获得的半导体标记。

本实施例中的半导体标记可以根据具有的尺寸要求依据上述半导体标记制作方法获得。

本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本发明的其它实施方案。本发明旨在涵盖本发明的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本发明的一般性原理并包括本发明未公开的本技术领域中的公知常识或惯用技术手段。说明书和示例实施方式仅被视为示例性的,本发明的真正范围和精神由前面的权利要求指出。

应当理解的是,本发明并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本发明的范围仅由所附的权利要求来限制。

- 半导体标记制作方法及半导体标记

- 半导体硅片对准标记制作方法及其制作的半导体硅片