非易失性存储器单元的编程方法及非易失性存储器设备

文献发布时间:2023-06-19 11:11:32

相关申请的交叉引用

本申请要求于2019年11月30日提交的美国临时申请序列号62/942,086的权益,该申请的名称为“Accurate Synapse Programming Method”。

技术领域

本发明涉及非易失性存储器技术。具体来说,本发明描述了能使存储器单元电流在预定的目标电流范围内流动的逻辑兼容闪存的编程脉冲宽度控制方案。

背景技术

闪存是一种即使系统电源断开也能永久存储信息的典型的非易失性存储器。逻辑兼容闪存(logic compatible flash memory)是一类仅用逻辑器件构建的闪存。图1以多行和多列的2D形式示出了传统的存储器单元阵列100。该存储器单元阵列100的结构包括多行和多列的逻辑兼容的闪存单元,即“单元A1”、“单元A2”和“单元A3”至“单元C1”、“单元C2”和“单元C3”。位线在构成列的多个单元旁边延伸。每条位线将同一列中的多个单元连接到位于该列的端部处的一个感测放大器电路。该存储器单元能基于单元中的存储信息来调节它的电流电平。感测放大器通过感测电流电平来确定单元状态。即使未在图1中描绘出,也存在一组与在每一行中排列的单元A、单元B和单元C连接的控制线(读取线)以用于存储器操作,诸如放电或使存储器单元放电。给定该存储器单元阵列,当仅针对一些存储器单元选择性地执行编程操作并且当那些单元(即,单元A1、B1和C1)共享公共读取线时,未选择的存储器单元(例如,单元C1)应不受所选择的存储器单元(例如,单元A1和单元B1)的编程操作的影响,并且必须维持其原始状态。

发明内容

本发明公开了一种对由标准逻辑器件组成的非易失性存储器进行选择性地编程的方法。根据本发明,对存储器阵列中的非易失性存储器单元进行编程的方法,包括:向所选择的待编程的存储器单元和未选择的存储器单元两者施加预定义的编程脉冲,未选择的存储器单元将不因所选择的存储器单元的编程而改变或者即使以某种程度改变,未选择的存储器单元也仅在预定的可允许范围内被改变;将未选择存储器单元的区域升压;设置预定义的编程脉冲的阈值时间,其中,阈值时间定义为未选择的存储器单元的浮置栅极与未选择的存储器单元的所升压的区域之间的电压差异的绝对值达到定义的阈值时的时间。

在一个实施例中,该方法还包括:将编程脉冲施加到存储器阵列中的未选择的存储器单元,直到阈值时间为止;以及使未选择的存储器单元的电压电位升压,直到阈值时间为止。在一个实施例中,编程脉冲在阈值时间处或阈值时间附近开始下降到接地电位。而且,在另一实施例中,阈值是用以禁止未选择的存储器单元的不需要的编程的未选择的存储器单元的浮置栅极与未选择的存储器单元的所升压的区域之间的最大电压差异。

在一个实施例中,预定义的编程脉冲被施加到与所选择的存储器单元和未选择的存储器单元连接的栅极线。在另一实施例中,未选择的存储器单元的所升压的区域包括未选择的存储器单元的形成在相应衬底上的源极区域、漏极区域以及在源极区域和漏极区域之间的沟道区域。在一个实施例中,所升压的区域通过未选择的存储器单元的浮置栅极上的电压电位而被升压到特定电压电平。在另一实施例中,预定义的编程脉冲的电压电平设定得足够低,以使得在所选择的存储器单元正在编程的同时,未选择的存储器单元的浮置栅极与所升压的区域之间的电压差异低至足以防止未选择的存储器单元的编程。

在一个实施例中,预定义的编程脉冲的在上升之后和在下降之前的持续时间保持足够长,只要预定义的编程脉冲在阈值时间处或阈值时间附近低至接地电位或大致接地电位即可。在本发明的一个实施例中,非易失性存储器设备包括:被配置为施加预定义的编程脉冲的电压信号脉冲生成器;以及非易失性存储器单元阵列。在一个实施例中,电压信号脉冲生成器被配置为生成具有预定义的编程脉冲的用于存储器单元阵列中的非易失性存储器单元的信号,以发送至选择的待编程的存储器单元和未选择的存储器单元两者,未选择的存储器单元将不因选择的存储器单元的编程而改变,或者即使在一定程度上改变,未选择的存储器单元也仅在预定的范围内改变。在另一实施例中,电压信号脉冲生成器还被配置为设定预定义的编程脉冲的阈值时间,其中,阈值时间定义为未选择的存储器单元的浮置栅极与未选择的存储器单元的升压区域之间的电压差异的绝对值达到定义的阈值时的时间。

附图说明

通过参照附图的以下描述,对于本领域技术人员而言,本发明的特征将变得显而易见。要理解的是,附图仅描绘了本发明的典型实施例,并且因此将不被视为对范围的限制,本发明通过使用附图以额外的特定性和细节来描述,在附图中:

图1示出了具有多行和多列的非易失性存储器单元阵列结构。

图2A和图2B示出了根据本发明的实施例的用于基于自升压禁止方案(self-boosting inhibit scheme)来选择性编程的偏置的逻辑兼容闪存单元的电路图。

图3A至图3H示出了根据本发明的实施例的用于基于自升压禁止方案来选择性编程的偏置的逻辑兼容闪存单元的另一电路图。

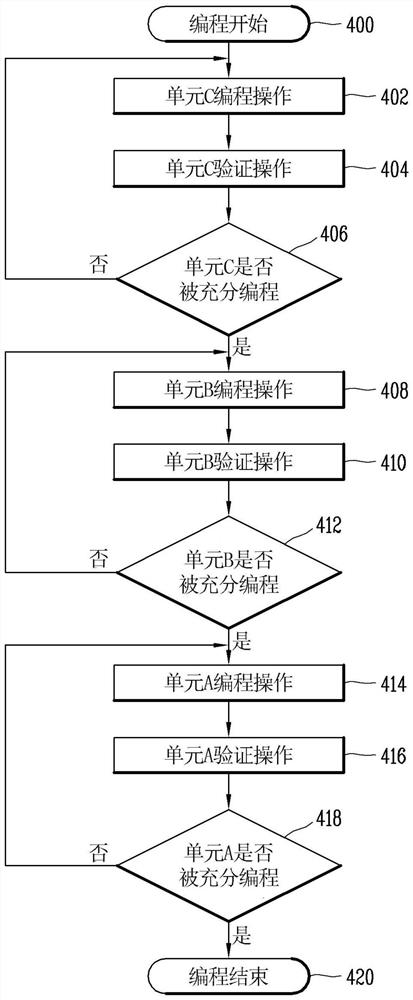

图4是描绘图3A至图3H中所示的对存储器单元进行编程的方法的流程图。

图5是描述用于对所选择的行存储器单元进行编程的各种电压信号的时序图。

图6示出了在存储器单元编程和验证迭代期间施加到图2A和图2B中的存储器单元阵列的控制栅极线CG1、CG2的两个示例性脉冲。

图7示出了根据本发明的实施例的形成在P掺杂本体上的逻辑兼容闪存单元的一系列晶体管的横截面与编程禁止偏置条件的图示。

图8A和图8B示出了根据一个实施例的施加到未选择的存储器单元的浮置栅极FG和升压节点的示例性电压脉冲。

图9示出了根据本发明的实施例的具有电压信号脉冲生成器和非易失性存储器单元阵列的框图。

图10示出了根据本发明的实施例的包括中央处理单元(CPU)、易失性存储器和部署脉冲宽度控制编程方案的非易失性存储器的芯片。

具体实施方式

图2A和图2B示出了描绘用于擦除和编程操作的布置在同一行中的两个逻辑兼容闪存单元的电路图。图2A和图2B中的每个存储器单元能够是图1中描绘的存储器单元。该闪存单元是逻辑兼容的,因为单元中的所有的单位器件使用标准逻辑器件来构建。图2A示出了为擦除操作而偏置的存储器单元。图2B示出了为编程操作而偏置的存储器单元。

存储器单元A和B中的每个包括漏极选择晶体管212/232、源极选择晶体管216/236和联接到一对控制栅极218和220(针对单元A)以及238和240(针对单元B)的读取晶体管214/234。单元A和B共享沿着行的控制栅极线CG1/CG2、选择栅极线SG1/SG2和源极线SL。然而,单元A和B分别连接到其各自的位线BL_A、BL_B。单元A经由漏极选择晶体管212连接到位线BL_A。单元B经由漏极选择晶体管232连接到位线BL_B。单元A中的读取晶体管214连接到形成浮置栅极FGA的一对控制栅极晶体管218和220。单元B中的读取晶体管234连接到形成浮置栅极FGB的一对控制栅极晶体管238和240。此外,与连接到下控制栅极线CG2的下控制栅极晶体管220和240相比,连接到上控制栅极线CG1的上控制栅极晶体管218和238尺寸变大。结果是,浮置栅极FGA和FGB的电压电位被保持为接近第一控制栅极线CG1的电压。

单元A中的浮置栅极FGA和单元B中的浮置栅极FGB电容性地联接到它们的相应的控制栅极:针对单元A的控制栅极218、220,以及针对单元B的控制栅极238、240。因此,单元A和B能各自存储阈值电压的形式的数据、相应单元能开启时的最低电压。阈值电压由保留在单元A的浮置栅极FGA、单元B的浮置栅极FGB上的电荷量控制。也就是说,在读取晶体管导通以允许它的源极和漏极之间的导通之前,依据浮置栅极FGA和FGB上的电荷的水平,一定电平的电压必须施加到控制栅极线CG1和CG2,在读取操作期间,电流在单元A和B中的每个的选择晶体管之间流动。浮置栅极FGA和FGB能存储两个或多于两个的状态。关于该两个状态,单元A、B能被编程或擦除。当单元A和B处于完全擦除状态时,数量稀少的电子被捕获在单元A和B中的每个中的浮置栅极(FG)节点中;因此,单元在读取操作期间能流过大量电流。当单元处于完全编程状态时,大量电子被存储在逻辑兼容闪存单元的FG节点中;因此,单元在读取操作期间流过少量电流。

图2A示出了用于擦除操作的存储器单元A和B这两者的偏置条件。擦除操作通过去除每个存储器单元中浮置栅极上的电子的处理而发生。针对这种情况,将高的正电压HV(大约+10V)施加到选择栅极线CG2,并且将接地电压施加到选择栅极线CG1。都连接到CG1的上控制栅极218和238的尺寸显著大于都连接到CG2的下控制栅极220和240。因此,上栅极的电压导致FG节点电压电位接近接地电压电位。因此,下控制栅极与浮置栅极的这个接近接地电压电位之间的电压差异足以通过下控制栅极(low control gate)来排斥浮置栅极内部的捕获的负电荷。

图2B示出了用于使用自升压禁止方案来选择性编程的闪存单元偏置条件。这里,存储器单元A和B这两者共享行信号线SG1、CG1、CG2、SG2、SL。单元A被偏置以被编程并且单元B被升压以不受单元A的编程的影响。针对这个选择性编程方案,高编程电压HV被施加到控制栅极。特定电源电压VDD被施加到第一选择栅极线SG1和源极线SL。GND电平被施加到第二选择栅极线SG2。为了对单元A1进行编程,单元A1中的漏极选择晶体管212被设定为导通,位线BL_A接地,并且电源电压VDD被施加到单元A1中的漏极选择晶体管212的栅极。结果是,存储器单元A1中的漏极选择晶体管212被偏置为导电状态(即,“导通”)。单元A中的源极选择晶体管216通过使晶体管的栅极接地而截止。然后,当将编程电压HV(即,几乎8V)施加到控制栅极线CG1和CG2时,单元A的浮置栅极FGA与单元A中的读取晶体管214的电子沟道之间的电压差异变得足够高。因此,电子通过福勒—诺德海姆(Fowler-Nordheim)隧穿注入到浮置栅极FGA中,并且当电子在那里蓄积时,浮置栅极带负电,然后单元A的阈值电压升高。单元A1的阈值电压响应于存储的电子而指示编程状态。

单元B是编程中未选择的存储器单元。因此,单元B被偏置以保持它的原始存储器状态(位信息),不因单元A的编程操作而改变,或者即使在一定程度上被改变,它也仅在预定的可允许范围内被改变。为了这个目的,位线BL_B和单元B中的漏极选择晶体管232的栅极被设定为电源电压VDD,因此漏极选择晶体管232截止。单元B中的源极选择晶体管236也被设定为截止。虽然源极选择晶体管236的源极接收高于0V的VDD,但是源极选择晶体管236因为其栅极经由第二选择栅极线SG2而接地,所以源极选择晶体管236截止。因此,通过使漏极选择晶体管232和源极选择晶体管236截止,读取晶体管234下的电子沟道被电隔离。当它发生时,单元B中的读取晶体管234的源极、漏极和电子沟道变得与位线BL_B电隔离并且进入“浮置状态”。读取晶体管234电容性地联接到由控制栅极线CG1和CG2充电的大面积的浮置栅极FGB。因此,响应于控制栅极线CG1和CG2上的编程电压,读取晶体管234将被自升压到足够高的电压电平,从而通过减小电压差异至低于用于使电子注入到浮置栅极FGB中的最小电压来禁止单元B的不需要的编程。电子沟道升压至编程电压HV的一半或几乎一半(即,差不多8伏的一半:4伏)。在这个偏置条件下,浮置栅极FGB和电子沟道之间的电压差异旨在足够小,以禁止电子从电子沟道到浮置栅极FGB的隧穿。然而,由于浮置栅极FGB和电子沟道之间的电压差异,仍可能发生一定数量的不需要的电子隧穿。因此,单元B的状态可以改变到一定水平(即,被干扰),并且当它超过由(图1中所描绘的)感测放大器限定的预定义的阈值时,那么感测放大器电路可在对单元进行读取操作期间输出不正确的值。然而,如果所改变的水平未超过预定义的阈值,那么具有足够高的精度的感测放大器电路仍会在读取操作期间输出正确的值。注意的是,具有更高精度的感测放大器电路比具有更低精度的感测放大器电路更复杂并且更大。因此,优选的是,限制或减少在编程操作期间引起干扰的不需要的电子隧穿的量,以使得在单元的读取操作期间,能使用不太复杂和紧凑的感测放大器来感测来自单元的正确输出。

图3A至图3H示出了用于一系列存储器操作:擦除、编程和读取的闪存单元阵列的偏置条件。单元A、B和C分别连接到位线BL_A、BL_B和BL_C。每一串中的各个单元的控制栅极连接到一对控制栅极线CG1/CG2。单元A中的漏极选择晶体管322将存储器单元A连接到位线BL_A。单元B中的漏极选择晶体管342将存储器单元B连接到位线BL_B。单元C中的漏极选择晶体管362将存储器单元C连接到位线BL_C。每个存储器单元中的漏极选择晶体管连接到第一选择栅极线SG1,并且每个单元中的源极选择晶体管连接到第二选择栅极线SG2。图3A示出了用于单元A、B和C的擦除操作的偏置条件。在编程之前,通过向第二控制栅极线CG2施加约10伏的高压HV来对存储器单元A、B和C进行擦除。经擦除的存储晶体管能存储数据“1”。

图3B示出了用于仅对阵列中的单元C进行编程的偏置条件。通过向控制栅极线CG1和CG2施加高电压HV_C并且使位线BL_C接地,朝向在位线BL_C上流动的电流电平C对存储器单元C进行编程。然而,单元C的编程不影响单元A和B,并且即使单元A和B在一定程度上被改变,它们也仅在预定义的可允许范围内变化,因为当通过控制栅极线CG1/CG2接收高电压HV_C时,它们的位线BL_A和BL_B通过电源电压VDD进行偏置。

图3C示出了用于验证被编程的单元C的存储器单元的偏置条件。一旦执行了对存储器单元C的编程操作,就在控制栅极线CG1和CG2以读取电压VRD_C被偏置的同时,通过感测位线BL_C中的电流电平Cur_C1来执行确保单元C是否被充分编程的内部检查。如果存储器单元C响应于读取电压VRD_C而传导了大于目标电平的电流,则单元C的状态未被正确编程。否则,如果单元C响应于读取电压VRD_C而传导了具有目标电平或小于目标电平的电流,则单元C被正确编程。如图3B和图3C中所示,该编程-验证步骤将被重复,直到单元C能在读取操作期间传导具有电流电平C的电流。在对存储器单元C执行该编程-验证操作期间,存储器单元A和B将通过被禁止编程来维持或保持接近擦除条件。

图3D示出了在验证经编程的存储器单元C之后对单元B进行编程的偏置条件。然后,通过向控制栅极线CG1和CG2施加高电压HV_B并且将位线BL_B接地来执行存储器单元B的编程。然而,在通过控制栅极线CG1/CG2来接收大的正电压HV_B时,通过将存储器单元A和C各自的位线偏置到电源电压VDD来禁止对存储器单元A和C进行编程。

图3E示出了用于验证存储器单元B的存储器单元的偏置条件。一旦执行了对存储器单元B的编程操作,则在控制栅极线CG1和CG2以读取电压VRD_B被偏置的同时,通过感测位线BL_B中的电流电平Cur_B1来执行确保存储器单元B是否被充分编程的内部检查。如果存储器单元B响应于读取电压VRD_B而传导大于目标电平的电流,则存储器单元B的状态未被正确编程。否则,如果存储器单元B响应于读取电压VRD_B而传导具有目标电平或小于目标电平的电流,则存储器单元B被正确编程。如图3D和图3E中所示,该编程-验证步骤将被重复,直到存储器单元B能在读取操作期间传导具有电流电平B的电流。在存储器单元B的编程-验证操作期间,存储器单元A和C保持它们的条件(未被单元B的操作改变),或者即使出现变化,它们仍保持在预定义的可允许范围内(存储器单元A为擦除状态,存储器单元C为编程状态)。

图3F示出了用于在验证存储器单元B之后对存储器单元A进行编程的偏置条件。与其它存储器单元B和C一样,通过向控制栅极线CG1和CG2施加高电压HV_A并且使位线BL_A接地来执行存储器单元A的编程。另一方面,在通过控制栅极线CG1/CG2接收大的正电压HV_A时,通过将存储器单元B和C各自的位线偏置到电源电压VDD,来禁止对存储器单元B和C进行编程。

图3G示出了用于验证存储器单元A已经被正确编程的存储器单元的偏置条件。一旦执行了存储器单元A的编程,就在控制栅极线CG1和CG2以读取电压VRD_A被偏置的同时,通过感测位线BL_A上的电流电平Cur_A1来执行确保存储器单元A是否被充分编程的内部检查。如果存储器单元A响应于读取电压VRD_A而传导大于目标电平的电流,则存储器单元A的状态未被正确编程。否则,如果存储器单元A响应于读取电压VRD_A而传导具有目标电平或小于该目标电平的电流,则存储器单元A被正确编程。如图3F和图3G中所示,该编程-验证步骤将被重复,直到存储器单元A在读取操作期间能传导具有电流电平A的电流。在对存储器单元A执行编程-验证操作期间,存储器单元B和C保持它们的条件(未被单元A的操作改变),或者即使出现变化,它们仍保持在预定义的可允许范围内(存储器单元B和C为编程状态),被保护免受由存储器单元A的编程而导致的任何不需要的(编程)干扰。

图3H示出了闪存单元A、B和C分别执行读取操作的偏置状态。在对所有存储器单元A、B和C进行编程之后,能通过向控制栅极信号CG1和CG2施加读取电压VRD来读取存储的单元值。如先前通过图3A至图3G所描述的,在未选择的存储器单元不受编程影响的同时,对所选择的存储器单元进行编程,或者即使被影响,通过实现单元的编程禁止偏置条件,未选择的存储器单元也仅在可允许的范围内受影响。并且来自单元A、B和C的单元电流应分别接近它们的目标电流电平Cur_A、Cur_B和Cur_C。

图4是描绘对图3A至图3H中所示的非易失性存储器单元进行编程的方法的流程图。在步骤400,待编程的存储器单元A、B和C被擦除。在步骤402,实施存储器单元C的编程。第一编程电压被施加到控制栅极线CG1和CG2,并且使它的联接的位线BL_C接地。在步骤404,验证存储器单元C的状态。为了确定存储器单元C是否被正确编程,通过向控制栅极线CG1和CG2施加基准电压VRD_C来读取存储器单元C的内容。在步骤406,如果存储器单元C通过位线BL_C传导高于目标电平的电流,则存储器单元C未以目标电平被正确编程。在那种情况下,将重复编程操作步骤402和验证操作步骤404,直到通过感测它的传导电流来确定存储器单元C被正确地编程。如果存储器单元C传导低于目标电平的电流或具有目标电平的电流Cur_C1,存储器单元C被验证为正确编程。

在步骤408,在发现存储器单元C被正确编程之后,通过将存储器单元B的位线BL_B偏置到大约接地电平来实施存储器单元B的编程。而且,位线BL_A和BL_C被电源电压VDD偏置以保护其它存储器单元A和C免受由存储器单元B的编程而导致的任何不需要的编程。在步骤410,验证存储器单元B的状态。像存储器单元C一样,为了确定存储器单元B的状态(它是被编程还是被擦除),通过向连接至存储器单元B的控制栅极线施加大致的基准电压VRD_B来读取存储器单元B的内容。

在步骤412,如果存储器单元B通过位线BL_B传导高于目标电平的电流,则存储器单元B未被正确编程。在那种情况下,将重复步骤408和410的编程操作和验证操作,直到通过感测它的传导电流来确定存储器单元B被正确编程。如果存储器单元B传导低于目标电平的电流或具有目标电平的电流Cur_B1,则存储器单元B被验证为正确编程。

在步骤414,在确定正确编程存储器单元B之后,则在将其它存储器单元B和C偏置到电源电压VDD的同时,通过将存储器单元A的位线BL_A偏置到大约接地电平来实施存储器单元A的编程。因此,存储器单元B和C中存储的电子有限地受到存储器单元A的编程的影响。在步骤416,验证存储器单元A的状态。为了确定存储器单元A是否被正确编程,通过向连接到存储器单元A的控制栅极线施加大致的基准电压VRD_A来读取存储器单元A的内容。

在步骤418,如果存储器单元A通过位线BL_A传导目标电平或高于目标电平的电流,则存储器单元A未被正确编程。在那种情况下,将重复步骤414和416的编程操作和验证操作,直到通过感测它的传导电流来确定存储器单元A被正确编程。如果存储器单元A传导低于目标电平的电流Cur_A1,则存储器单元A被验证为正确编程。

在步骤420,一旦确定所有所选择的存储器单元A、B和C被正确编程,则逻辑兼容闪存的行存储器阵列的编程操作结束。由于针对每个单元设定了不同的目标编程电平,因此可选择性地对每个单元进行编程和验证,同时通过上述自升压技术来在很大程度上保护编程禁止的单元免受不需要的编程的影响。

图5是描述用于对所选择的行存储器单元进行编程的各种电压信号的时序图。该编程方法能通过图2A和图2B和图3A至图3H中所示的自升压方法来选择性地对行存储器阵列中的单元进行编程。控制栅极线CG1/CG2上的顺序电压包括编程电压脉冲和验证电压脉冲。编程脉冲的阶段由针对电压上升、编程和电压下降的时间构成。同样,验证脉冲的阶段由针对电压上升、验证和电压下降的时间构成。由于在存储器阵列中承载控制信号的长导线的显著(很大)的寄生电容,因此这些上升和下降时间能是整个编程时间中的很大一部分。

在图3A至图3H中对三个存储器单元A、B和C进行编程的输入电压信号在一定时间段内的组合顺序如下:在时间t0,将具有电源电压VDD的电源信号施加到选择栅极线SG1和源极线SL,使控制栅极线CG1/CG2接地,选择栅极线SG2具有接地电压。在控制栅极线CG1/CG2的电平从时间t0开始上升之后,在时间t1,它们被升高到目标编程电平。在时间t2,控制栅极线CG1/CG2的电平开始减小,并且在它们下降之后,在时间t3返回到接地电平。在时间t4,源极线SL上的电源电压VDD开始减小,直到它达到零伏。在时间t5,将验证脉冲施加到控制栅极线CG1/CG2,直到它到达目标电平。在时间t6,该验证脉冲减小到接地电平。在时间t7,电源信号将被施加到源极线SL,以使得它返回到电源电压VDD。一旦完成第一存储器单元C的编程,在规定的时间间隔后,重新开始针对下一存储器单元(即,单元B和A)的编程/验证脉冲的下一周期。

图6示出了在存储器单元编程和验证迭代期间在图3A至图3H中施加到存储器单元阵列的控制栅极线CG1、CG2的两个示例性脉冲。在图6中,上图和下图都示出了用于在图3A至图3H中将足够数量的电子捕获到存储器单元A、B和C的浮置栅极上的示例性编程脉冲序列。而且,如图5中所讨论的,在施加具有脉冲高电平宽度(pulse high width)T1或T2的每个编程脉冲后,在一些延迟之后将验证脉冲施加到控制栅极线CG1、CG2。

上图示出了三个编程/验证脉冲周期的序列。总累积的编程脉冲的高电平时间(programpulse high time)被计算为每个编程脉冲的高电平持续时间与为3的迭代次数的乘积。相反,下图示出了六个编程/验证脉冲周期的序列,每个编程脉冲的高电平持续时间为T2。因此,总累积的编程脉冲的高电平时间被计算为每个编程脉冲的高电平持续时间T2与为6的迭代次数的乘积。结果是,假定持续时间T1等于持续时间T2的大约两倍,针对两种情况(即,T1*3和T2*6)的累积的编程脉冲的高电平时间可以近似。因此,一旦施加了三次和六次迭代的编程-验证脉冲,就能完成存储器单元的编程。另一方面,具有持续时间T1或T2的编程脉冲均需要编程前的上升的时间和编程后的下降的时间。针对具有持续时间T1的编程脉冲对存储器单元进行编程,预计出现三个上升和下降周期的时间。另一方面,针对具有持续时间T2的编程脉冲对相同的存储器单元进行编程,预计出现六个上升和下降的周期的时间。

如果不管编程脉冲的高电平宽度如何,上升和下降的周期花费相同的时间,则与具有较短的脉冲高电平宽度T2的编程/验证迭代相比,需要较少的上升和下降的周期和较少的验证脉冲的具有较长的脉冲高电平宽度T1的编程/验证迭代,显著地减少了总编程/验证时间。换句话说,总编程时间在具有较长的编程脉冲宽度T1的情况下短多了,因为它可以平摊脉冲上升和下降的时序开销、验证脉冲时间以及脉冲之间的相关延迟。

图7示出了在P掺杂本体上形成的逻辑兼容闪存单元的一系列晶体管的横截面与编程禁止偏置条件的图示。在图7中,图2B中的“经由自升压禁止编程”的存储器单元B被形成在P掺杂衬底上。如先前所提及的,为了使漏极选择晶体管截止,晶体管的n+漏极区域(连接到位线BL)和晶体管的栅极(连接到选择栅极线SG1)都被偏置到VDD。而且,为了使源极选择晶体管截止,向晶体管的n+源极区域(连接到源极线SL)提供电源电压VDD,并且使晶体管的栅极(连接到选择栅极线SG2)接地。

用虚线示出的驱动到升压电压BV的升压节点包括安装在p衬底上的两条“导线”。导线中的第一个导线位于漏极选择晶体管(具有选择栅极线SG1)和读取晶体管之间,并且导线中的第二个导线位于源极选择晶体管(具有选择栅极线SG2)和读取晶体管之间。如早前所讨论的,读取晶体管的浮置栅极FG电联接到控制栅极线CG1、CG2,其中控制栅极线CG1、CG2承载与闪存阵列中的其它存储器单元共享的编程电压,并且浮置栅极FG联接到特定高电压HV。

当漏极选择晶体管和源极选择晶体管这两者截止时,定义为升压节点BV的区域变得电浮置。升压节点BV电容性地联接到浮置栅极FG以及P掺杂本体衬底。因此,当将高电压施加到浮置栅极时,升压节点将自升压到特定电压电平。理想地,浮置栅极FG与电子沟道之间的电压差异充分小,即使将编程电压施加到所选择的行存储器阵列中的相邻的存储器单元,也足以禁止电子从电子沟道隧穿到浮置栅极FG。

给定时间的升压节点电压能通过以下公式近似确定:升压节点电压(时间)=(近似=)Cap_A/(Cap_A+Cap_B)×FG电压-(i1+i2)*时间/(Cap_A+Cap_B),其中Cap_A表示FG与升压节点之间的电容,Cap_B表示升压节点与本体(GND)之间的电容,i1是从n+源极和漏极区域到本体的结漏电流(junction leakage current),以及i2是通过其栅极连接到选择栅极线SG1的漏极选择晶体管从升压节点到位线BL的亚阈值漏电流。即,虚线箭头中的“i1”表示到本体的结漏电流,并且虚线箭头中的“i2”表示通过漏极选择晶体管的亚阈值漏电流。

假设Cap_A能具有与Cap_B近似的值,则在编程脉冲上升到规定的高电平值时之后,升压节点立即具有升高到存储器单元B的浮置栅极FG的电压(=HV)的大约50%的自升压电压。然而,当编程脉冲被维持高电平时,到本体的结漏电流和通过漏极选择晶体管的亚阈值漏电流能释放升压节点电压。结果是,在一定时间后,浮置栅极与读取晶体管的电子沟道之间的电压差异变得足够高,从而允许从电子沟道到浮置栅极FG的福勒—诺德海姆隧穿,这对于编程禁止单元来说不是所期望的。当出现隧穿时,图2A和图2B中能出现针对存储器单元B的本不需要的编程,从而干扰了它的原始状态。

图8A和图8B示出了当在图2A和图2B和图3A至图3H中用相同的控制栅极脉冲对阵列中的所选择的存储器单元进行编程时,(1)控制栅极线CG1和CG2上的控制栅极电压脉冲的变化以及(2)由于图7中所描述的未选择的存储器单元的漏电流引起的升压节点电压的变化。所示的电压脉冲由至少三个阶段构成:电压上升阶段、编程阶段和电压下降阶段。

在时间t1和时间t2之间(上升时间),施加到控制栅极线CG1和CG2的电压信号从0V增加到目标编程电压电平,并且浮置栅极FG的电压通过与控制栅极线CG1和CG2的联接而增加到特定电压电平。然后,由于未选择的存储器单元的升压节点进入电隔离状态,即“浮置状态”,如图2B中所描述的,升压节点电压通过与FG节点联接而增加到另一特定电压电平。在时间t2,编程阶段开始。时间t2之后,控制栅极线CG1/CG2维持在高编程电压,并且FG也维持在大致高电压电平。通过联接上拉FG节点的控制栅极线CG1和CG2的目标编程电压电平需要足够低(即,大约小于12V),以使得FG和升压节点之间的电压差异小于电压增量阈值(即,大约6V)。结果是,对于针对禁止编程单元,FG节点和升压节点之间的电压差异变得足够小,以防止在编程阶段开始时未选择的存储器单元发生不需要的电子隧穿。

然而,由于不需要的漏电流,升压节点电压在时间t2到达它的峰值之后可逐渐减小。在时间t3,下降阶段开始,并且控制栅极线CG1/CG2开始放电,直到它在时间t4达到几乎0V。而且,在时间t3,施加到升压节点的自升压电压开始下降,并且在时间t4低至约0V。在共享控制栅极线CG1和CG2被驱动到高电压编程电压电平时,在时间t2和时间Tth之间,浮置栅极FG和升压节点之间的电压差异的大小(电压增量)充分低,足以禁止未选择的存储器单元的不需要的编程,同时,通过电子的福勒—诺德海姆隧穿对所选择的行存储器阵列中的所选择的单元进行编程。

图8A示出了编程脉冲高电平宽度(t3-t2)长于临界时间(Tth-t2),使得在编程操作期间,在阈值时间Tth之后,浮置栅极FG和升压节点之间的电压差异变得大于电压增量阈值。时间Tth是当升压节点中的电压低到到达阈值电平时的“阈值时间”,其中阈值电平升压节点防止电子隧穿到浮置栅极FG中的最低电压。在经过时间Tth之后,自升压效应可能变得无效,并且在时间Tth之后能出现对未选择的存储器单元的不需要的编程。“电压增量阈值”表示浮置栅极FG和升压节点之间的用来禁止它们之间的电子隧穿的电压差异的最大大小。

根据本发明的一个实施例,图8B示出了编程脉冲高电平宽度(t3-t2)短于临界时间(Tth-t2),使得在整个编程操作期间,浮置栅极FG和升压节点之间的电压差异连续变得小于电压增量阈值。需要注意的是,图8A示出了在阈值时间Tth之后的时间t3,未选择的存储器单元(即,联接到未选择的存储器单元的控制栅极线CG1和CG2)上的电压电平开始下降的情况。相反,图8B示出了在建立的阈值时间Tth之前的时间t3,未选择的存储器单元上的电压电平开始下降的情况。

另一方面,当编程脉冲高电平宽度(t3-t2)变较短时,信号的上升和下降时间可能很长(significant)。由于所选择的单元(即,图2A和图2B中的单元A)在该开销时间(即,上升和下降时间)期间没有被编程,因此优选将这部分的该开销时间最小化。因此,只要编程禁止单元未达到阈值时间,就应最大化编程脉冲高电平宽度,以最小化那些上升和下降时间开销的部分。因此,根据本发明,控制栅极线CG1和CG2的到逻辑兼容闪存的控制栅极信号脉冲应维持到足够短(例如,小于10微秒),以便不到达能严重地出现不需要的编程操作的时刻(即,阈值时间),同时将脉冲高电平宽度维持得尽可能大,以使得能有效地分摊上升和下降时间开销。

图9示出了根据本发明的具有电压信号脉冲生成器和非易失性存储器单元阵列的框图。参照图2A和图2B和图3A至图3H中的闪存阵列,当接收输入信号(控制信号)时,电压信号脉冲生成器通过经由控制栅极线CG1/CG2、选择栅极线SG1/SG2和源极线SL发送一组控制信号来操作非易失性存储器单元阵列。在本发明的一个实施例中,电压信号生成器产生控制栅极线CG1和CG2的通过联接来上拉非易失性存储器单元的FG节点的目标编程电压,其中目标编程电压电平充分低(即,大约小于12V),使得在对阵列中的所选择的存储器单元进行编程的同时,阵列中的未选择的存储器单元的浮置栅极FG节点与升压节点之间的电压差异的大小小于电压增量阈值(即,大约6V)。结果是,对编程禁止单元,浮置栅极节点FG和升压节点之间的电压差异变得足够小,以防止未选择的存储器单元发生不需要的电子隧穿。此外,电压信号脉冲生成器还使控制栅极线CG1和CG2的控制栅极信号脉冲足够短,以不到达能严重发生不需要的编程操作的时刻(即阈值时间),同时脉冲高电平宽度被生成为尽可能大,以使得能有效地摊销上升和下降时间开销。

在一个实施例中,即使没有在图9中具体描述,电压信号脉冲生成器也可以包括关键子块(key subblock),诸如代码存储器、计时器、一次性可编程或只读存储器或者控制器电路。代码存储器被配置为存储非易失性存储器单元阵列的操作序列(例如,图4中所示的操作序列)。计时器电路能检查操作时序并且根据规定的时序(例如,图5中所示的编程操作的时序)调节关键信号脉冲。一次性可编程(OTP)或只读存储器能存储配置以选择上述控制栅极信号的适当电压电平(例如,HV、HV_A、HV_B、HV_C、VRD、VRD_A、VRD_B、VRD_C等)和时序信息(例如,图5中的t0至t7,图8A和图8B中的t1至t4等)。

能在每个芯片中预先确定或校准OTP存储器单元中存储的信息以用于在制造后的微调,然而只读存储中存储的信息是预先确定的,并且不能在制造之后被校准。控制器电路从代码存储器、计时器、OTP或只读存储器单元检索信息或者检索进入到电压信号脉冲生成器中的外部控制信号,并且基于这些信息调节电压信号脉冲生成器的信号输出。此外,电压信号脉冲生成器中的这样的关键子块的定义和使用对本领域技术人员而言是众所周知的,并且不应限于此处描述的特定描述或形式。

图10示出了根据本发明的具有各种组件的示例性芯片,组件诸如有中央处理单元(CPU)、易失性存储器和部署脉冲宽度控制编程方案的非易失性存储器。非易失性存储器单元能使用标准逻辑器件来制成,如图2A和图2B中所描绘的。因此,能使用标准逻辑工艺来成本效益高地构建整个芯片,而无需具有任何特定的制造工艺步骤,同时,根据本发明,能利用上述脉冲宽度控制编程方案准确而有效地将非易失性存储器单元编程到目标电平。

尽管在本公开中描述了具有五个逻辑器件(即,图2A和图2B中的单元A中的212、214、216、218、220;图2A和图2B中的单元B中的230、232、234、236、238、240)和五条行线(例如,图2A和图2B中的SG1、SG2、CG1、CG2、SL)的非易失性存储器单元,但本领域技术人员应能够将本发明应用于任何其它类型的逻辑兼容的非易失性存储器。因此,所提出的发明的定义和使用不应限于本公开中所示的逻辑兼容的非易失性存储器单元的具体描述或形式。尽管本发明易于进行各种修改和具有各替代形式,然而,应理解的是,本发明不限于所公开的特定形式。

- 非易失性存储器单元的编程方法及非易失性存储器设备

- 具有极性控制的每单元多比特(MBC)的非易失性存储器设备和系统及其编程方法