MOSFET器件版图的修整方法

文献发布时间:2023-06-19 11:17:41

技术领域

本发明涉及半导体制造技术领域,特别涉及一种MOSFET器件版图的修整方法。

背景技术

现有技术中,MOSFET器件(Metal-Oxide-Semiconductor Field-EffectTransistor,金属氧化物半导体场效应晶体管)版图(Layout)包含了MOSFET器件的尺寸,以及MOSFET器件中的各工艺层的相关物理信息数据,是MOSFET器件从设计走向制造的桥梁。如图1所示,图1是在现有技术的MOSFET器件的制造方法中形成的结构示意图。现有的MOSFET器件的制造方法通常包括:提供半导体衬底10,所述半导体衬底10包括有源区11和隔离区12,在所述有源区上形成浮栅13,所述浮栅13覆盖部分所述有源区11及部分所述隔离区12;然后,以所述浮栅13为掩膜,对所述有源区11执行倾斜离子注入,以形成轻掺杂漏区。但在以上步骤中,在以所述浮栅13为掩膜,对所述有源区11执行倾斜离子注入时,所述浮栅13会阻挡所述离子注入中的部分离子,部分离子由于被浮栅13遮挡使得在有源区中形成阴影区域14,该阴影区域14会引起漏电,并且会使得MOSFET器件的功耗较大。

因此,需要对MOSFET器件的制造方法中的工艺进行调整(调整器件的尺寸或者位置等),由此需要对MOSFET器件对应的MOSFET器件版图进行修整,以实现版图设计层面上的功耗优化。具体的,MOSFET器件对应的MOSFET器件版图的修整包括:修改MOSFET器件中的有源区11对应的有源区版图和/或浮栅13对应的浮栅版图等。在现有技术中,在对MOSFET器件版图进行修整时,会修改MOSFET器件版图的全部布局(版图中的图形排布、尺寸和形状)等,即需要对MOSFET器件版图进行大量的修改,一方面对应的工作量非常大,另一方面,修改MOSFET器件版图的全部布局后,可能会增加MOSFET器件版图中的图形尺寸,从而会影响形成的MOSFET器件的尺寸,因此,需要一种新的MOSFET器件版图的修整方法,以简单及快速的完成版图的修改,并实现版图设计层面上的功耗优化。

发明内容

本发明的目的在于提供一种MOSFET器件版图的修整方法,以简单及快速的完成版图的修改,并实现版图设计层面上的功耗优化。

为实现上述目的,本发明提供一种MOSFET器件版图的修整方法,包括:

获取原始版图,所述原始版图包括有源区版图和浮栅版图,所述有源区版图包括至少一个有源区图形,所述浮栅版图包括至少一个浮栅图形,每个所述浮栅图形均包括一第一浮栅子图形,所述第一浮栅子图形与所述有源区图形平行,并且所述第一浮栅子图形与所述有源区图形之间存在间距;

修改所述原始版图的设计规则;

根据修改后的所述原始版图的设计规则修改所述浮栅版图,减小所述浮栅版图中的所有浮栅图形的尺寸,以增大所述第一浮栅子图形与所述有源区图形之间的间距;以及

根据修改后的所述原始版图的设计规则检查修改后的所述浮栅版图中的所有浮栅图形。

可选的,在所述的MOSFET器件版图的修整方法中,所述浮栅图形还包括第二浮栅子图形,所述第二浮栅子图形与所述第一浮栅子图形的部分重叠并连接为一体,并且所述第二浮栅子图形覆盖部分所述有源区图形。

可选的,在所述的MOSFET器件版图的修整方法中,所述第一浮栅子图形和所述第二浮栅子图形均呈一矩形,所述第一浮栅子图形沿第一方向延伸,所述第二浮栅子图形沿第二方向延伸,所述第一方向与所述第二方向垂直。

可选的,在所述的MOSFET器件版图的修整方法中,修改所述原始版图的设计规则的方法包括:

获取所述原始版图的设计规则;

根据所述原始版图对应的制造工艺,确定所述原始版图的设计规则中可牺牲的设计规则,并根据所述可牺牲的设计规则修改所述原始版图的设计规则。

可选的,在所述的MOSFET器件版图的修整方法中,获取的所述原始版图的设计规则包括:

所述有源区版图的设计规则、所述浮栅版图的设计规则及所述有源区版图与所述浮栅版图之间的间距的设计规则;其中,所述有源区版图的设计规则包括所述有源区图形的最小尺寸,所述浮栅版图的设计规则包括所述浮栅图形的最小尺寸,所述浮栅版图与所述有源区版图之间的间距的设计规则包括所述第一浮栅子图形与所述有源区图形之间的最小间距尺寸。

可选的,在所述的MOSFET器件版图的修整方法中,所述可牺牲的设计规则包括:减小所述有源区版图的设计规则中的所述浮栅图形的最小尺寸、减小所述浮栅版图中的所述浮栅图形的最小尺寸,以及减小所述浮栅版图与所述有源区版图之间的间距的设计规则中的所述第一浮栅子图形与所述有源区图形之间的最小间距尺寸。

可选的,在所述的MOSFET器件版图的修整方法中,根据修改后的所述原始版图的设计规则修改所述浮栅版图的方法包括:

通过版图逻辑运算筛选出所述浮栅版图中的所有浮栅图形;

根据修改后的所述原始版图的设计规则修改所有的所述浮栅图形的尺寸及形状;

其中,所述浮栅图形的尺寸及形状的修改方法包括:

形成一修整图形,所述修整图形呈一矩形,并且所述修整图形的尺寸小于所述第一浮栅子图形的尺寸;

使所述修整图形对准所述第一浮栅子图形,以使所述第一浮栅子图形的部分与所述修整图形重叠;

去除所述第一浮栅子图形中与所述修整图形重叠的部分;

去除所述修整图形。

可选的,在所述的MOSFET器件版图的修整方法中,修改后的所述浮栅图形的第一浮栅子图形中具有一凹口,所述凹口朝向所述有源区图形。

可选的,在所述的MOSFET器件版图的修整方法中,使所述第一浮栅子图形与所述浮栅图形的部分重叠的方法包括:使所述修整图形中沿第一方向平行的一边与所述第一浮栅子图形中靠近所述有源区且沿所述第一方向平行的一边的至少一段边对齐,以及使所述修整图形中沿所述第二方向平行的一边与所述第二浮栅子图形中沿所述第二方向平行的一边连接。

可选的,在所述的MOSFET器件版图的修整方法中,所述浮栅图形呈L型、T型或十字型。

发明人研究发现,现有的MOSFET器件的有源区中存在阴影区域的原因是,MOSFET器件的原始版图中的有源区图形与第一浮栅子图形之间的间距较小,由此导致在有源区版图与浮栅版图对应的制造工艺中,第一浮栅子图形对应的浮栅与有源区之间的间距较小,从而在现有的MOSFET器件的制造方法中,对有源区执行倾斜离子注入时,会导致浮栅(第一浮栅子图形对应的浮栅)阻挡的离子注入中的离子较多,并会导致有源区中形成阴影区域。基于此,在本发明提供的MOSFET器件版图的修整方法中,通过修改原始版图的设计规则;然后,通过修改后的所述原始版图的设计规则修改浮栅版图,减小所述浮栅版图中的所有浮栅图形的尺寸,以增大所述第一浮栅子图形与所述有源区图形之间的间距;如此,可以简单及快速的完成原始版图的修改,并实现版图设计层面上的功耗优化。

附图说明

图1是现有技术中的MOSFET器件的制造方法中形成的结构示意图;

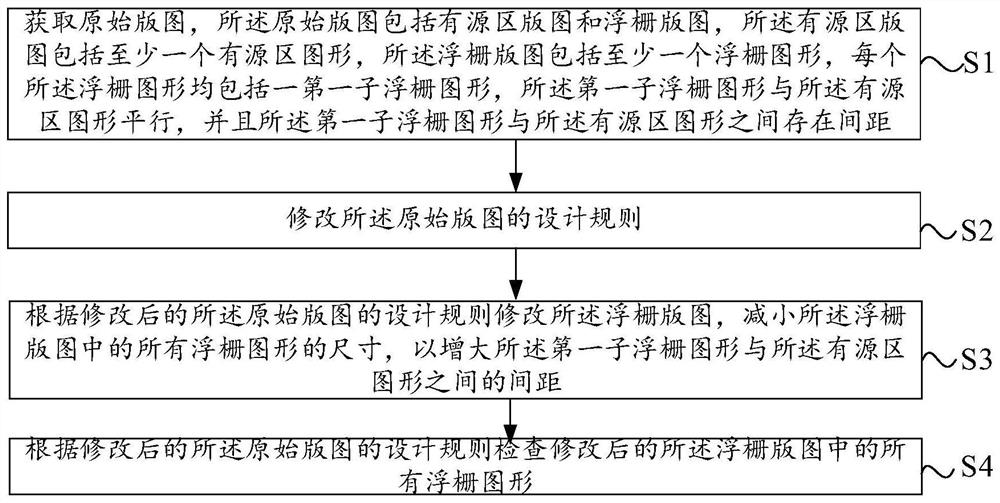

图2是本发明实施例提供的MOSFET器件版图的修整方法的流程示意图;

图3~图7是本发明实施例提供的MOSFET器件版图的修整方法中形成的版图结构示意图;

其中,附图标记说明如下:

10-半导体衬底;11-有源区;12-隔离区;13-浮栅;14-阴影区域;

100-原始版图;110-有源区图形;120-浮栅图形;121-第一浮栅子图形;122-第二浮栅子图形;130-修整图形。

具体实施方式

以下结合附图和具体实施例对本发明提出的MOSFET器件版图的修整方法作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

发明人研究发现,现有的MOSFET器件的有源区中存在阴影区域的原因是,MOSFET器件的原始版图中的有源区图形与第一浮栅子图形之间的间距较小,由此导致在有源区版图与浮栅版图对应的制造工艺中,第一浮栅子图形对应的浮栅与有源区之间的间距较小,由此,在现有的MOSFET器件的制造方法中,对有源区执行倾斜离子注入时,会导致浮栅(第一浮栅子图形对应的浮栅)阻挡的离子注入中的离子较多,并会导致有源区中形成阴影区域。基于此,在本发明提供的MOSFET器件版图的修整方法中,通过修改原始版图的设计规则;然后,通过修改后的所述原始版图的设计规则修改浮栅版图,减小所述浮栅版图中的所有浮栅图形的尺寸,以增大所述第一浮栅子图形与所述有源区图形之间的间距;如此,可以简单及快速的完成原始版图的修改,并实现版图设计层面上的功耗优化。

请参考图2,其为本发明实施例提供的MOSFET器件版图的修整方法的流程示意图。如图2所示,本发明提供一种MOSFET器件版图的修整方法,所述MOSFET器件版图的修整方法包括:

步骤S1:获取原始版图,所述原始版图包括有源区版图和浮栅版图,所述有源区版图包括至少一个有源区图形,所述浮栅版图包括至少一个浮栅图形,每个所述浮栅图形均包括一第一浮栅子图形,所述第一浮栅子图形与所述有源区图形平行,并且所述第一浮栅子图形与所述有源区图形之间存在间距;

步骤S2:修改所述原始版图的设计规则;

步骤S3:根据修改后的所述原始版图的设计规则修改所述浮栅版图,减小所述浮栅版图中的所有浮栅图形的尺寸,以增大所述第一浮栅子图形与所述有源区图形之间的间距;以及

步骤S4:根据修改后的所述原始版图的设计规则检查修改后的所述浮栅版图中的所有浮栅图形。

接下去,将结合附图3~7对以上步骤进行更详细的说明;其中,图3~7为本发明实施例提供的MOSFET器件版图的修整方法中形成的版图结构示意图。

首先,执行步骤S1,参考图3,获取原始版图100,所述原始版图100包括有源区版图和浮栅版图,所述有源区版图包括至少一个有源区图形110,每个所述浮栅版图均包括至少一个浮栅图形120,所述浮栅图形120包括一第一浮栅子图形121,所述第一浮栅子图形121与所述有源区图形110平行,并且所述第一浮栅子图形121与所述有源区图形110之间存在间距d

进一步的,所述浮栅图形120还包括第二浮栅子图形122,所述第二浮栅子图形122与所述第一浮栅子图形121的部分重叠并连接为一体,并且所述第二浮栅子图形122覆盖部分所述有源区图形110。所述第一浮栅子图形121与所述第二浮栅子图形122呈一矩形,所述第一浮栅子图形121沿第一方向X延伸,所述第二浮栅子图形122沿第二方向Y延伸,所述第一方向X与所述第二方向Y垂直。

所述浮栅图形120呈L型。此外,如图4和图5所示,在本发明提供的其他实施例中,所述浮栅图形120也可以呈T型或十字型。

接着,执行步骤S2,修改所述原始版图100的设计规则。具体的,修改所述原始版图100的设计规则的方法包括:

步骤S21:获取所述原始版图100的设计规则,获取的所述原始版图100的设计规则包括:所述有源区版图的设计规则、所述浮栅版图的设计规则,以及所述浮栅版图与所述有源区版图之间的间距的设计规则。进一步的,有源区版图的设计规则包括所述有源区图形110的最小尺寸,所述浮栅版图的设计规则包括所述浮栅图形120的最小尺寸,所述浮栅版图与有源区版图之间的间距的设计规则包括所述第一浮栅子图形121与所述有源区图形110之间的最小间距尺寸。

步骤S22:根据所述原始版图100对应的制造工艺,确定所述原始版图100的设计规则中可牺牲的设计规则,并根据所述可牺牲的设计规则修改所述原始版图100的设计规则。其中,所述原始版图100对应的制造工艺为所述原始版图100所对应的MOSFET器件的制造工艺。

根据所述原始版图100对应的制造工艺,确定所述原始版图100的设计规则中可牺牲的设计规则的具体方法包括:根据所述原始版图100对应的制造工艺,确定所述制造工艺形成的有源区的尺寸与所述原始版图100中的有源区图形110的尺寸之间的误差,以及确定所述制造工艺形成的和浮栅的尺寸与所述原始版图100中的浮栅图形120的尺寸之间的误差,或者说制造工艺的精度,根据该误差或者制造工艺精度,可以评估所述原始版图100的设计规则中可牺牲的设计规则。

更具体的,所述可牺牲的设计规则包括:减小所述有源区版图的设计规则中的所述有源区图形110的最小尺寸、减小所述浮栅版图的设计规则中的所述浮栅图形120的最小尺寸,以及减小所述浮栅版图与所述有源区版图之间的设计规则中的所述第一浮栅子图形121与所述有源区图形之间的最小间距尺寸中的至少一个。

接着,执行步骤S3:参考图6,根据修改后的所述原始版图100的设计规则修改所述浮栅版图,减小所述浮栅版图中的所有浮栅图形120的尺寸,以增大所述第一浮栅子图形121与所述有源区图形110之间的间距。

具体的,根据修改后的所述原始版图100的设计规则修改所述浮栅版图的方法包括:

步骤S31:通过版图逻辑运算筛选出所述浮栅版图中所有的浮栅图形120;

步骤S32:根据修改后的所述原始版图100的设计规则修改所有的所述浮栅图形120的尺寸及形状。

其中,所述浮栅图形120的尺寸及形状的修改方法包括:如图6所示,首先,形成一修整图形130,所述修整图形130呈一矩形,并且所述修整图形130的尺寸小于所述第一浮栅子图形121的尺寸;所述修整图形130的尺寸可以根据,所述浮栅版图的设计规则中的所述浮栅图形120的最小尺寸与修改后的所述浮栅版图的设计规则中的所述浮栅图形120的最小尺寸之间的尺寸差得到。

然后,使所述修整图形130对准所述第一浮栅子图形121,以使所述第一浮栅子图形121的部分与所述修整图形130重叠。

具体的,使所述第一浮栅子图形121的部分与所述修整图形130重叠的方法包括:使所述修整图形130中沿第一方向X平行的一边与所述第一浮栅子图形121中靠近所述有源区且沿所述第一方向X平行的一边的至少一段边对齐,以及使所述修整图形130中沿所述第二方向Y平行的一边与所述第二浮栅子图形122中沿所述第二方向Y平行的一边连接。

接着,如图7所示,去除所述第一浮栅子图形121中与所述修整图形130重叠的部分。进一步的,使所述第一浮栅子图形121的部分与所述修整图形130重叠的目的是,所述第一浮栅子图形121的部分与所述修整图形130的重叠的区域靠近沟道区(第二浮栅子图形122覆盖部分有源区图形110的区域),而在MOSEFET的制造工艺中阴影区域通常出现在靠近沟道区的有源区中,因此将所述第一浮栅子图形121的部分与所述修整图形130的重叠的区域设在靠近沟道区的附近,如此,在后续去除所述第一浮栅子图形121中与所述修整图形130重叠的部分后,可以增加所述第一浮栅子图形121与所述有源区图形110之间的间距,从而在MOSEFET的制造工艺中,可以增加浮栅(第一浮栅子图形对应的浮栅)与有源区之间的距离,由此可以避免浮栅对离子注入的阻挡,从而可以避免有源区中出现阴影区域。

进一步的,修改后的所述浮栅图形120的所述第一浮栅子图形121与所述有源区图形110之间存在间距d

进一步的,修改后的所述浮栅图形120的第一浮栅子图形121具有一凹口140,所述凹口140朝向所述有源区图形110,即去除所述浮栅图形120中与所述第一浮栅子图形121重叠的部分,会改变所述浮栅图形120的形状,从而使得所述第一浮栅子图形121具有一凹口140,该凹口140的存在,可以增加所述第一浮栅子图形121与所述有源区图形110之间的间距,可以实现版图设计层面上的功耗优化,并且在有源区版图与浮栅版图对应的制造工艺中,可以避免有源区与浮栅之间出现阴影区域。接着,去除所述修整图形130。

此外,所述浮栅版图的修改可通过自动化程序或者软件实现,即上述步骤可以作为标准化步骤而通过自动化程序或者软件实现。如此,可以节省人力,进一步的,通过获取原始版图,并修改所述原始版图的设计规则,以及根据修改后的所述原始版图的设计规则修改所述浮栅版图,减小所述浮栅版图中的所有浮栅图形的尺寸,以增大所述第一浮栅子图形与所述有源区图形之间的间距。由此,通过在原始版图的基础上对浮栅版图进行修改,无需要重新设计版图,从而可以避免增加MOSFET器件版图的总体面积。

接着,执行步骤S4,根据修改后的所述原始版图100的设计规则检查修改后的所述浮栅版图中的所有浮栅图形120。具体的,在完成原始版图100的修改以后,需要根据修改后的原始版图100的设计规则,对修改后的浮栅版图中的所有浮栅图形120进行检查,即设计规则检查(Design Rule Check,DRC),以确保修改后的所述浮栅版图中的所有浮栅图形120满足修改后的原始版图100的设计规则,即检查修改后的所有所述浮栅图形120的尺寸是否符合修改后的设计规则中的所述浮栅图形120的最小尺寸,也就是说检查修改后的所有所述浮栅图形120的尺寸是否至少为修改后的设计规则中的所述浮栅图形120的最小尺寸。

综上可见,在本发明提供的MOSFET器件版图的修整方法中,通过修改原始版图的设计规则;然后,通过修改后的所述原始版图的设计规则修改浮栅版图,减小所述浮栅版图中的所有浮栅图形的尺寸,以增大所述第一浮栅子图形与所述有源区图形之间的间距;如此,可以简单及快速的完成版图的修改,并实现版图设计层面上的功耗优化。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

- MOSFET器件版图的修整方法

- 一种双面版图设计方法、双面版图及双面版图切割方法