开关芯片

文献发布时间:2023-06-19 11:17:41

技术领域

本发明涉及一种多工器与解多工器,特别是一种利用互补式金属氧化物半导体工艺(CMOS)以及封装的导线(bond wire)取代晶粒(die)的走线的双向被动N:M多工器以及M:N解多工器,其应用于高速信号的数据流传输(其中N大于M)。

背景技术

尽管处理器经常以并行方式处理数据,但是数据在点与点之间却是以串行的方式进行通信。在通信电路的发送端中,经常使用串行电路(serializer circuit)对并行的数据串行化,而在接收端则较常使用解串行电路(deserializer circuit)将串行的数据并行化。双向通信的电路中往往使用执行串行化以及并行化的设备,该设备称之为串行器(serializer)以及解串行器(deserializer),或更常称之为SerDes。

在一些应用中,数据能以不同的传输速率(data rate)从一个点传输至另一个点,或从一个点传输到任意数量的其他点。当以不同的传输速率发送数据时,在通信电路中使用的SerDes设备以相应的不同频率工作。

发明内容

本发明在此提出了开关芯片(多工器/解多工器),并且利用封装的导线(bondwire)取代晶粒中的金属走线,使得晶粒中各个元件之间的电感值能够更精确的控制,也增加设计上的弹性。此外,由于导线的阻抗值较小,因此降低了传导损耗,再加上导线没有晶粒中的金属走线的介电损耗。此外,在晶粒中不同元件之间利用导线进行耦接,有助于拓展开关芯片的操作带宽,使得开关芯片达到宽操作频带、低插入损耗、低回波损耗且高隔离的目的。

有鉴于此,本发明提出一种开关芯片。开关芯片包括一第一开关元件、一第一静电放电保护装置以及一第二静电放电保护装置。上述第一开关元件电性耦接在一第一接垫以及一第二接垫之间。上述第一静电放电保护装置电性耦接至一第三接垫,其中上述第三接垫通过一第一导线电性耦接至上述第一接垫。上述第二静电放电保护装置,电性耦接至一第四接垫,其中上述第四接垫通过一第二导线电性耦接至上述第二接垫。

本发明更提出一种开关芯片,开关芯片包括一第一开关元件、一第二开关元件、一第一静电放电保护装置、一第二静电放电保护装置以及一第三静电放电保护装置。上述第一开关元件电性耦接在一第一接垫以及一第二接垫之间。上述第二开关元件电性耦接在上述第一接垫以及一第三接垫之间。上述第一静电放电保护装置电性耦接至一第四接垫,其中上述第四接垫通过一第一导线电性耦接至上述第一接垫。上述第二静电放电保护装置电性耦接至一第五接垫,其中上述第五接垫通过一第二导线电性耦接至上述第二接垫。上述第三静电放电保护装置电性耦接至一第六接垫,其中上述第六接垫通过一第三导线电性耦接至上述第三接垫。

本发明更提出一种开关芯片,开关芯片包括一第一开关元件、一第二开关元件、一第三开关元件、一第四开关元件、一第五开关元件、一第六开关元件、一第一静电放电保护装置、一第二静电放电保护装置、一第三静电放电保护装置、一第四静电放电保护装置以及一第五静电放电保护装置。上述第一开关元件电性耦接在一第一接垫以及一第二接垫之间。上述第二开关元件电性耦接在上述第二接垫以及一第三接垫之间。上述第三开关元件电性耦接在一第四接垫以及一第五接垫之间。上述第四开关元件电性耦接在上述第五接垫以及一第六接垫之间。上述第五开关元件电性耦接在一第七接垫以及一第八接垫之间。上述第六开关元件电性耦接在上述第八接垫以及一第九接垫之间。上述第一静电放电保护装置电性耦接至一第十接垫,其中上述第十接垫通过一第一导线电性耦接至上述第一接垫、通过一第二导线电性耦接至上述第四接垫且通过一第三导线电性耦接至上述第七接垫。上述第二静电放电保护装置电性耦接至一第十一接垫,其中上述第十一接垫通过一第四导线电性耦接至上述第三接垫、通过一第五导线电性耦接至上述第六接垫且通过一第六导线电性耦接至上述第九接垫。上述第三静电放电保护装置电性耦接至一第十二接垫,其中上述第十二接垫通过一第七导线电性耦接至上述第二接垫。上述第四静电放电保护装置电性耦接至一第十三接垫,其中上述第十三接垫通过一第八导线电性耦接至上述第五接垫。上述第五静电放电保护装置电性耦接至一第十四接垫,其中上述第十四接垫通过一第九导线电性耦接至上述第八接垫。

本发明更提出一种开关芯片,上述开关芯片包括一第一引脚、一第二引脚以及一晶粒。上述第一引脚通过一第一导线电性耦接至一第一接垫。上述第二引脚通过一第二导线电性耦接至第二接垫。上述晶粒包括一第一开关元件,上述第一开关元件的一端通过一第三导线耦接至上述第一接垫,上述第一开关元件的另一端通过一第四导线耦接至上述第二接垫。

本发明更提出一种开关芯片,上述开关芯片包括一第一引脚、一第二引脚、一第三引脚以及一晶粒。上述第一引脚通过一第一导线电性耦接至一第一接垫。上述第二引脚通过一第二导线电性耦接至一第二接垫。上述第三引脚通过一第三导线电性耦接至一第三接垫。上述晶粒包括一第一开关元件以及一第二开关元件。上述第一开关元件的一端通过一第四导线电性耦接在上述第二接垫,上述第二开关元件的一端通过一第五导线电性耦接在上述第三接垫,上述第一开关元件的另一端以及上述第二开关元件的另一端共同通过一第六导线电性耦接在上述第一接垫。

本发明更提出一种开关芯片,上述开关芯片包括一第一引脚、一第二引脚、一第三引脚、一第四引脚、一第五引脚以及一晶粒。上述第一引脚通过一第一导线电性耦接至一第一接垫。上述第二引脚通过一第二导线电性耦接至一第二接垫。上述第三引脚通过一第三导线电性耦接至一第三接垫。上述第四引脚通过一第四导线电性耦接至一第四接垫。上述第五引脚通过一第五导线电性耦接至一第五接垫。上述晶粒包括一第一开关元件、一第二开关元件、一第三开关元件、一第四开关元件、一第五开关元件以及一第六开关元件。上述第一开关元件的一端通过一第六导线电性耦接至上述第一接垫。上述第二开关元件一端分别通过一第七导线电性耦接在上述第二接垫,上述第一开关元件的另一端以及上述第二开关元件的另一端共同通过一第八导线电性耦接在上述第三接垫。上述第三开关元件的一端通过一第九导线电性耦接至上述第一接垫。上述第四开关元件一端通过一第十导线电性耦接在上述第二接垫,上述第三开关元件的另一端以及上述第四开关元件的另一端共同通过一第十一导线电性耦接在上述第四接垫。上述第五开关元件的一端通过一第十二导线电性耦接至上述第一接垫。上述第六开关元件的一端通过一第十三导线的方式电性耦接在上述第二接垫,上述第五开关元件的另一端以及上述第六开关元件的另一端共同通过一第十四导线的方式电性耦接在上述第五接垫。

附图说明

图1是显示根据一实施例所述的开关芯片的示意图;

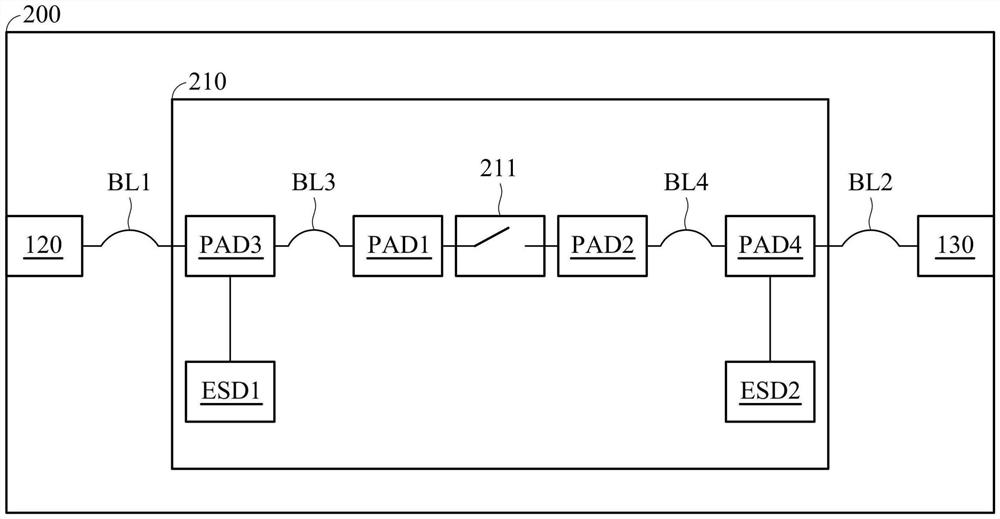

图2是显示根据本发明的一实施例所述的开关芯片的示意图;

图3是显示根据本发明的一实施例所述的开关芯片的等效电路图;

图4是显示根据本发明的另一实施例所述的由多个开关元件所构成的1:2解多工器或是2:1多工器的示意图;以及

图5是显示根据本发明的另一实施例所述的由多个开关元件所构成的2:3解多工器或是3:2多工器的示意图。

【符号说明】

100、200、400、500:开关芯片

110、210、410、510:晶粒

120、420、520:第一引脚

130、430、530:第二引脚

111、211、411、511:第一开关元件

300:等效电路

412、512:第二开关元件

513:第三开关元件

514:第四开关元件

515:第五开关元件

516:第六开关元件

440、540:第三引脚

550:第四引脚

560:第五引脚

ESD1:第一静电放电保护装置

ESD2:第二静电放电保护装置

ESD3:第三静电放电保护装置

PAD1:第一接垫

PAD2:第二接垫

PAD3:第三接垫

PAD4:第四接垫

PAD5:第五接垫

PAD6:第六接垫

PAD7:第七接垫

PAD8:第八接垫

PAD9:第九接垫

PAD10:第十接垫

PAD11:第十一接垫

PAD12:第十二接垫

PAD13:第十三接垫

PAD14:第十四接垫

BL1:第一导线

BL2:第二导线

BL3:第三导线

BL4:第四导线

BL5:第五导线

BL6:第六导线

BL7:第七导线

BL8:第八导线

BL9:第九导线

BL10:第十导线

BL11:第十一导线

BL12:第十二导线

BL13:第十三导线

PAD14:第十四导线

TR1:第一走线

TR2:第二走线

TR3:第三走线

TR4:第四走线

LBL1:第一导线电感

LBL2:第二导线电感

LBL3:第三导线电感

LBL4:第四导线电感

CESD1:第一静电放电保护装置电容

CESD2:第二静电放电保护装置电容

SW:理想开关

C1:第一(寄生)电容

C2:第二(寄生)电容

CPCB1:第一电路板电容

CPCB2:第二电路板电容

S1:第一信号

S2:第二信号

S3:第三信号

S4:第四信号

S5:第五信号

具体实施方式

以下说明为本发明的实施例。其目的是要举例说明本发明一般性的原则,不应视为本发明的限制,本发明的范围当以权利要求书所界定者为准。

能理解的是,虽然在此可使用用语“第一”、“第二”、“第三”等来叙述各种元件、组成成分、区域、层、和/或部分,这些元件、组成成分、区域、层、和/或部分不应被这些用语限定,且这些用语仅是用来区别不同的元件、组成成分、区域、层、和/或部分。因此,以下讨论的一第一元件、组成成分、区域、层、和/或部分可在不偏离本公开一些实施例的教示的情况下被称为一第二元件、组成成分、区域、层、和/或部分。

值得注意的是,以下所公开的内容可提供多个用以实践本发明的不同特点的实施例或范例。以下所述的特殊的元件范例与安排仅用以简单扼要地阐述本发明的精神,并非用以限定本发明的范围。此外,以下说明书可能在多个范例中重复使用相同的元件符号或文字。然而,重复使用的目的仅为了提供简化并清楚的说明,并非用以限定多个以下所讨论的实施例和/或配置之间的关系。此外,以下说明书所述的一个特征连接至、耦接至和/或形成于另一特征之上等的描述,实际可包含多个不同的实施例,包括该等特征直接接触,或者包含其它额外的特征形成于该等特征之间等等,使得该等特征并非直接接触。

多工器(MUX)以及解多工器(DEMUX)是高速信号规格中(如USB、SATA、PCIe等)常使用的元件,其用以改变所连接的高速数据流的传送/接收路径及方向。一般来说,多工器以及解多工器的相关电路包含了ESD保护电路、晶体管(MOSFET)、栅极控制信号以及连接晶体管与数据流输入端与输出端的金属线。本发明中的N:M多工器以及M:N解多工器适用于高速数据流的传输(如1Gbps或更高),其中N大于M。一般而言,ESD保护电路以及晶体管所产生的寄生电容(Parasitics)如果不被吸收将增加数据流通过多工器以及解多工器的信号损耗,而影响数据流的信号完整性(signal integrity),进而降低多工器以及解多工器可使用数据流的传输速度。为了降低这些寄生电容对于多工器以及解多工器所产生的不良影响,常用方式便是利用晶圆厂所提供的工艺上的厚金属层来实现电感以将这些寄生电容吸收,进而降低这些寄生电容所造成的影响。另一种方式是利用互补式金属氧化物半导体-硅晶绝缘体(CMOS SOI)工艺。上述两种做法虽可达到降低寄生电容对于多工器以及解多工器所产生的不良影响,却也增加了产品的成本。

由于多工器与解多工器中是由至少一个开关元件所构成,以下先以一开关元件来进行说明。图1是显示根据一实施例所述的开关芯片的示意图。如图1所示,在一实施例中,开关芯片100为具有一导线架(lead frame)的封装芯片,其中开关芯片100包括晶粒(die)110、第一引脚120以及第二引脚130。晶粒110包括第一开关元件111、第一静电放电保护装置ESD1以及第二静电放电保护装置ESD2、第一接垫PAD1、第二接垫PAD2。

第一开关元件111通过第一走线TR1而耦接至第一接垫PAD1,并且通过第二走线TR2而耦接至第二接垫PAD2。第一静电放电保护装置ESD1电性耦接至第一接垫PAD1,第二静电放电保护装置ESD2电性耦接至第二接垫PAD2。根据本发明的一实施例,第一走线TR1以及第二走线TR2为晶粒110中的金属走线。根据本发明的一实施例,第三走线TR3以及第四走线TR4为晶粒110中的金属走线。第一静电放电保护装置ESD1通过第三走线TR3耦接至第一接垫PAD1,第二静电放电保护装置ESD2通过第四走线TR4耦接至第二接垫PAD2。第一静电放电保护装置ESD1以及第二静电放电保护装置ESD2用以保护第一开关元件111,免于第一接垫PAD1以及第二接垫PAD2所接收到的静电放电。

第一静电放电保护装置ESD1至第一接垫PAD1以及第二静电放电保护装置ESD2至第二接垫PAD2之间的距离极短,因此在此忽略第一静电放电保护装置ESD1至第一接垫PAD1以及第二静电放电保护装置ESD2至第二接垫PAD2之间的走线TR3、TR4所产生的效应,以简化说明。

如图1所示,晶粒110的第一接垫PAD1通过第一导线BL1电性耦接至第一引脚120,晶粒110的第二接垫PAD2通过第二导线BL2电性耦接至第二引脚130,使得晶粒110得以通过第一引脚120以及第二引脚130而电性耦接至其他外部电路。

为了使开关芯片100能够适用于宽频带(wide bandwidth)并达成低插入损耗(lowinsertion loss)、低回波损耗(low return loss)以及高隔离(high isolation)的应用目的,由于开关芯片100属于被动元件,因此如何减少第一走线TR1以及第二走线TR2的介电损耗(dielectric loss)以及传导损耗(conduction loss)将成为设计的关键。

此外,由于晶粒110的制造过程中蚀刻工艺的精准度难以掌握,使得第一走线TR1以及第二走线TR2的走线宽度与长度经常发生飘移的现象,进而影响阻抗匹配而造成信号耗损。

本发明在此提出一种利用封装(packaging)的导线(bondwires)取代晶粒(die)中的走线(metal traces)做为开关元件两端与数据流的输入端与输出端的连接。在一实施例中,开关元件可为晶体管,则在晶体管的漏极(Drain)与源极(Source)的上的走线将以封装(packaging)的导线(bondwires)取代。因为利用导线做为电感可将先前所提到的寄生电容吸收的更好,并且导线相较于工艺所用的金属走线有较高的Q值,因而降低了数据流的传导损耗,同时也保持了在高速传输下信号的完整性,进而达到宽频带、低损耗、低回波损耗的设计。

由于多工器与解多工器中是由至少一个开关元件所构成,以下先以一开关元件来说明本发明。图2是显示根据本发明的一实施例所述的开关芯片的示意图。如图2所示,在一实施例中,开关芯片200为具有一导线架(lead frame)的封装芯片,其中开关芯片200包括晶粒210、第一引脚120以及第二引脚130。晶粒210包括第一开关元件211、第一静电放电保护装置ESD1、第二静电放电保护装置ESD2、第一接垫PAD1、第二接垫PAD2、第三接垫PAD3、第四接垫PAD4、第三导线BL3以及第四导线BL4。

如图2所示,第一开关元件211电性耦接在第一接垫PAD1以及第二接垫PAD2之间,第一静电放电保护装置ESD1电性耦接至第三接垫PAD3,第二静电放电保护装置ESD2电性耦接至第四接垫PAD4。此外,第一接垫PAD1通过第三导线BL3电性耦接至第三接垫PAD3,第二接垫PAD2通过第四导线BL4电性耦接至第四接垫PAD4。

根据本发明的一实施例,第一开关元件211与第一接垫PAD1以及第二接垫PAD2之间的距离极短,故可忽略其间的走线所产生的效应。根据本发明的一实施例,第一静电放电保护装置ESD1至第三接垫PAD3以及第二静电放电保护装置ESD2至第四接垫PAD4之间的距离极短,因此在此忽略第一静电放电保护装置ESD1至第三接垫PAD3以及第二静电放电保护装置ESD2至第四接垫PAD4之间的走线所产生的效应。根据本发明的许多实施例,第一开关元件211为N型晶体管,或是P型晶体管。根据本发明的其他实施例,第一开关元件211可为其他可作为开关的电子元件。

将图2的晶粒210与图1的晶粒110相比,图1的第一走线TR1以第三导线BL3取代,图1的第二走线TR2以第四导线BL4取代。根据本发明的一实施例,第三导线BL3以及第四导线BL4为封装中用以连接接垫以及导线架的金属导线,而第一导线BL1、第二导线BL2也是金属导线,其用以连接晶粒中的接垫与接垫之间。

图3是显示根据本发明的一实施例所述的开关芯片的等效电路图。如图3所示,等效电路300为开关芯片200的等效电路。第一导线电感LBL1、第二导线电感LBL2、第三导线电感LBL3以及第四导线电感LBL4分别为第一导线BL1、第二导线BL2、第三导线BL3以及第四导线BL4的等效电感,第一静电放电保护装置电容CESD1以及第二静电放电保护装置电容CESD2分别为第一静电放电保护装置ESD1以及第二静电放电保护装置ESD2所产生的寄生电容。

第一开关元件211等效为理想开关SW、第一(寄生)电容C1以及第二(寄生)电容C2,第一引脚120所耦接的外部电路板的寄生电容可等效为第一电路板电容CPCB1,第二引脚130所耦接的外部电路板的寄生电容可等效为第二电路板电容CPCB2。

根据本发明的一实施例,如图3所示,开关芯片200可等效为LC阶梯式(LC-ladder)滤波器,并利用设计LC阶梯式滤波器的方式,扩展开关芯片200的操作带宽。此外,由于导线的电感值与其长度有关,相较于因蚀刻工艺的限制而难以掌握晶粒的内部走线的宽度以及长度,导线的电感值更容易精准控制。并且,导线具有低阻抗的特性,利用导线取代晶粒的内部走线有助于降低信号的损耗。因此,使用导线替代晶粒的内部走线,有助于开关芯片200更容易达成宽频带、低插入损耗、低回波损耗且高隔离的应用目的。

图4是显示根据本发明的另一实施例所述的由多个开关元件所构成的1:2解多工器或是2:1多工器的示意图。如图4所示,在一实施例中,开关芯片400为具有一导线架(leadframe)的封装芯片,其中开关芯片400包括晶粒410、第一引脚420、第二引脚430以及第三引脚440。

晶粒410包括第一开关元件411、第二开关元件412、第一静电放电保护装置ESD1、第二静电放电保护装置ESD2、第三静电放电保护装置ESD3、第一接垫PAD1、第二接垫PAD2、第三接垫PAD3、第四接垫PAD4、第五接垫PAD5以及第六接垫PAD6。

第一开关元件411电性耦接在第一接垫PAD1以及第二接垫PAD2之间,第二开关元件412电性耦接在第一接垫PAD1以及第三接垫PAD3之间。根据本发明的一实施例,第一开关元件411以及第二开关元件412分别至第一接垫PAD1、第二接垫PAD2以及第三接垫PAD3之间的距离极短,故可忽略其间的走线所产生的效应。第四接垫PAD4通过第一导线BL1而电性耦接至第一引脚420,第五接垫PAD5通过第二导线BL2而电性耦接至第二引脚430,第六接垫PAD6通过第三导线BL3而电性耦接至第三引脚440。

第一静电放电保护装置ESD1电性耦接至第四接垫PAD4,第二静电放电保护装置ESD2电性耦接至第五接垫PAD5,第三静电放电保护装置ESD3电性耦接至第六接垫PAD6。根据本发明的一实施例,由于第一静电放电保护装置ESD1至第四接垫PAD4、第二静电放电保护装置ESD2至第五接垫PAD5以及第三静电放电保护装置ESD3至第六接垫PAD6之间的距离极短,因此在此忽略第一静电放电保护装置ESD1至第四接垫PAD4、第二静电放电保护装置ESD2至第五接垫PAD5以及第三静电放电保护装置ESD3至第六接垫PAD6之间的走线所产生的效应。

第一接垫PAD1通过第四导线BL4而电性耦接至第四接垫PAD4,第二接垫PAD2通过第五导线BL5而电性耦接至第五接垫PAD5,第三接垫PAD3通过第六导线BL6而电性耦接至第六接垫PAD6。

根据本发明的一实施例,第一引脚420接收到第一信号S1。根据本发明的一实施例,当第一开关元件411导通而第二开关元件412不导通时,开关芯片400将第一信号S1提供至第二引脚430。根据本发明的另一实施例,当第一开关元件411不导通而第二开关元件412导通时,开关芯片400将第一信号S1提供至第三引脚440。此时开关芯片400是等效为一1:2解多工器(未显示其控制端)。

根据本发明的另一实施例,第二引脚430接收到第二信号S2且第三引脚440接收到第三信号S3。根据本发明的一实施例,当第一开关元件411导通而第二开关元件412不导通时,开关芯片400将第二信号S2提供至第一引脚420。根据本发明的另一实施例,当第一开关元件411不导通而第二开关元件412导通时,开关电路400将第三信号S3提供至第一引脚420。此时开关芯片400是等效为一2:1多工器(未显示其控制端)。

换句话说,开关芯片400可根据第一开关元件411以及第二开关元件412是否导通,将第一引脚420接收的信号提供至第二引脚430和/或第三引脚430。另一方面,开关芯片400也可根据第一开关元件411以及第二开关元件412是否导通,而选择性的将第二引脚430接收的信号或第三引脚440接收的信号提供至第一引脚420。在一实施例中,开关芯片400可作为一串行器、解串行器其中一个,其应用在高速传输的信号传递,例如USB、SATA、PCIE等规格中的传输信号(TX、RX等),然不以此为限。

图4的开关芯片400用以传送和/或接收单端信号,两个相同的开关芯片400即可用以传送和/或接收差动信号。为了简化说明,在此仅以传送和/或接收单端信号为例进行说明解释,并非以任何形式限定于此。

图5是显示根据本发明的另一实施例所述的由多个开关元件所构成的2:3解多工器或是3:2多工器的示意图。如图5所示,在一实施例中,开关芯片500为具有一导线架(leadframe)的封装芯片,其中开关芯片500包括晶粒510、第一引脚520、第二引脚530、第三引脚540、第四引脚550以及第五引脚560。

晶粒510包括第一开关元件511、第二开关元件512、第三开关元件513、第四开关元件514、第五开关元件515、第六开关元件516、第一接垫PAD1、第二接垫PAD2、第三接垫PAD3、第四接垫PAD4、第五接垫PAD5、第六接垫PAD6、第七接垫PAD7、第八接垫PAD8以及第九接垫PAD9。

第一开关元件511电性耦接在第一接垫PAD1以及第二接垫PAD2之间,第二开关元件512电性耦接在第二接垫PAD2以及第三接垫PAD3之间。第三开关元件513电性耦接在第四接垫PAD4以及第五接垫PAD5之间,第四开关元件514电性耦接在第五接垫以及第六接垫PAD6之间。第五开关元件515电性耦接在第七接垫PAD7以及第八接垫PAD8之间,第六开关元件516电性耦接在第八接垫PAD8以及第九接垫PAD9之间。

根据本发明的一实施例,由于第一开关元件511、第二开关元件512以及第三开关元件513分别至各个接垫PAD1、PAD2、PAD3、PAD4、PAD5之间的距离极短,第四开关元件514、第五开关元件515以及第六开关元件516分别至各个接垫PAD5、PAD6、PAD7、PAD8、PAD9之间的距离极短,因此在此忽略各个开关元件与接垫之间的走线所产生的效应。

如图5所示,晶粒510还包括第十接垫PAD10、第十一接垫PAD11、第十二接垫PAD12、第十三接垫PAD13以及第十四接垫PAD14。第十接垫PAD10通过第一导线BL1电性耦接至第一引脚520,第十一接垫PAD11通过第二导线BL2电性耦接至第二引脚530。第十二接垫PAD12通过第三导线BL3电性耦接至第三引脚540,第十三接垫PAD13通过第四导线BL4电性耦接至第四引脚550,第十四接垫PAD14通过第五导线BL5电性耦接至第五引脚560。

如图5所示,晶粒510还包括第一静电放电保护装置ESD1、第二静电放电保护装置ESD2、第三静电放电保护装置ESD3、第四静电放电保护装置ESD4以及第五静电放电保护装置ESD5。第一静电放电保护装置ESD1电性耦接至第十接垫PAD10,第二静电放电保护装置ESD2电性耦接至第十一接垫PAD11,第三静电放电保护装置ESD3电性耦接至第十二接垫PAD12,第四静电放电保护装置ESD4电性耦接至第十三接垫PAD13,第五静电放电保护装置ESD5电性耦接至第十四接垫PAD14。

根据本发明的一实施例,由于第一静电放电保护装置ESD1、第二静电放电保护装置ESD2、第三静电放电保护装置ESD3、第四静电放电保护装置ESD4以及第五静电放电保护装置ESD5分别至第十接垫PAD10、第十一接垫PAD11、第十二接垫PAD12、第十三接垫PAD13以及第十四接垫PAD14之间的距离极短,因此在此忽略各个静电放电保护装置与接垫之间的走线所产生的效应。

如图5所示,第一接垫PAD1通过第六导线BL6,电性耦接至第十接垫PAD10。第二接垫PAD2通过第七导线BL7,电性耦接至第十二接垫PAD12。第三接垫PAD3通过第八导线BL8,电性耦接至第十一接垫PAD11。第四接垫PAD4通过第九导线BL9,电性耦接至第十接垫PAD10。第五接垫PAD5通过第十导线BL10,电性耦接至第十三接垫PAD13。第六接垫PAD6通过第十一导线BL11,电性耦接至第十一接垫PAD11。

第七接垫PAD7通过第十二导线BL12,电性耦接至第十接垫PAD10。第八接垫PAD8通过第十三导线BL13,电性耦接至第十四接垫PAD14。第九接垫PAD9通过第十四导线BL14,电性耦接至第十一接垫PAD11。

根据本发明的一实施例,当第一引脚520接收第一信号S1且第二引脚530接收第二信号S2时,开关芯片500根据第一开关元件511、第二开关元件512、第三开关元件513、第四开关元件514、第五开关元件515以及第六开关元件516是否导通,而分别将第一信号S1和/或第二信号S2分别提供至第三引脚540、第四引脚550以及第五引脚560的任何一个。此时开关芯片500是等效为一2:3解多工器(未显示其控制端)。

根据本发明的另一实施例,当第三引脚540接收第三信号S3、第四引脚550接收第四信号S4以及第五引脚560接收第五信号S5时,开关芯片500根据第一开关元件511、第二开关元件512、第三开关元件513、第四开关元件514、第五开关元件515以及第六开关元件516是否导通,而选择将第三信号S3、第四信号S4以及第五信号S5的至少一个,提供至第一引脚520和/或第二引脚530。此时开关芯片500是等效为一3:2多工器(未显示其控制端)。

在一实施例中,开关芯片500可作为一串行器、解串行器其中一个,其应用在高速传输的信号传递,例如USB、SATA、PCIE等规格中,然不以此为限。

根据本发明的其他实施例,二个相同的开关芯片500可用以传送和/或接收差动信号。为了简化说明,在此仅以传送和/或接收单端信号为例进行说明解释,并非以任何形式限定于此。

如前所述的开关芯片100、200、400、500中只绘示出与本发明相关的部分,无关的其他电路并未绘示出。

本发明在此提出了开关芯片(多工器/解多工器),并且利用封装的导线(bondwire)取代晶粒中的金属走线,使得晶粒中各个元件之间的电感值能够更精确的控制,也增加设计上的弹性。此外,由于导线的阻抗值较小,因此降低了传导损耗,再加上导线没有晶粒中的金属走线的介电损耗。此外,在晶粒中不同元件之间利用导线进行耦接,有助于拓展开关芯片的操作带宽,使得开关芯片达到宽操作频带、低插入损耗、低回波损耗且高隔离的目的。

虽然本公开的实施例及其优点已公开如上,但应该了解的是,本领域技术人员,在不脱离本公开的精神和范围内,当可作更动、替代与润饰。此外,本公开的保护范围并未局限于说明书内所述特定实施例中的工艺、机器、制造、物质组成、装置、方法及步骤,本领域技术人员可从本公开一些实施例的揭示内容中理解现行或未来所发展出的工艺、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结果皆可根据本公开一些实施例使用。因此,本公开的保护范围包括上述工艺、机器、制造、物质组成、装置、方法及步骤。另外,每一权利要求构成个别的实施例,且本公开的保护范围也包括各个权利要求及实施例的组合。

- 用于开关电源芯片的使能电路、开关电源芯片及控制方法

- 一种用于开关电源芯片的抖频电路及开关电源芯片