微处理器电路以及其存储器的数据保护方法

文献发布时间:2023-06-19 11:19:16

技术领域

本发明是有关于一种微处理器电路以及其存储器的数据保护方法,且特别是有关于一种可即时锁定受保护数据的微处理器电路以及其存储器的数据保护方法。

背景技术

在现有技术领域中,微处理器提供内建的快闪存储器以做数据储存使用。这样的优点在于微处理器可通过其中的存储器控制器直接控制快闪存储器的数据存取动作,具有较快的读写速度,且又不需要设置外挂存储器,可节省成本及电路空间。

如果要在快闪存储器中放重要数据,现有技术的数据保护机制在发生篡改事件(Tamper Event),则将快闪存储器中所储存的受保护数据进行抹除(Erase),以防止受保护数据被读出。

然而,快闪存储器的数据抹除动作需要一定的时间,如果有人在这段期间中断数据抹除的动作(例如:将微处理器断电),将造成受保护数据未被完全清除,攻击者将可以读到部分的数据受保护数据。

发明内容

本发明提供一种微处理器电路以及其存储器的数据保护方法,可有效防止受保护数据被读出或篡改。

本发明的存储器的数据保护方法包括:侦测数据篡改事件有无发生以产生触发信号;依据触发信号以在第一时间区间对存储器写入锁定信号,其中锁定信号用以使存储器的受保护数据无法被读出;依据锁定信号,以在第二时间区间抹除存储器中的受保护数据,其中第一时间区间在该第二时间区间之前。

在本发明的一实施例中,上述的锁定信号的位数小于一预设值。

在本发明的一实施例中,上述的锁定信号的位数等于1,且存储器为非挥发性存储器。

在本发明的一实施例中,上述的第一时间区间的长度小于第二时间区间的长度。

在本发明的一实施例中,上述的依据触发信号以在第一时间区间对存储器写入锁定信号的步骤包括:当触发信号指示数据篡改事件发生时,在第一时间区间对存储器写入为第一逻辑准位的锁定信号。

在本发明的一实施例中,存储器的数据保护方法更包括:在第二时间区间以后,当受保护数据被抹除后,清除锁定信号为第二逻辑准位,其中第一逻辑准位与第二逻辑准位不相同。

本发明的微处理器电路包括数据篡改事件侦测器、存储单元阵列以及存储器控制器。数据篡改事件侦测器用以侦测数据篡改事件有无发生以产生触发信号。存储器控制器耦接数据篡改事件侦测器以及存储单元阵列。存储器控制器接收触发信号并依据触发信号以在第一时间区间对存储器阵列写入锁定信号,其中锁定信号用以使存储单元阵列中的受保护数据无法被读出。存储器控制器并依据锁定信号以在第二时间区间抹除存储单元阵列中的受保护数据。

基于上述,本发明通过在数据篡改事件发生时,快速的对存储器写入锁定信号。并通过锁定信号来锁定存储器的受保护数据不被读出。基于锁定信号的写入动作可以快速的被完成,可降低攻击者读取到完整的或部分的受保护数据的机率,提高系统的安全性。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。在附图中:

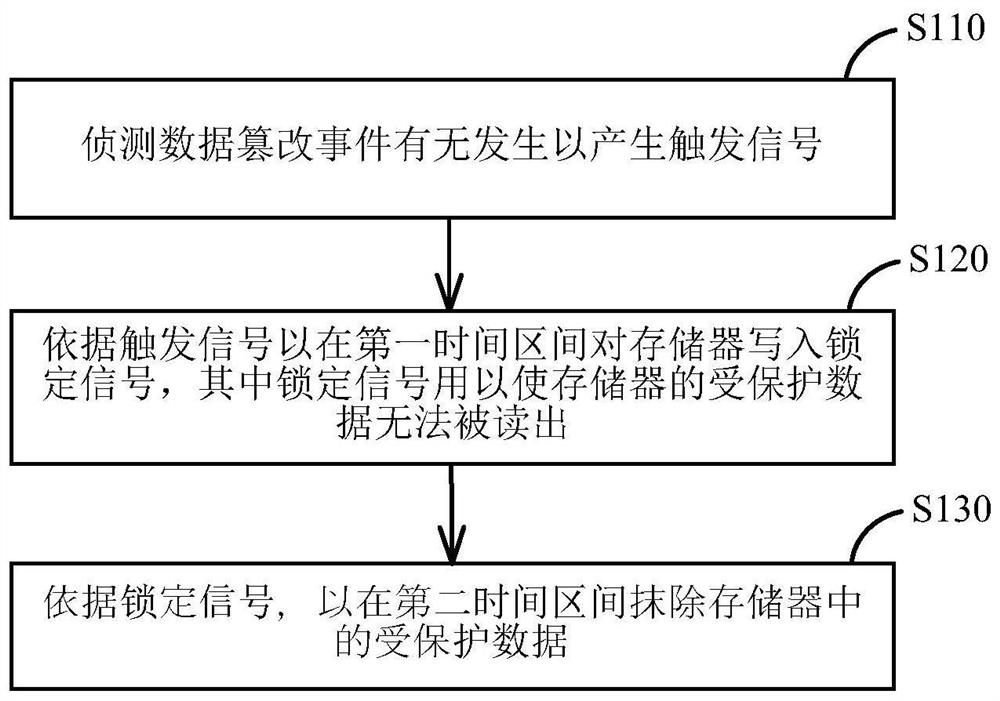

图1为本发明一实施例的存储器的数据保护方法的流程图;

图2为本发明另一实施例的存储器的数据保护方法的流程图;

图3为本发明一实施例的微处理器的示意图。

300:微处理器;

310:数据篡改事件侦测器;

320:存储器;

321:存储器控制器;

322:存储单元阵列;

330:核心电路;

LS:锁定信号;

S110~S130、S210~S250:数据保护步骤;

TGS触发信号。

具体实施方式

请参照图1,图1为本发明一实施例的存储器的数据保护方法的流程图。其中,步骤S110中,针对数据篡改事件有无发生进行侦测,并藉以产生一触发信号。接着,在步骤S120中,若在当数据篡改事件发生时,依据步骤S110中所产生的触发信号以在第一时间区间对存储器写入一锁定信号,其中,锁定信号用以使存储器的受保护数据无法被读出。在步骤S130中,则依据存储器中的锁定信号,以在第一时间区间后的第二时间区间抹除存储器中的受保护数据。

细节上来说明,在本发明实施例中,本发明实施例中的存储器可以为一非挥发性存储器,例如:快闪存储器、电阻式存储器或其他任意形式可提供数据读取、数据写入以及数据抹除的非挥发性存储器。在步骤S110中,若侦测数据篡改事件发生时,可对应产生触发信号,并依据触发信号,在步骤S120中产生锁定信号,并将锁定信号写入至存储器中。

在此请注意,在本发明实施例中,锁定信号的位数可以小于预设的一临界值。如此一来,在针对存储器写入锁定信号时所需要的时间,可以控制在一个相对短的时间中。在本发明实施例中,锁定信号的位数可以为1个位。因此,针对存储器写入锁定信号,可以快速的被完成。在本发明实施例中,当数据篡改事件发生时,依据触发信号所产生的锁定信号可以为第一逻辑准位。第一逻辑准位可以为逻辑0或逻辑1,没有一定的限制。

在上述的说明中,锁定信号作为存储器的受保护数据可否被读出的依据。具体来说明,当针对存储器进行读取动作时,需先判断存储器中所储存的锁定信号是否为第一逻辑准位。若存储器中所储存的锁定信号为第一逻辑准位时,针对存储器所进行的读取动作将被禁止而无法执行。相对的,若存储器中所储存的锁定信号非为第一逻辑准位(为第二逻辑准位)时,针对存储器所进行的读取动作可以被执行。

在步骤S130中,则依据为第一逻辑准位的锁定信号,在第一时间区间后的第二时间区间,抹除存储器中的受保护数据。其中,基于受保护数据的位数大于锁定信号的位数,第二时间区间的长度会长于第一时间区间的长度。

在此请注意,本发明实施例在当数据篡改事件发生时,快速的依据触发信号以对存储器写入锁定信号,并快速的完成对存储器中的受保护数据进行锁定动作,以防止受保护数据被读出。基于锁定信号的写入动作所需要的时间甚短,攻击者将无法快速的对存储器执行断电,以企图通过断电的方式来达到读取受保护数据的目的。并且,本发明实施例在锁定信号写入动作完成后,将受保护数据由存储器中抹除,阻绝受保护数据被攻击者读出的可能。

基于存储器为非挥发性存储器,针对存储器所执行的断电动作,并不能变更存储器中的锁定信号的数值。也就是说,针对存储器所执行的断电动作,并无法窃取存储器中的受保护数据。

进一步来说明,在当受保护数据完成由存储器中抹除的动作后,本发明实施例并可将存储器中的锁定信号清除,例如使存储器中的锁定信号为第二逻辑准位。

以下请参照图2,图2为本发明另一实施例的存储器的数据保护方法的流程图。其中,步骤S210中,针对储存在存储器中的锁定信号进行检查,并判断锁定信号指示受保护数据是否为被锁定状态(步骤S220)。当步骤S220中,判断出锁定信号指示受保护数据为被锁定状态,执行步骤S230,相对的,若步骤S220中判断出锁定信号指示受保护数据非为被锁定状态,则重新执行步骤S210。

在另一方面,本发明实施例的步骤S241中,并即时的针对有无发生数据篡改事件进行侦测。在当数据篡改事件发生时,通过产生触发信号,以在步骤S242中对存储器写入为第一逻辑准位的锁定信号。此外,在步骤S230中,则进行存储器中的受保护数据的被抹除动作。并在步骤S230完成后,执行步骤S250以清除存储器中的锁定数据为第二逻辑准位。

步骤S250完成后则重新执行步骤S210,并针对锁定信号的逻辑准位进行检查动作。

以下请参照图3,图3为本发明一实施例的微处理器的示意图。微处理器300包括数据篡改事件侦测器310、存储器320以及核心电路330。存储器320包括存储器控制器321以及存储单元阵列322。数据篡改事件侦测器310耦接至存储器320,用以侦测有无发生数据篡改事件。在当数据篡改事件侦测器310侦测出有发生数据篡改事件时,则产生触发信号TGS,并将触发信号TGS传送至存储器320中。

存储器320另耦接至核心电路330。存储器320可依据所接收的触发信号TGS来产生锁定信号LS。其中,存储器控制器321接收锁定信号LS,并将例如为第一逻辑准位的锁定信号LS写入至存储单元阵列322的一个或部分位中。此外,存储器控制器321并可即时的判读存储单元阵列322中的锁定信号LS的逻辑准位,并在当锁定信号LS为第一逻辑准位时,将存储单元阵列322中所储存的受保护数据抹除。

在另一方面,当存储器控制器321完成受保护数据的抹除动作后,存储器控制器321可另清除存储单元阵列322中的锁定信号LS为第二逻辑准位。

附带一提的,核心电路330可发送存取命令以针对存储器320执行存取动作。当存储器控制器321接收到核心电路330所发送的存取命令后,可先读取存储单元阵列322中所储存的锁定信号LS。若存储单元阵列322中所储存的锁定信号LS为第一逻辑准位时,存储器控制器321将会阻绝核心电路330所发送存取命令,并不传送存储单元阵列322中的受保护数据至核心电路330。相对的,若当存储单元阵列322中所储存的锁定信号LS为第二逻辑准位时,存储器控制器321则可依据核心电路330所发送存取命令来对存储单元阵列322进行存取动作。

在本实施例中,数据篡改事件侦测器310可应用本领域技术人员所熟知的电路来建构,没有特别的限制。此外,存储单元阵列322可以为非挥发性存储单元阵列,而锁定信号LS的位数可以为1。

综上所述,本发明通过在数据篡改事件发生时,快速的针对存储器写入具有少数位数的锁定信号,以即时的完成受保护数据的锁定动作。如此一来,攻击者将没有时间可以通过断电的方式,来破解受保护数据的保护机制。可有效防止受保护数据的任一部分被读出。

虽然本发明已以实施例揭露如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰,故本发明的保护范围当视本案的权利要求保护范围所界定者为准。

- 微处理器电路以及其存储器的数据保护方法

- 存储器的集成电路上的数据保护方法及相关的存储器电路