用于栅极绑定关断的新颖标准单元架构

文献发布时间:2023-06-19 12:21:13

本申请是申请日为2018年12月7日,国际申请号为PCT/US2018/064371、申请号为201880088197.5、发明名称为“用于栅极绑定关断的新颖标准单元架构”的申请的分案申请。

背景技术

优先权要求

本专利申请要求于2018年2月1日提交的题为“A NOVEL STANDARD CELLARCHITECTURE FOR GATE TIE-OFF(用于栅极绑定关断的新颖标准单元架构)”的申请No.15/886,611的优先权,该申请被转让给本申请受让人并由此通过援引明确纳入于此。

领域

本公开的诸方面一般涉及隔离结构,并且尤其涉及栅极绑定关断结构。

背景

半导体芯片(管芯)可包括大量的晶体管以及用于在芯片上的各晶体管之间提供电隔离的隔离结构。此类隔离结构的示例是栅极绑定关断结构,其中虚设栅极被电耦合(绑定)至源极。

概述

以下给出对一个或多个实施例的简化概述以提供对此类实施例的基本理解。此概述不是所有构想到的实施例的详尽综览,并且既非旨在标识所有实施例的关键性或决定性要素亦非试图界定任何或所有实施例的范围。其唯一的目的是要以简化形式给出一个或多个实施例的一些概念以作为稍后给出的更加具体的说明之序。

第一方面涉及一种芯片。该芯片包括:第一栅极、第二栅极、第一源极、设置在第一源极上的第一源极触点、在第一源极触点和第一栅极上方的金属互连、将第一栅极电耦合至该金属互连的第一栅极触点、以及将第一源极触点电耦合至该金属互连的第一通孔。该芯片还包括电源轨以及将第一源极触点电耦合至该电源轨的第二通孔。第二栅极处于第一源极与第一栅极之间,并且金属互连在第二栅极上方通过。

第二方面涉及一种芯片。该芯片包括:第一栅极、第一源极、设置在第一源极上的第一源极触点、在第一源极触点和第一栅极上方的第一金属互连、将第一栅极电耦合至第一金属互连的第一栅极触点、以及将第一源极触点电耦合至第一金属互连的第一通孔。该芯片还包括:第二栅极、第二源极、设置在第二源极上的第二源极触点、在第二源极触点和第二栅极上方的第二金属互连、将第二栅极电耦合至第二金属互连的第二栅极触点、以及将第二源极触点电耦合至第二金属互连的第二通孔。第一金属互连和第二金属互连中的每一者均沿第一横向方向延伸,第一金属互连在第二横向方向上与第二金属互连对准,并且第一横向方向大致垂直于第二横向方向。

为了实现前述以及相关目的,一个或多个实施例包括随后完整描述的以及在权利要求书中具体指出的特征。以下说明和所附插图详细阐述了这一个或多个实施例的某些解说性方面。但是,这些方面仅仅是指示了可采用各个实施例的原理的各种方式中的若干种,并且所描述的实施例旨在涵盖所有此类方面及其等效方案。

附图简述

图1示出了根据本公开的某些方面的栅极绑定关断结构的示例。

图2A示出了根据本公开的某些方面的两个单元的源极至源极邻接的示例。

图2B示出了根据本公开的某些方面的两个单元的源极至漏极邻接的示例。

图2C示出了根据本公开的某些方面的两个单元的漏极至漏极邻接的示例。

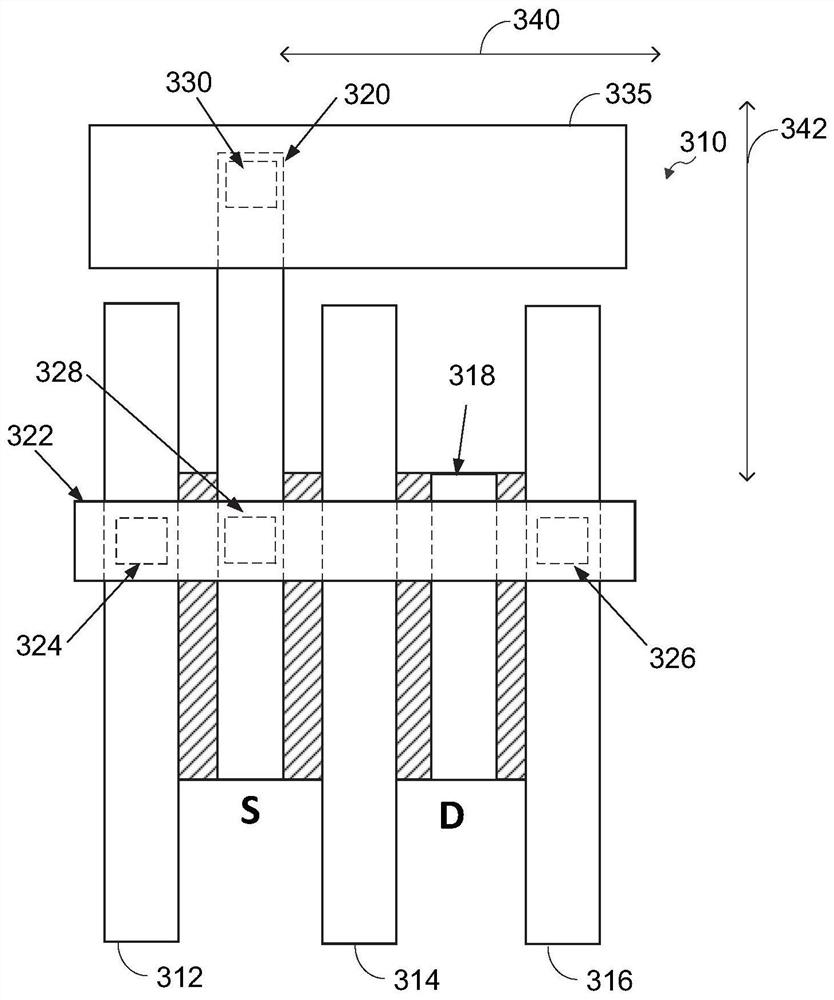

图3A示出了根据本公开的某些方面的包括金属互连的示例性栅极绑定关断结构的俯视图。

图3B示出了图3A中示出的示例性栅极绑定关断结构的侧视图。

图4A示出了根据本公开的某些方面的第一单元和第二单元的漏极至漏极邻接的示例的俯视图。

图4B示出了图4A中示出的漏极至漏极邻接的侧视图。

图5A示出了根据本公开的某些方面的第一单元和第二单元的源极至漏极邻接的示例的俯视图。

图5B示出了图5A中示出的源极至漏极邻接的侧视图。

图6A示出了根据本公开的某些方面的第一单元和第二单元的源极至源极邻接的示例的俯视图。

图6B示出了图6A中示出的源极至源极邻接的侧视图。

图7A示出了根据本公开的某些方面的第一单元和第二单元的漏极至漏极邻接的另一示例的俯视图。

图7B示出了图7A中示出的漏极至漏极邻接的侧视图。

图8A示出了根据本公开的某些方面的第一单元和第二单元的源极至漏极邻接的另一示例的俯视图。

图8B示出了图8A中示出的源极至漏极邻接的侧视图。

图9A示出了根据本公开的某些方面的第一单元和第二单元的源极至源极邻接的另一示例的俯视图。

图9B示出了图9A中示出的源极至源极邻接的侧视图。

图10A示出了根据本公开的某些方面的包括栅极绑定关断结构的单元的示例的俯视图。

图10B示出了图10A中示出的单元的侧视图。

图11示出了根据本公开的某些方面的其中图10A中的单元包括多个鳍的示例的立体视图。

图12A示出了根据本公开的某些方面的包括栅极绑定关断结构的单元的另一示例的俯视图。

图12B示出了图12A中示出的单元的侧视图。

图13A示出了根据本公开的某些方面的用于单元的多条轨道的示例。

图13B示出了根据本公开的某些方面的用于多个单元的多条轨道的示例。

详细描述

以下结合附图阐述的详细描述旨在作为各种配置的描述,而无意表示可实践本文中所描述的概念的仅有配置。本详细描述包括具体细节以提供对各种概念的透彻理解。然而,对于本领域技术人员将显而易见的是,没有这些具体细节也可以实践这些概念。在一些实例中,以框图形式示出众所周知的结构和组件以便避免湮没此类概念。

半导体芯片(管芯)可包括大量的晶体管以及用于在芯片上的各晶体管之间提供电隔离的隔离结构。此类隔离结构的示例是栅极绑定关断结构,其中虚设栅极被电耦合(绑定)至源极。将虚设栅极耦合至源极关断了虚设栅极下方的沟道,藉此在虚设栅极的相对侧上的各晶体管之间提供电隔离。

图1示出了根据本公开的某些方面的包括栅极绑定关断结构的单元105的示例的俯视图。在该示例中,单元105包括有源区110以及多个栅极120、122、124、126、128和130。对于鳍型场效应晶体管(finFET)工艺,有源区110可包括在横向方向150上跨单元105延伸的多个鳍。为解说简单起见,图1中未示出个体鳍。如本文所使用的,术语“横向”是指平行于芯片的基板延伸的方向。

有源区110以及栅极122、126和128形成单元105中的晶体管。对于finFET工艺的示例,在有源区110的鳍的相应部分上形成每个栅极122、126和128,其中薄介电层被设置在栅极与鳍之间。在该示例中,每个栅极122、126和128形成单元110中的晶体管的栅极,其中在栅极的相对侧上的鳍的各部分形成晶体管的源极和漏极。

在图1中示出的示例中,栅极绑定关断结构包括栅极124以及将栅极124电耦合(绑定)至相邻(毗邻)源极140的触点135。触点135可通过设置在源极140上的源极触点(图1中未示出)来耦合至源极。将栅极124耦合至源极140关断了栅极124下方的沟道,藉此在栅极124的相对侧上的各晶体管之间提供电隔离。触点135由接触层形成,该接触层还可被用于形成用于将晶体管的栅极耦合至上层互连金属层(未示出)的栅极触点(未示出)。如果源极140是p型场效应晶体管(PFET)的源极,则源极140可被耦合至电压供电轨,并且如果源极140是n型场效应晶体管(NFET)的源极,则源极140可被耦合至接地轨。

图1中示出的栅极绑定关断结构在栅极124的相对侧上的各晶体管之间提供电隔离,而不必切割(破坏)栅极124下方的鳍。这是因为栅极关断结构通过将栅极124耦合(绑定)至源极140来关断栅极124下方的沟道。作为结果,有源区110的鳍可在栅极124下方连续地延伸。

在替换的电隔离办法中,在栅极124下方切割鳍,以在栅极124的相对侧上的各晶体管之间提供电隔离。在该办法中,通过切割鳍形成的空间被填充有电隔离材料(例如,电介质材料),该电隔离材料在鳍中引入了对工艺变化敏感的应力。鳍中的应力改变了单元105中的晶体管的电特性。由于鳍中的应力对工艺变化敏感,因此晶体管的电特性的所得变化也对工艺变化敏感,从而导致晶体管的电特性的不确定性。栅极绑定关断结构通过在栅极124的相对侧上的各晶体管之间提供电隔离而不必切割(破坏)栅极124下方的鳍来克服该缺点。

图1中示出的示例性栅极绑定关断结构可被用于将彼此邻接的两个单元中的晶体管电隔离。就此而言,以下图2A-2C示出了针对两个单元的三种不同邻接场景的示例。

图2A示出了第一单元205和第二单元208的源极至源极邻接的示例的俯视图。第一单元205包括多个栅极210、212和214、源极(标记为“S”)、和漏极(标记为“D”)。栅极212、源极和漏极形成第一单元205中的晶体管。第一单元205还包括设置在漏极上的漏极触点216以及设置在源极上的源极触点218。漏极触点和源极触点216和218可由接触层形成,该接触层可不同于用于形成栅极触点(未示出)的接触层。第一单元205还包括通孔222,该通孔222将源极触点218(以及因此源极)电耦合至位于源极触点218上方的电源轨224。对于其中源极是PFET的源极的示例,电源轨224可以是电压供电轨,并且对于其中源极是NFET的源极的示例,电源轨可以是接地轨。注意,在图2A中以虚线示出了电源轨224下方的结构。

第一单元205进一步包括栅极绑定关断结构,该栅极绑定关断结构包括栅极214以及将栅极214电耦合(绑定)至源极触点218(以及因此第一单元205中的源极)的触点220。通过将栅极214耦合至源极,栅极绑定关断结构关断了栅极214下方的沟道,藉此为第一单元205中的晶体管提供电隔离。

第二单元208包括多个栅极226、228和230、源极(标记为“S”)、和漏极(标记为“D”)。栅极228、源极和漏极形成第二单元208中的晶体管。第二单元208还包括设置在漏极上的漏极触点232以及设置在源极上的源极触点234。漏极触点和源极触点232和234可由用于形成第一单元205中的漏极触点和源极触点216和218的相同接触层形成。第二单元208还包括通孔238,该通孔238将源极触点234(以及因此源极)电耦合至位于源极触点234上方的电源轨240。注意,在图2A中以虚线示出了电源轨240下方的结构。

第二单元208进一步包括栅极绑定关断结构,该栅极绑定关断结构包括栅极226以及将栅极226电耦合(绑定)至源极触点234(以及因此第二单元208中的源极)的触点236。通过将栅极226耦合至源极,栅极绑定关断结构关断了栅极226下方的沟道,藉此为第二单元208中的晶体管提供电隔离。

图2A的右手侧示出了其中第一单元205的源极侧邻接第二单元208的源极侧的示例。在该示例中,栅极214和226被合并成栅极242,其中栅极242通过触点220来耦合至第一单元205中的源极,并且通过触点236来耦合至第二单元208中的源极。此外,第一单元和第二单元中的源极被耦合至位于源极触点218和238上方的共用电源轨244。由于栅极242被耦合(绑定)至第一单元205和第二单元208中的源极,因此栅极242下方的沟道被关断,藉此在第一单元205和第二单元208中的各晶体管之间提供电隔离。在该示例中,栅极242是通过触点220和236耦合至两个相邻源极的虚设栅极。因此,图1中示出的栅极绑定关断结构支持两个单元的源极至源极邻接。

图2B示出了第一单元246和第二单元248的源极至漏极邻接的示例的俯视图。第一单元246在结构上与以上参考图2A讨论的第一单元205相同。因此,以上提供的第一单元205的描述适用于图2B中的第一单元246。

第二单元248包括多个栅极250、252和254、源极(标记为“S”)、和漏极(标记为“D”)。栅极252、源极和漏极形成第二单元248中的晶体管。第二单元248还包括设置在漏极上的漏极触点256以及设置在源极上的源极触点258。第二单元248还包括通孔262,该通孔262将源极触点258(以及因此源极)电耦合至位于源极触点258上方的电源轨266。注意,以虚线示出了电源轨266下方的结构。

第二单元248进一步包括栅极绑定关断结构,该栅极绑定关断结构包括栅极254以及将栅极254电耦合(绑定)至源极触点258(以及因此第二单元248中的源极)的触点260。通过将栅极254耦合至源极,栅极绑定关断结构关断了栅极254下方的沟道,藉此为第二单元248中的晶体管提供电隔离。

图2B的右手侧示出了其中第一单元246的源极侧邻接第二单元248的漏极侧的示例。在该示例中,栅极214和250被合并成栅极268,其中栅极268通过触点220来耦合至第一单元246中的源极。而且,第一单元和第二单元中的源极被耦合至共用电源轨270。由于栅极268被耦合(绑定)至第一单元246中的源极,因此栅极268下方的沟道被关断,藉此在第一单元246和第二单元248中的各晶体管之间提供电隔离。在该示例中,栅极268是通过触点220耦合至两个相邻源极之一的虚设栅极。因此,图1中示出的栅极绑定关断结构支持两个单元的源极至漏极邻接。

图2C示出了第一单元272和第二单元274的漏极至漏极邻接的示例的俯视图。如以下进一步解释的,以上讨论的栅极绑定关断结构不支持两个单元的漏极至漏极邻接。

第一单元272包括多个栅极276、278和280、源极(标记为“S”)、和漏极(标记为“D”)。栅极278、源极和漏极形成第一单元272中的晶体管。第一单元272还包括设置在漏极上的漏极触点282以及设置在源极上的源极触点284。漏极触点和源极触点282和284可由接触层形成,该接触层可不同于用于形成栅极触点(未示出)的接触层。第一单元272还包括通孔288,该通孔288将源极触点284(以及因此源极)电耦合至位于源极触点284上方的电源轨290。注意,在图2C中以虚线示出了电源轨290下方的结构。

第一单元272进一步包括栅极绑定关断结构,该栅极绑定关断结构包括栅极276以及将栅极276电耦合(绑定)至源极触点284(以及因此第一单元272中的源极)的触点286。通过将栅极276耦合至源极,栅极绑定关断结构关断了栅极276下方的沟道,藉此为第一单元272中的晶体管提供电隔离。

第二单元274在结构上与以上参考图2B讨论的第二单元248相同。因此,以上提供的第二单元248的描述适用于图2C中的第二单元274。

图2C的右手侧示出了其中第一单元272的漏极侧邻接第二单元274的漏极侧的示例。栅极280和250被合并成栅极292,并且第一单元和第二单元中的源极被耦合至共用电源轨294。在该示例中,栅极292在两侧上被漏极包围,而不具有相邻的源极。因此,栅极292不能使用触点来耦合(绑定)至源极以在第一单元272和第二单元274中的各晶体管之间提供电隔离。因此,以上讨论的栅极绑定关断结构不支持两个单元的漏极至漏极邻接。

以上讨论的栅极绑定关断结构的另一挑战在于,可能难以控制将虚设栅极耦合至源极的触点的对准。触点的失准可导致触点接触毗邻晶体管的栅极,从而使该晶体管的栅极与源极短路。这可能会永久关断晶体管,从而使晶体管无法工作。

因此,存在对克服以上讨论的一个或多个缺点的栅极绑定关断结构的需要。

就此而言,图3A示出了根据本公开的某些方面的用于芯片上的单元310的示例性栅极绑定关断结构的俯视图。如之前进一步讨论的,图3A中示出的示例性栅极绑定关断结构支持两个单元的漏极至漏极邻接。

在该示例中,单元310包括多个栅极312、314和316、源极(标记为“S”)、和漏极(标记为“D”)。在该示例中,栅极312和316位于单元310的边界上。栅极314、源极和漏极形成单元310中的晶体管。单元310还包括设置在漏极上的漏极触点318以及设置在源极上的源极触点320。漏极触点和源极触点318和320可由接触层形成,该接触层可不同于用于形成栅极触点的接触层。单元310还包括通孔330,该通孔330将源极触点320(以及因此源极)电耦合至位于源极触点320上方的电源轨335。注意,在图3A中以虚线示出了电源轨335下方的结构。对于其中单元310中的晶体管是PFET的示例,电源轨335可以是电压供电轨(例如,Vdd轨),并且对于其中单元310中的晶体管是NFET的示例,电源轨335可以是接地轨(例如,Vss轨)。

栅极绑定关断结构包括金属互连322,该金属互连322可由芯片(管芯)的后端工艺(BEOL)中的金属层(即,最底部金属层)形成。金属互连322位于栅极312、314和316、漏极触点318和源极触点320上方。注意,以虚线示出了金属互连322下方的结构。在图3A中的示例中,金属互连322在横向方向340上跨单元310延伸。在一些方面,金属互连322可由用于形成电源轨335的相同金属层(例如,使用光刻和蚀刻工艺)形成,并且可平行于电源轨335延伸。例如,金属互连322和电源轨335可由芯片的BEOL中的相同金属层(例如,最底部金属层)形成。

栅极绑定关断结构还包括设置在栅极312与金属互连322之间的第一栅极触点324、设置在栅极316与金属互连322之间的第二栅极触点326、以及设置在源极触点320与金属互连322之间的通孔328。在该示例中,第一栅极触点324将栅极312耦合至金属互连322,第二栅极触点326将栅极316耦合至金属互连322,并且通孔328将源极触点320耦合至金属互连322。因此,栅极312通过第一栅极触点324、金属互连322和通孔328来电耦合至源极触点320(以及因此源极)。类似地,栅极316通过第二栅极触点326、金属互连322和通孔328来电耦合至源极触点320(以及因此源极)。因此,在该示例中,栅极312和316是通过金属互连322来电耦合(绑定)至源极的虚设栅极。由于栅极312和316位于单元310的边界上,因此将栅极312和316通过金属互连322电耦合至源极为单元310中的晶体管提供与其他单元(未示出)的电隔离。

图3B示出了示例性栅极绑定关断结构的侧视图。如图3B中所示,金属互连322在漏极触点318上方通过(穿过),并且在纵向方向344上与漏极触点318分隔开一空间(间隙)。该空间可被填充有电隔离材料以将金属互连322与漏极触点318电隔离,从而允许金属互连322在漏极触点318上方通过而不会与漏极触点318电短路。金属互连322还在单元310中的晶体管的栅极314上方通过(穿过),并且在纵向方向344上与该晶体管的栅极314分隔开一空间(间隙)。该空间可被填充有电隔离材料以将金属互连322与栅极314电隔离,从而允许金属互连322在栅极314上方通过而不会与栅极314电短路。如本文所使用的,术语“纵向”是指垂直于芯片的基板延伸的方向。

因此,金属互连322在漏极触点318和晶体管的栅极314上方通过(穿过),而不会与漏极触点318和晶体管的栅极314电短路。这允许金属互连将虚设栅极316耦合至源极触点320(以及因此源极),即使虚设栅极316不毗邻于源极。作为对比,以上参考图1讨论的栅极绑定关断结构要求虚设栅极具有相邻(毗邻)的源极,以便将该虚设栅极耦合(绑定)至源极。图3A和3B中示出的示例性栅极绑定关断结构不具有这种限制,从而允许漏极至漏极邻接,如以下进一步讨论的。

在图3B所示的示例中,源极和漏极被描绘为用于平面晶体管的芯片(管芯)的基板中的掺杂区。然而,应领会,对于finFET的示例,源极和漏极可由在横向方向340上跨单元310延伸的多个鳍(图3B中未示出)形成。因此,应领会,本公开的各方面适用于平面晶体管和finFET两者。

如图3A中所示,漏极触点318在横向方向342上在金属互连322下方延伸。这允许漏极触点318在漏极的更大区域上延伸,这减小了漏极的接触电阻。漏极触点318能够在金属互连322下方延伸,因为金属互连322在纵向方向344上与漏极触点310分隔开一空间(间隙),该空间防止金属互连322与漏极触点318短路。对于finFET工艺,这允许漏极触点318在横向方向342上跨单元310延伸,并且为了较低的接触电阻而与所有鳍接触。

在金属互连322与漏极触点318之间不具有空间(间隙)的情况下,漏极触点318无法在漏极触点318不与金属互连322短路的情况下在金属互连322下方通过。在该情形中,漏极触点仅能部分地在漏极上延伸,其中漏极触点和金属互连需要在横向方向342上分隔开一裕量,以防止漏极触点与金属互连短路。与图3A中示出的可为了较低的接触电阻而在横向方向342上完全跨漏极延伸的漏极触点318相比,在该情形中的部分漏极触点可显著增加漏极的接触电阻。

在某些方面,栅极触点324和326是使用自对准触点工艺形成的自对准栅极触点。对于每个栅极,自对准触点工艺可包括以下步骤。可以在栅极的相对侧上形成间隔物(例如,氮化物间隔物),其中间隔物之间的空间被填充有填充材料(例如,氧化物材料)。随后可以使用选择性蚀刻工艺来移除填充材料,该选择性蚀刻工艺蚀刻掉填充材料而不蚀刻掉间隔物,藉此在间隔物之间创建开口。所得开口处于栅极正上方,并且通过隔离物与(诸)相邻的漏极/源极触点电隔离。随后可以在开口中沉积金属以形成相应的栅极触点。所得栅极触点是自对准的。这是因为间隔物(例如,氮化物间隔物)限定了在其中形成栅极触点的开口,从而使得栅极触点的形成显著更容忍栅极触点图案失准。自对准栅极触点有助于防止栅极触点的失准,这促成栅极触点与相邻的漏极/源极触点并排放置,而不会使栅极触点与相邻的漏极/源极触点短路。

图3B示出了其中栅极触点324和326被直接耦合至金属互连322的示例。然而,将领会,本公开并不限于此示例。例如,栅极触点324和326中的每一者可通过设置在栅极触点与金属互连322之间的相应通孔来耦合至金属互连322。

参考图3A,应领会,漏极触点318可被耦合至信号路由结构(未示出)以用于向和/或从漏极路由信号。路由结构可包括设置在漏极触点318上的通孔(未示出),其中该通孔在横向方向342上从金属互连322偏移,以防止漏极与金属互连322短路。类似地,应领会,晶体管的栅极314可被耦合至信号路由结构(未示出)以用于向和/或从栅极314路由信号。路由结构可包括设置在栅极314上的栅极触点(未示出),其中该栅极触点在横向方向342上从金属互连322偏移,以防止栅极314与金属互连322短路。

应领会,单元310可包括栅极312与316之间的附加晶体管,其中栅极312和316通过金属互连322来耦合至单元310中的至少一个晶体管的源极。由于栅极312和316位于单元310的边界上,因此将栅极312和316通过金属互连322耦合到至少一个晶体管的源极将单元310中的晶体管与其他单元(未示出)电隔离。在该示例中,金属互连322可在横向方向340上在单元310中的晶体管上方延伸。

如以上讨论的,图3A和3B中示出的示例性栅极绑定关断结构支持两个单元的漏极至漏极邻接。现在将在下面参考图4A和4B讨论此示例。

图4A示出了第一单元410和第二单元412的漏极至漏极邻接的示例的俯视图。第一单元410在结构上与以上参考图3A和3B讨论的单元310相同。因此,以上提供的单元310的描述适用于第一单元410。

第二单元412包括多个栅极414、416和418、源极(标记为“S”)、和漏极(标记为“D”)。在该示例中,栅极414和418位于第二单元412的边界上。栅极416、源极和漏极形成第二单元412中的晶体管。第二单元412还包括设置在漏极上的漏极触点420以及设置在源极上的源极触点422。第二单元412还包括通孔432,该通孔432将源极触点422(以及因此源极)电耦合至位于源极触点422上方的电源轨435。注意,以虚线示出了电源轨435下方的结构。

第二单元412进一步包括栅极绑定关断结构,该栅极绑定关断结构包括金属互连424,该金属互连424可由与第一单元410的金属互连322相同的金属层形成。金属互连424位于栅极414、416和418、漏极触点420和源极触点422上方。注意,以虚线示出了金属互连424下方的结构。在图4A中示出的示例中,金属互连424在横向方向460上跨第二单元412延伸。

栅极绑定关断结构还包括将栅极414耦合至金属互连424的第一栅极触点428、将栅极418耦合至金属互连424的第二栅极触点426、以及将源极触点422耦合至金属互连424的通孔430。在该示例中,栅极414和418是通过金属互连424来电耦合(绑定)至源极的虚设栅极。

图4B示出了第二单元412的栅极绑定关断结构的侧视图。如图4B中所示,金属互连424在漏极触点420上方通过,并且在纵向方向470上与漏极触点420分隔开一空间。这允许漏极触点420在横向方向465上在金属互连424下方延伸以减小漏极接触电阻。金属互连424还在第二单元412中的晶体管的栅极416上方通过,并且在纵向方向470上与该晶体管的栅极416分隔开一空间。

图4A和4B的右手侧示出了其中第一单元410的漏极侧邻接第二单元412的漏极侧的示例。栅极316和414被合并成栅极440,并且金属互连322和424被组合成共用金属互连445,该共用金属互连445在横向方向460上跨第一单元410和第二单元412延伸。在该示例中,栅极440通过设置在栅极440与金属互连445之间的栅极触点442来耦合至金属互连445。另外,第一单元和第二单元中的源极被耦合至共用电源轨450。

在该示例中,漏极至漏极邻接处的栅极440通过金属互连445来耦合(绑定)至第一单元410和第二单元412中的源极。金属互连445将栅极440耦合至源极,即使栅极440不具有相邻的源极(即,栅极440在两侧上被漏极包围)。这是因为互连445能够在栅极314和416上方穿过,以将栅极440分别耦合至源极触点320和422。由于栅极440通过金属互连445来耦合(绑定)至第一单元和第二单元中的源极,因此栅极440下方的沟道被关断,藉此在第一单元和第二单元中的各晶体管之间提供电隔离。因此,根据本公开的各方面的示例性栅极绑定关断结构支持两个单元的漏极至漏极邻接。示例性栅极绑定关断结构还支持源极至漏极邻接和源极至源极邻接,如以下进一步讨论的。

在图4A中示出的示例中,源极触点320和422分别通过通孔330和432来耦合至共用电源轨450。对于其中第一单元和第二单元中的晶体管是PFET的示例,电源轨450可以是电压供电轨(例如,Vdd轨),并且对于其中第一单元和第二单元中的晶体管是NFET的示例,电源轨450可以是接地轨(例如,Vss轨)。在某些方面,电源轨450可由与金属互连445相同的金属层(例如BEOL的最底部金属层)(例如,使用光刻和蚀刻工艺)形成,并且平行于金属互连445延伸。

图5A示出了第一单元510和第二单元512的源极至漏极邻接的示例的俯视图。第一单元510包括多个栅极514、516和518、源极(标记为“S”)、和漏极(标记为“D”)。在该示例中,栅极514和518位于第一单元510的边界上。栅极516、源极和漏极形成第一单元510中的晶体管。第一单元510还包括设置在漏极上的漏极触点520以及设置在源极上的源极触点522。第一单元510还包括通孔532,该通孔535将源极触点522(以及因此源极)电耦合至位于源极触点522上方的电源轨535。注意,以虚线示出了电源轨535下方的结构。

第一单元510进一步包括栅极绑定关断结构,该栅极绑定关断结构包括金属互连524,该金属互连524可由芯片的BEOL中的金属层(例如,最底部金属层)形成。金属互连524位于栅极514、516和518、漏极触点520和源极触点522上方。注意,以虚线示出了金属互连524下方的结构。在图5A中示出的示例中,金属互连524在横向方向560上跨第一单元510延伸。

栅极绑定关断结构还包括将栅极514耦合至金属互连524的第一栅极触点528、将栅极518耦合至金属互连524的第二栅极触点526、以及将源极触点522耦合至金属互连524的通孔530。在该示例中,栅极514和518是通过金属互连524来电耦合(绑定)至源极的虚设栅极。

图5B示出了第一单元510的栅极绑定关断结构的侧视图。如图5B中所示,金属互连524在漏极触点520上方通过,并且在纵向方向570上与漏极触点520分隔开一空间。这允许漏极触点520在横向方向565上在金属互连524下方延伸以减小漏极接触电阻。金属互连524还在第一单元510中的晶体管的栅极516上方通过,并且在纵向方向570上与该晶体管的栅极516分隔开一空间。

第二单元512在结构上与以上参考图4A和4B讨论的第二单元412相同。因此,以上提供的第二单元412的描述适用于图5A和5B中示出的第二单元512。

图5A和5B的右手侧示出了其中第一单元510的源极侧邻接第二单元512的漏极侧的示例。栅极518和414被合并成栅极540,并且金属互连424和524被组合成共用金属互连545,该共用金属互连545在横向方向560上跨第一单元510和第二单元512延伸。在该示例中,栅极540通过设置在栅极540与金属互连545之间的栅极触点542来耦合至金属互连545。另外,第一单元和第二单元中的源极被耦合至共用电源轨550。

在该示例中,源极至漏极邻接处的栅极540通过金属互连545来耦合(绑定)至第一单元510和第二单元512中的源极。由于栅极540通过金属互连545来耦合(绑定)至第一单元和第二单元中的源极,因此栅极540下方的沟道被关断,藉此在第一单元和第二单元中的各晶体管之间提供电隔离。因此,根据本公开的各方面的示例性栅极绑定关断结构支持两个单元的源极至漏极邻接。

在图5A中示出的示例中,源极触点522和422分别通过通孔532和432来耦合至共用电源轨550。对于其中第一单元和第二单元中的晶体管是PFET的示例,电源轨550可以是电压供电轨(例如,Vdd轨),并且对于其中第一单元和第二单元中的晶体管是NFET的示例,电源轨550可以是接地轨(例如,Vss轨)。在某些方面,电源轨550可由与金属互连545相同的金属层(例如BEOL的最底部金属层)(例如,使用光刻和蚀刻工艺)形成,并且平行于金属互连545延伸。

图6A示出了第一单元610和第二单元612的源极至源极邻接的示例的俯视图。第一单元610在结构上与以上参考图5A和5B讨论的第一单元510相同。因此,以上提供的第一单元510的描述适用于图6A和6B中示出的第一单元610。

第二单元612包括多个栅极614、616和618、源极(标记为“S”)、和漏极(标记为“D”)。在该示例中,栅极614和618位于第二单元612的边界上。栅极616、源极和漏极形成第二单元612中的晶体管。第二单元612还包括设置在漏极上的漏极触点620以及设置在源极上的源极触点622。第二单元612还包括通孔632,该通孔632将源极触点622(以及因此源极)电耦合至位于源极触点622上方的电源轨635。注意,以虚线示出了电源轨635下方的结构。

第二单元612进一步包括栅极绑定关断结构,该栅极绑定关断结构包括金属互连624,该金属互连624可由与第一单元610的金属互连524相同的金属层形成。金属互连624位于栅极614、616和618、漏极触点620和源极触点622上方。注意,以虚线示出了金属互连624下方的结构。在图6A中示出的示例中,金属互连624在横向方向660上跨第二单元612延伸。

栅极绑定关断结构还包括将栅极614耦合至金属互连626的第一栅极触点624、将栅极618耦合至金属互连624的第二栅极触点628、以及将源极触点622耦合至金属互连624的通孔630。在该示例中,栅极614和618是通过金属互连624来电耦合(绑定)至源极的虚设栅极。

图6B示出了第二单元612的栅极绑定关断结构的侧视图。如图6B中所示,金属互连624在漏极触点620上方通过,并且在纵向方向670上与漏极触点620分隔开一空间。金属互连624还在第二单元612中的晶体管的栅极616上方通过,并且在纵向方向670上与该晶体管的栅极616分隔开一空间。

图6A和6B的右手侧示出了其中第一单元610的源极侧邻接第二单元612的源极侧的示例。栅极518和614被合并成栅极640,并且金属互连524和624被组合成共用金属互连645,该共用金属互连645在横向方向660上跨第一单元610和第二单元612延伸。在该示例中,栅极640通过设置在栅极640与金属互连645之间的栅极触点642来耦合至金属互连645。另外,第一单元和第二单元中的源极被耦合至共用电源轨650。

在该示例中,源极至源极邻接处的栅极640通过金属互连645来耦合(绑定)至第一单元610和第二单元612中的源极。由于栅极640通过金属互连645来耦合(绑定)至第一单元和第二单元中的源极,因此栅极640下方的沟道被关断,藉此在第一单元和第二单元中的各晶体管之间提供电隔离。因此,根据本公开的各方面的示例性栅极绑定关断结构支持两个单元的源极至源极邻接。

在图6A中示出的示例中,源极触点522和622分别通过通孔532和632来耦合至共用电源轨650。对于其中第一单元和第二单元中的晶体管是PFET的示例,电源轨650可以是电压供电轨(例如,Vdd轨),并且对于其中第一单元和第二单元中的晶体管是NFET的示例,电源轨650可以是接地轨(例如,Vss轨)。在某些方面,电源轨650可由与金属互连645相同的金属层(例如BEOL的最底部金属层)(例如,使用光刻和蚀刻工艺)形成,并且平行于金属互连645延伸。

图7A和7B分别示出了第一单元710和第二单元712的漏极至漏极邻接的另一示例的俯视图和侧视图。第一单元710类似于图4A和4B中的第一单元410,其中对于单元710和410两者而言共用的元件由相同的附图标记来标识。第一单元710与图4A和4B中的第一单元410的不同之处在于,图4A和4B中的栅极触点324被略去。作为结果,栅极312未被耦合至第一单元710的金属互连722。此外,互连722与图4A和4B中的互连322的不同之处在于,互连722未在栅极312上方延伸。

第二单元712类似于图4A和4B中的第二单元412,其中对于单元712和412两者而言共用的元件由相同的附图标记来标识。第二单元712与图4A和4B中的第二单元412的不同之处在于,图4A和4B中的栅极触点426被略去。作为结果,栅极418未被耦合至第二单元712的金属互连724。此外,互连724与图4A和4B中的互连424的不同之处在于,互连724未在栅极418上方延伸。

图7A和7B的右手侧示出了其中第一单元710的漏极侧邻接第二单元712的漏极侧的示例。栅极316和414被合并成栅极440,并且金属互连722和724被组合成共用金属互连745。在该示例中,栅极440通过设置在栅极440与金属互连745之间的栅极触点442来耦合至金属互连745。如图7A和7B中所示,漏极至漏极邻接处的栅极440通过金属互连745来电耦合至第一单元710和第二单元712中的源极。这关断了栅极440下方的沟道,藉此在第一单元710和第二单元712中的各晶体管之间提供电隔离。互连745通过在漏极触点318和420以及栅极314和416上方穿过来将栅极440耦合至源极,即使栅极440在两侧上被漏极触点318和420包围,如图7B中所示。

图8A和8B分别示出了第一单元810和第二单元812的源极至漏极邻接的另一示例的俯视图和侧视图。第一单元810类似于图5A和5B中的第一单元510,其中对于单元810和510两者而言共用的元件由相同的附图标记来标识。第一单元810与图5A和5B中的第一单元510的不同之处在于,图5A和5B中的栅极触点526被略去。作为结果,栅极518未被耦合至第一单元810的金属互连824。此外,互连824与图5A和5B中的互连524的不同之处在于,互连824未在栅极518上方延伸。

第二单元812类似于图5A和5B中的第二单元512,其中对于单元812和512两者而言共用的元件由相同的附图标记来标识。第二单元812与图5A和5B中的第二单元512的不同之处在于,图5A和5B中的栅极触点426被略去。作为结果,栅极418未被耦合至第二单元812的金属互连826。此外,互连826与图5A和5B中的互连424的不同之处在于,互连826未在栅极418上方延伸。

图8A和8B的右手侧示出了其中第一单元810的源极侧邻接第二单元812的漏极侧的示例。栅极518和414被合并成栅极540,并且金属互连824和826被组合成共用金属互连845。在该示例中,栅极540通过设置在栅极540与金属互连845之间的栅极触点542来耦合至金属互连845。如图8A和8B中所示,源极至漏极邻接处的栅极540通过金属互连845来电耦合至第一单元810和第二单元812中的源极。这关断了栅极440下方的沟道,藉此在第一单元810中的源极与第二单元812中的漏极之间提供电隔离。

图9A和9B分别示出了第一单元910和第二单元912的源极至源极邻接的另一示例的俯视图和侧视图。第一单元910类似于图6A和6B中的第一单元610,其中对于单元910和610两者而言共用的元件由相同的附图标记来标识。第一单元910与图6A和6B中的第一单元610的不同之处在于,图6A和6B中的栅极触点526被略去。作为结果,栅极518未被耦合至第一单元910的金属互连924。此外,互连924与图6A和6B中的互连524的不同之处在于,互连924未在栅极518上方延伸。

第二单元912类似于图6A和6B中的第二单元612,其中对于单元912和612两者而言共用的元件由相同的附图标记来标识。第二单元912与图6A和6B中的第二单元612的不同之处在于,图6A和6B中的栅极触点626被略去。作为结果,栅极614未被耦合至第二单元912的金属互连926。此外,互连926与图6A和6B中的互连624的不同之处在于,互连926未在栅极614上方延伸。

图9A和9B的右手侧示出了其中第一单元910的源极侧邻接第二单元912的源极侧的示例。栅极518和614在第一单元910和第二单元912的源极至源极邻接处被合并成栅极640。在该示例中,栅极640处于浮置(即,未被耦合至金属互连924或金属互连926)。此外,栅极640被第一单元910和第二单元912中的源极包围,其中源极通过共用电源轨650(例如,Vdd或Vss)被偏置在相同的电势。由于第一单元910和第二单元912中的源极在该示例中处于相同电势,因此栅极640不需要在源极之间提供电隔离,并且因此在该示例中不需要被绑定关断。

根据本公开的各方面的栅极绑定关断结构可在单元内被使用以绑定关断该单元内的一个或多个栅极。就此而言,图10A示出了包括多个栅极1012、1014、1016、1018、1020、1022和1024、源极(标记为“S”)和漏极(标记为“D”)的示例性单元1010的俯视图。在该示例中,每个源极位于相应的栅极对之间,并且每个漏极位于相应的栅极对之间。单元1010还包括漏极触点1026、1030、1032和1036,其中每个漏极触点被设置在漏极的相应一者上。单元1010还包括源极触点1028和1034,其中每个源极触点被设置在源极的相应一者上。该单元进一步包括电源轨1060以及分别将源极触点1028和1034耦合至电源轨1060的通孔1040和1042。

单元1010包括栅极绑定关断结构,该栅极绑定关断结构包括金属互连1050,该金属互连1050可由与电源轨1060相同的金属层或不同的金属层形成。金属互连1050位于栅极1016和1018、漏极触点1030和源极触点1028上方。注意,以虚线示出了金属互连1050下方的结构。在图10A中的示例中,金属互连1050在横向方向1062上部分地跨单元1010延伸。

栅极绑定关断结构还包括设置在栅极1018与金属互连1050之间的栅极触点1054、以及设置在源极触点1028与金属互连1050之间的通孔1052。在该示例中,栅极触点1054将栅极1018耦合至金属互连1050,并且通孔1052将源极触点1028耦合至金属互连1050。因此,栅极1018通过栅极触点1054、金属互连1050和通孔1052来电耦合至源极触点1028(以及因此相应源极)。因此,在该示例中,栅极1018是通过金属互连1050来电耦合(绑定)至单元1010的源极之一以在栅极1018的相对侧上的各晶体管之间提供电隔离的虚设栅极。

图10B示出了示例性栅极绑定关断结构的侧视图。如图10B中所示,金属互连1050在漏极触点1030上方通过(穿过),并且在纵向方向1066上与漏极触点1030分隔开一空间。类似地,金属互连1050在栅极1016上方通过(穿过),并且在纵向方向1066上与栅极1016分隔开一空间。这允许金属互连1050在漏极触点1030和栅极1016上方穿过以将栅极1018耦合至源极触点1028,而不会使金属互连1050与漏极触点1030和栅极1016短路。漏极触点1030与金属互连1050之间的纵向空间允许漏极触点1030在横向方向1064上在金属互连1050下方延伸,如图10A中所示。

在图10B所示的示例中,源极和漏极被描绘为用于平面晶体管的芯片(管芯)的基板中的掺杂区。然而,应领会,对于finFET的示例,源极和漏极可由在横向方向1062上跨单元1010延伸的多个鳍形成。就此而言,图11示出了单元1010的一部分的立体图,其中单元1010包括在横向方向1062上跨单元1010延伸的多个鳍1110。在该示例中,在鳍1110的相应部分上形成栅极1016和1018中的每一者,其中薄介电层(未示出)被设置在栅极与鳍1110之间。因此,在该示例中,鳍连续地通过栅极延伸。漏极触点1030被设置在鳍1110的形成相应漏极的一部分上,并且源极触点1028被设置在鳍1110的形成相应源极的一部分上。

如图11中所示,金属互连1050与漏极触点1030之间在纵向方向1066上的纵向空间(间隙)允许漏极触点1030在横向方向1064上在金属互连1050下方延伸。漏极触点1030在横向方向1064上的延伸允许漏极触点1030为了较低的漏极接触电阻而与所有鳍1110电接触。漏极触点1030与金属互连1050之间的空间(间隙)可被填充有电隔离材料。

尽管图11示出了其中单元1010包括三个鳍的示例,但是应领会,单元1010可包括不同数目的鳍。此外,尽管图11示出了其中每个鳍具有矩形横截面的示例,但是应领会,每个鳍可具有另一横截面形状(例如,锥形形状)。

应领会,鳍1110可被用于以上讨论的任何实施例中,其中鳍可跨一个或多个单元延伸。对于其中两个单元彼此邻接的示例,鳍可以连续地通过位于这些单元的邻接处的栅极(例如,栅极440、栅极540或栅极640)延伸。在该情形中,在邻接处的栅极可被绑定关断,以在两个单元之间提供电隔离而不切割(破坏)栅极下方的鳍。

应领会,单元1010除了图10A和10B中示出的示例性栅极绑定关断结构之外还可包括一个或多个附加的栅极绑定关断结构(未示出)。在该情形中,该一个或多个附加的栅极绑定关断结构以及图10A和10B中示出的示例性栅极绑定关断结构可共享在横向方向1062上跨单元1010延伸的共用金属互连。

就此而言,图12A示出了包括跨单元1210延伸的金属互连1250的示例性单元1210的俯视图。单元1210类似于图10A中的单元1010,其中对于单元1010和1210两者而言共用的元件由相同的附图标记来标识。

图12A中的金属互连1250和图10A中示出的金属互连1050的不同之处在于,金属互连1250跨单元1210延伸。金属互连1250可由与电源轨1060相同的金属层或不同的金属层形成。金属互连1250位于栅极1012、1014、1016、1018、1020、1022和1024、漏极触点1026、1030、1032和1036、以及源极触点1028和1034上方。注意,以虚线示出了金属互连1250下方的结构。

如图12A中所示,类似于图10A中的单元1010,栅极触点1054将栅极1018耦合至金属互连1250,并且通孔1052将源极触点1028耦合至金属互连1250。单元1250还包括设置在栅极1012与金属互连1250之间的栅极触点1252、以及耦合在栅极1024与金属互连1250之间的栅极触点1254。栅极触点1252将栅极1012耦合至金属互连1250,并且栅极触点1254将栅极1024耦合至金属互连1250。因此,栅极1012通过金属互连1250来耦合至源极触点1028(以及因此相应源极),并且栅极1024通过金属互连1250来耦合至源极触点1028(以及因此相应源极)。由于栅极1012和1024位于单元1250的边界上,因此将栅极1012和1024通过金属互连1250电耦合至源极为单元1210中的晶体管提供与其他单元(未示出)的电隔离。

图12B示出了单元1210的侧视图。如图12B中所示,金属互连1250在漏极触点1026、1030、1032和1036上方通过(穿过),并且在纵向方向1066上与漏极触点分隔开一空间。这允许金属互连1250在漏极触点上方穿过而不会使金属互连1250与漏极触点短路。此外,在该示例中,金属互连1250在栅极1014、1016、1020和1022上方通过(穿过),并且在纵向方向1066上与这些栅极分隔开一空间。这允许金属互连1250在这些栅极上方穿过而不会使金属互连1250与这些栅极短路。

在图12A和12B所示的示例中,单元1210还包括将源极触点1034耦合至金属互连1250的通孔1256。因此,在该示例中,栅极1018通过金属互连1250来耦合至两个源极,其中栅极1018位于这两个源极之间。

在图12A所示的示例中,单元1210包括在横向方向1062上跨单元1210延伸的连续有源区1260(在图12A中表示为阴影区域)。在该示例中,栅极1014、1016、1018、1020和1022中的每个栅极、每个源极、以及每个漏极中的至少一部分处于连续有源区1260内。对于FinFET工艺,连续有源区1260包括在横向方向1062上跨单元1210延伸的鳍。在该示例中,鳍连续地通过栅极1014、1016、1018、1020和1022延伸,而未对鳍进行切割(破坏)。

以上讨论的示例性单元可在标准单元库中被预定义,该标准单元库定义了可被放置在某个半导体处理器的芯片(管芯)上的各种单元。对于单元库中的每个单元,单元库可定义单元中的各晶体管的布局、用于将单元中的各晶体管互连的互连结构、和/或用于单元的栅极绑定关断结构。单元库中的单元的多个实例可被放置在芯片(管芯)上。

在某些方面,单元库中的每个单元可被配置成执行相应的逻辑功能。在这些方面,电路的功能可在设计阶段被分解成多个逻辑功能,其中每个逻辑功能可由单元库中的单元之一执行。执行逻辑功能的各单元可随后被放置在芯片上并且被互连以在芯片上实现电路。单元可通过BEOL中的上层金属层来互连。因此,在该示例中,单元被用作电路的构建块。

用于芯片上的单元的布局参数可包括定义单元中针对由特定金属层(例如,BEOL的最底部金属层)形成的金属线的可用路径的轨道。就此而言,图13A解说了根据本公开的某些方面的用于示例性单元1310的多条轨道。在图13A中,轨道被标记为T0至T7,并且由在横向方向1330上跨单元1310延伸的多条线来表示。轨道平行于彼此延伸并且在横向方向1340上间隔开,其中横向方向1340大致垂直于横向方向1330。如本文所使用的,术语“大致垂直”指示两个方向之间的角度处于85度与95度之间。应领会,单元1310不限于图13A中所示的示例性数目的轨道,并且单元1310可具有不同数目的轨道。

轨道定义了单元1310中针对由特定金属层(例如,BEOL的最底部金属层)形成的金属线的可用路径。换言之,轨道定义了由金属层形成的金属线可被放置在单元上的何处。在该示例中,金属互连可被放置在轨道之一上,以绑定关断单元1310中的一个或多个栅极,并且电源轨可被放置在轨道的不同的一者上。另外,用于信号路由的金属线可被放置在与用于金属互连和电源轨的轨道不同的一条或多条轨道上。例如,这些金属线可被用于向或从单元中的(诸)漏极路由信号,和/或向或从单元中的(诸)栅极路由信号。

图13B示出了用于位于芯片上的同一行中的多个单元1310至1330的多条轨道(标记为T0至T7)的示例,其中单元1310至1330的边界在图13B中由虚线来指示。在该示例中,单元1320毗邻于单元1310和1310,并且位于单元1310与1330之间。

如图13B中所示,单元1310至1330具有相同数目的轨道以及相同的高度(标记为“H”)。在该示例中,图13B中示出的轨道(标记为T0和T7)表示用于将由相同金属层(例如,BEOL中的最底部金属层)形成的金属线放置在单元1310至1330中的可用路径。单元1310至单元1330可各自包括用于栅极绑定关断的金属互连(图13B中未示出),其中单元1310至1330的金属互连被放置在相同的轨道上。因此,在该示例中,单元1310至1330的金属互连沿着横向方向1330延伸,并且由于它们位于相同轨道上而在横向方向1340上彼此对准。一般而言,位于相同轨道上的金属线在横向方向1340上彼此对准。单元1310至1330的金属互连可被组合成跨单元1310至1330延伸的一个连续的金属互连,或者可以是在横向方向1330上由间隙间隔开的分开的金属互连。

图13B中的单元1310至1330中的每一者可以是图3A、3B、4A、4B、5A、5B、6A、6B、7A、7B、8A、8B、9A、9B、10A和10B中示出的示例性单元中的任一者的实例(即,副本),其中横向方向1330对应于横向方向340、460、560、660和1062,并且横向方向1340对应于横向方向342、465、565、665和1066。单元1310至1330中的两者或更多者可以各自是以上附图之一中示出的相同单元的单独实例。

如以上所讨论的,以上讨论的示例性金属互连中的任一者可由芯片的BEOL中的最底部金属层(例如,使用光刻和蚀刻工艺)形成。最底部金属层可取决于BEOL中的金属层的指定是在M0还是M1处开始而被称为金属层M0或金属层M1。

尽管图3B、4B、5B、6B、7B、8B、9B和10B示出了其中栅极触点被直接耦合至金属互连的示例,但是应领会,本公开不限于该示例。例如,这些栅极触点中的每一者可通过设置在栅极触点与相应金属互连之间的相应通孔来耦合至金属互连。

在本公开内,措辞“示例性”用于意指“用作示例、实例、或解说”。本文中描述为“示例性”的任何实现或方面不必被解释为优于或胜过本公开的其他方面。同样,术语“方面”不要求本公开的所有方面都包括所讨论的特征、优点或操作模式。术语“耦合”在本文中用于指代两个组件之间的直接或间接耦合。

本文中使用诸如“第一”、“第二”等指定对元素的任何引述一般并不限定那些元素的数量或次序。确切而言,这些指定在本文中用作区别两个或更多个元素或者元素实例的便捷方式。由此,对第一元素和第二元素的引述并不意味着仅能采用两个元素、或者第一元素必须位于第二元素之前。

将领会,本公开不限于以上用于描述本公开的各方面的术语。例如,有源区也可被称为扩散区或另一术语。在另一示例中,电源轨也可被称为电网或另一术语。

提供对本公开的先前描述是为使得本领域任何技术人员皆能够制作或使用本公开。对本公开的各种修改对本领域技术人员而言将容易是显而易见的,并且本文中所定义的普适原理可被应用到其他变型而不会脱离本公开的精神或范围。由此,本公开并非旨在被限定于本文中所描述的示例,而是应被授予与本文中所公开的原理和新颖特征相一致的最广范围。

- 用于栅极绑定关断的新颖标准单元架构

- 用于栅极绑定关断的新颖标准单元架构