供电系统及电子设备

文献发布时间:2023-06-19 19:23:34

技术领域

本公开涉及电力电子技术领域,特别涉及一种供电系统及电子设备。

背景技术

数据处理的核心在于各个种类的处理器芯片,例如中央处理单元(CPU)、图形处理单元(GPU)、现场可编程门阵列(FPGA)以及大规模定制化处理器(ASIC),供电系统对于处理器芯片的性能极为重要,其中稳定的供电电压可有效提升处理器芯片的性能,因此供电予处理器芯片的功率单元的稳态及动态性能十分重要。于供电系统中,功率单元与处理器芯片之间的连接阻抗较大,因此直接影响了功率单元供电予处理器芯片的供电性能,造成处理器芯片的性能亦较差,进而使得整体供电系统的供电性能较差。

因此,实有必要发展一种供电系统,以解决现有技术所面临的问题。

发明内容

本公开的目的为提供一种供电系统及电子设备,其具有供电效能较佳的优势。

为达上述目的,本公开的一实施方式为提供一种供电系统,用以供电给负载,供电系统包含系统板、基板、至少一输出电容、至少一正输出导接区、至少一负输出导接区及至少一功率单元。系统板包含相对设置的第一面及第二面,负载设置于第一面上。基板包含相对设置的第一面及第二面,基板的第一面位于系统板的第二面及基板的第二面之间。至少一输出电容表贴于系统板的第二面。至少一正输出导接区设置于基板的第一面,且连接于系统板的第二面,并经由系统板内的布线与输出电容的一端电性连接。至少一负输出导接区设置于基板的第一面,且连接于系统板的第二面,并经由系统板内的布线与输出电容的另一端电性连接。至少一功率单元设置于基板的第二面,且经由基板内的布线与至少一正输出导接区及至少一负输出导接区电性连接。

本公开的另一实施方式为提供一种电子设备,该电子设备包含负载和前述的供电系统,供电系统用以供电给负载。

附图说明

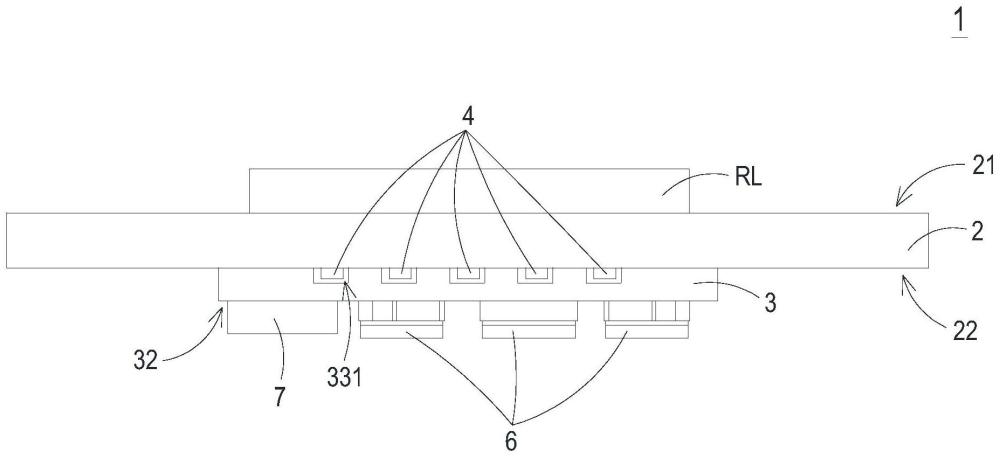

图1为本公开第一实施例的供电系统的剖面结构示意图。

图2为图1所示的供电系统的分解结构示意图。

图3A及图3B为图1所示的供电系统的基板的两个不同视角的结构示意图。

图3C为图1所示的供电系统的基板的另一实施例的结构示意图。

图3D为图1所示的供电系统的基板的另一实施例的结构示意图。

图3E为图1所示的供电系统的基板的另一实施例的结构示意图。

图3F为图1所示的供电系统的基板的另一实施例的结构示意图。

图3G为图1所示的供电系统的基板的另一实施例的结构示意图。

图4为图1所示的供电系统的等效电路图。

图5为图1所示的供电系统的基板及设置于基板上的电子元件的结构示意图。

图6为图1所示的供电系统的基板的另一实施例的结构示意图。

图7为图1所示的供电系统的基板的第二面的结构上视图。

图8为图1所示的供电系统示出连接孔的剖面结构示意图。

图9为本公开第二实施例的供电系统的剖面结构示意图。

图10为本公开第三实施例的供电系统的剖面结构示意图。

图11为图10所示的供电系统的分解结构示意图。

图12为本公开第四实施例的供电系统的剖面结构示意图。

图13为图1所示的供电系统的各种导接区的另一实施例的设置位置示意图。

图14为图13所示的正输出导接区及相邻的输出电容的极性关系示意图。

图15为图13所示的正输出导接区及相邻的输出电容的另一实施例的极性关系示意图。

图16为本公开第五实施例的供电系统的基板的第二面的结构示意图。

图17为图16所示的供电系统的功率单元焊盘的第一种实施例的放大示意图。

图18为图16所示的供电系统的功率单元焊盘的第二种实施例的放大示意图。

图19为图16所示的供电系统的功率单元焊盘的第三种实施例的放大示意图。

附图标记:

1、1a、1b、1c:供电系统

Vin:输入电压

RL:负载

Cin:输入电容

Q1、Q2:开关元件

L:电感

Co:输出电容

Vin+:正输入端

Vin-:负输入端

Vout+:正输出端

Vout-:负输出端

2:系统板

21:系统板的第一面

22:系统板的第二面

3、3a、3’:基板

31:基板的第一面

32:基板的第二面

331:第一容置槽

331a:第二容置槽

331b:第三容置槽

331c:第四容置槽

332:连接孔

333:铜柱

334:导电结构

34:基板的第一侧壁

35:基板的第二侧壁

36:基板的第三侧壁

37:基板的第四侧壁

381:控制器焊盘

382:电容焊盘

39、39a:功率单元焊盘

391:信号引脚

392:输入端引脚

393:输出端引脚

394:接地引脚

395:功率单元焊盘的第一侧壁

396:功率单元焊盘的第二侧壁

397:功率单元焊盘的第三侧壁

398:功率单元焊盘的第四侧壁

O:中心点

4:输出电容

51:正输出导接区

511:子正输出导接区

52:负输出导接区

521:子负输出导接区

53:正输入导接区

531:子正输入导接区

54:负输入导接区

541:子负输入导接区

6:功率单元

601:功率单元的正输出引脚

602:功率单元的负输出引脚

61:第一排列行

62:第二排列行

63:第三排列行

64:第四排列行

7:控制器

具体实施方式

体现本公开特征与优点的一些典型实施例将在后段的说明中详细叙述。应理解的是本公开能够在不同的实施方式上具有各种的变化,其皆不脱离本公开的范围,且其中的说明及附图在本质上当作说明之用,而非用于限制本公开。

请参阅图1至图4,其中图1为本公开第一实施例的供电系统的剖面结构示意图,图2为图1所示的供电系统的分解结构示意图,图3A及图3B为图1所示的供电系统的基板的两个不同视角的结构示意图,图4为图1所示的供电系统的等效电路图,图4仅示意性的给出了一个单相功率单元的供电电路,实际供电系统中的功率单元可能包含多个图4所示虚线框内的电路并联结构,以输出负载RL所需的功率,当然一个功率单元对应虚线框内的电路可以是两相甚至更多相并联,这里不做限制。本实施例的供电系统1用以接收并转换输入电压Vin以供电给负载RL,其中负载RL为处理器芯片,例如中央处理器(Central ProcessingUnit,CPU)、图形处理器(Graphics Processing Unit,GPU)、张量处理器(TensorProcessing Unit,TPU)、网络处理器(Network Processing Unit,NPU)、现场可程序化逻辑门阵列(Field Programmable Gate Array,FPGA)或特定应用集成电路(ApplicationSpecific Integrated Circuit,ASIC)。图1所示的供电系统1可包含一个或多个功率单元,可构成多个图4所示的电路结构,其中多个功率单元的输出端之间并联连接以共同供电给负载RL,而以下以单一的单相功率单元所构成的供电系统1进行说明,如图4所示,供电系统1包含输入电容Cin、两个开关元件Q1、Q2、电感L及输出电容Co,其中两个开关元件Q1、Q2及电感L构成供电系统1的功率单元6,以转换输入电压Vin所提供的电能,其中供电系统1的功率单元6可为BUCK电路或LLC电路。输入电容Cin连接于输入电压Vin以接收输入电压Vin所提供的电能,且输入电容Cin的两端分别连接供电系统1的正输入端Vin+及负输入端Vin-。两个开关元件Q1、Q2相互串联,且两个开关元件Q1、Q2串联所构成的电路支路与输入电容Cin并联连接。电感L的第一端连接于两个开关元件Q1、Q2的中点,电感L的第二端连接于输出电容Co。输出电容Co的两端分别连接供电系统1的正输出端Vout+及负输出端Vout-,且输出电容Co与负载RL并联连接。供电系统1的负输入端Vin-及负输出端Vout-之间短接。

如图1至图3B所示,本实施例的供电系统1的实体结构包含系统板2、基板3、多个输出电容4、多个正输出导接区51、多个负输出导接区52、多个正输入导接区53、多个负输入导接区54及多个功率单元6。首先,如图1及图2所示,系统板2包含第一面21及第二面22,系统板2的第一面21及第二面22相对设置,其中负载RL设置于系统板2的第一面21。如图2、图3A及图3B所示,基板3包含第一面31、第二面32、多个第一容置槽331、第一侧壁34、第二侧壁35、第三侧壁36及第四侧壁37,基板3的第一面31及第二面32相对设置,基板3的第一面31贴合于系统板2的第二面22,使基板3的第一面31位于系统板2的第二面22及基板3的第二面32之间,其中基板3于系统板2上的设置位置与负载RL于系统板2上的设置位置相互对应。多个第一容置槽331由基板3的第一面31内凹所构成,且于基板3的第一面31贴合于系统板2的第二面21时,每一第一容置槽331与系统板2的第二面22分别定义出为封闭状态的容置空间,其中每一第一容置槽331可为但不限为利用铣槽工艺加工制成。基板3的第一侧壁34、第二侧壁35、第三侧壁36及第四侧壁37皆位于基板3的第一面31及第二面32之间,其中第一侧壁34及第二侧壁35相对设置,第三侧壁36及第四侧壁37相对设置且位于第一侧壁34及第二侧壁35之间。

如图1所示,每一输出电容4用以构成如图4所示的对应的供电系统1中的输出电容Co,且输出电容4利用焊接工艺而表贴于系统板2的第二面22,且经由系统板2内的布线与负载RL电性连接,其中每一输出电容4容置于基板3上对应的第一容置槽331内,且每一第一容置槽331的体积大于对应的输出电容4的体积,而每一第一容置槽331的壁面与对应的输出电容4之间具有间隙,而使输出电容4不会接触于对应的第一容置槽331的壁面,以提升输出电容4装配于系统板2的安定性。

每一正输出导接区51用以构成图4所示的供电系统1中的正输出端Vout+,且按序排列设置于基板3的第一面31,且于基板3的第一面31贴合于系统板2的第二面22时连接于系统板2的第二面22,其中每一正输出导接区51的延伸方向相同于基板3的第一侧壁34朝向第二侧壁35的方向,且经由系统板2内的布线而与对应的输出电容4的一端电性连接,其中多个正输出导接区51之间经由基板3内的布线相互连接以构成供电系统1整体的正输出端Vout+。每一负输出导接区52用以构成图4所示的供电系统1中的负输出端Vout-,且按序排列设置于基板3的第一面31,且于基板3的第一面31贴合于系统板2的第二面22时连接于系统板2的第二面22,其中每一负输出导接区52的延伸方向相同于基板3的第一侧壁34朝向第二侧壁35的方向,且经由系统板2内的布线而与对应的输出电容4的另一端电性连接,其中多个负输出导接区52之间经由基板3内的布线相互连接以构成供电系统1整体的负输出端Vout-。如图3A及图3B所示,多个负输出导接区52与多个正输出导接区51之间相互交错设置,即代表每两个相邻的负输出导接区52之间具有对应的正输出导接区51,且每两个相邻的正输出导接区51之间具有对应的负输出导接区52。于本实施例中,每一第一容置槽331位于对应的正输出导接区51及对应的负输出导接区52之间,使得位于对应的第一容置槽331内的输出电容4位于对应的正输出导接区51及对应的负输出导接区52之间。

上述的实施例中,如图2所示,功率单元6包含至少一正输出引脚601及至少一负输出引脚602。功率单元6的正输出引脚601经由基板3内的布线与正输出导接区51电性连接,并经由该系统板2内的布线与输出电容Co的一端电性连接;功率单元6的负输出引脚602经由基板3内的布线与负输出导接区52电性连接,并经由系统板2内的布线与输出电容Co的另一端电性连接。

另一种可能的引脚排布形式,如图3C所示,由于正输出导接区51比负输出导接区52的电流大,因此正输出导接区51的尺寸会设置的更宽一些,或者设置成并列的两个正输出导接区51,依次形成正输出导接区51、正输出导接区51、负输出导接区52、正输出导接区51、正输出导接区51、负输出导接区52、正输出导接区51、正输出导接区51及负输出导接区52的排列形式,即代表每两个相邻的负输出导接区52之间具有对应的两个正输出导接区51。针对并列的正输出导接区51,可以是在一个很宽的正输出导接区51上通过一绿油条阻断,如图3c的虚线所示,也可以是设置成两个独立的正输出导接区51,如此设置有利于基板与系统板之间焊接过程的排气,降低空洞比例。

引脚的排布形式除了如图3C所示的排布形式外,也可以是其他排布形式,如图3D所示,每两个相邻的正输出导接区51之间具有对应的两个负输出导接区52,依次形成正输出导接区51、负输出导接区52、负输出导接区52、正输出导接区51、负输出导接区52及负输出导接区52的排列形式。在其它实施例中,两个相邻的正输出导接区51之间具有对应的的负输出导接区52,且负输出导接区52的数量可以为大于两个。如图3E所示,每两个相邻的第一容置槽331之间包含两个正输出导接区51或者两个负输出导接区52,依次形成正输出导接区51、正输出导接区51、负输出导接区52、负输出导接区52、正输出导接区51、正输出导接区51、负输出导接区52及负输出导接区52的排列形式。如图3F所示,每两个相邻的第一容置槽331之间包含多个正输出导接区51或者多个负输出导接区52。通过将大焊盘分割成小焊盘后,可以增加焊接过程的排气通路,使得焊接更加稳定,降低空洞率。值得说明的是,在该些实施例中,各处正输出导接区51和负输出导接区52的数量可以为其他值,例如多于两个。

系统板2用于与基板3连接的第二面22,其焊盘可以设置成与基板3的焊盘完全一致的结构形式,用于与负载RL连接的第一面21,其焊盘可以设置成与负载RL焊盘完全一致的结构形式。或者,为了满足电流从功率单元到负载之间更好的均流,系统板2的第二面22亦可以设置成与系统板2的第一面21相同的焊盘排布形式,即系统板2的第一面21、系统板2的第二面22以及基板3的第一面31的焊盘排布形式完全相同。根据实际的加工过程,基板3与系统板2之间的相对位置可能存在偏移,有效焊接面积需至少大于焊盘面积的50%,以保证焊接可靠性以及通流需求。

请继续参考图3D~3F,可以看出相邻于每一个输出电容4两侧的输出导接区的极性不同,沿着第一方向S1,每两个相邻的输出电容4之间包含两个输出导接区且两个输出导接区的电极性相同。如图3G所示,沿着第一方向S1,每两个相邻的输出电容4之间也可以包含三个输出导接区,其中相邻于该两个相邻的输出电容4的输出导接区的极性不同。如图3F所示,沿着第二方向S2,相邻输出电容4的同侧电极相同。该实施例通过设置多个输出导接区,使得通流能力大大提升,进一步提升功率模块6的供电效率。以图3F最左侧第一列电容为例,每一电容均包含两个端面,输出电容4的同侧是指沿着第二方向阵列的输出电容4的同一端面对应的侧面,例如图3F中输出电容4的左侧或右侧。值得说明的是,在该实施例中,第一方向S1为第一容置槽331的排布方向,例如横向,第二方向S2为第一容置槽331的延伸方向,例如纵向,第二方向S2垂直于第一方向S1。

每一正输入导接区53用以构成图4所示的供电系统1中的正输入端Vin+,如图2、图3A及图3B所示,本实施例的正输入导接区53的个数为两个,两个正输入导接区53设置于基板3的第一面31,且分别相邻于基板3的第一侧壁34及第二侧壁35,其中多个正输出导接区51及多个负输出导接区52分别位于两个正输入导接区53之间,其中两个正输入导接区53之间经由基板3内的布线相互连接以构成供电系统1整体的正输入端Vin+。

每一负输入导接区54用以构成图4所示的供电系统1中的负输入端Vin-,如图2、图3A及图3B所示,本实施例的负输入导接区54的个数为两个,两个负输入导接区54设置于基板3的第一面31,且分别相邻于基板3的第三侧壁36及第四侧壁37,其中多个正输出导接区51及多个负输出导接区52分别位于两个负输入导接区54之间,其中两个负输入导接区54之间经由基板3内的布线相互连接以构成供电系统1整体的负输入端Vin-。于一些实施例中,由于供电系统1的负输入端Vin-及供电系统1的负输出端Vout-之间短接,因此构成供电系统1的负输入端Vin-的负输入导接区54的设置位置及构成供电系统1的负输出端Vout-的负输出导接区52的设置位置可相互调换。于本实施例中,正输出导接区51、负输出导接区52、正输入导接区53、负输入导接区54可为但不限为由阻焊层定义焊盘(SolderMaskDefined,SMD)或非阻焊层定义焊盘(NonSolderMaskDefined,NSMD)的方式所构成。

如图1及图2所示,多个功率单元6设置于基板3的第二面32,每一功率单元6经由基板3内的布线而与对应的正输出导接区51、负输出导接区52、正输入导接区53及负输入导接区54电性连接。

由上可知,本实施例的供电系统1的输出电容4表贴于系统板2的第二面22,且负载RL设置于系统板2的第一面21,而使得输出电容4与负载RL之间的连接路径非常短,即输出电容4与负载RL之间的连接路径仅为系统板2内连接于输出电容4与负载RL之间的布线,而使输出电容4与负载RL之间的连接阻抗亦较低,进而提升了功率单元6的供电性能,因此本实施例的供电系统1的整体性能亦随之提升。此外,由于每一输出电容4设置于基板3上对应的第一容置槽331内,而输出电容4位于对应的正输出导接区51及对应的负输出导接区52之间,即代表图4所示的输出电容Co上的电流可平均流向正输出端Vout+及负输出端Vout-,使得构成正输出端Vout+的正输出导接区51及构成负输出端Vout-的负输出导接区52之间的均流效果十分显著。最后,由于输出电容Co均是采用常规的表贴工艺设置于系统板2上,工艺过程简单可靠。

请参阅图5并配合图2及图3A,其中图5为图1所示的供电系统的基板及设置于基板上的电子元件的结构示意图。于本实施例中,供电系统1还包含控制器7,设置于基板3的第二面32,且相邻于部分的功率单元6,更相邻于基板3的第一侧壁34与第三侧壁36的连接处,且控制器7经由基板3内的布线以与多个功率单元6电性连接,控制器7用以控制功率单元6内的开关元件(未图示)的运行状态。由上可知,本实施例的供电系统1的控制器7与功率单元6皆设置于基板3的第二面32上,因此控制器7与功率单元6之间不需要设置额外连接线,使得控制器7与功率单元6之间的连接阻抗大幅降低,亦降低了控制器7输出的控制信号传送至功率单元6的时间,进而维持供电系统1的输出电压的稳定性。且由于控制器7设置于基板3的第二面32上,而可减少系统板2上的电子元件的数量,使得系统板2的面积缩小。

请继续参阅图5,于本实施例中,功率单元6的数量为十二个,且十二个功率单元6的排列方式构成三个排列行,即第一排列行61、第二排列行62及第三排列行63,第一排列行61、第二排列行62及第三排列行63依序排列设置,且第一排列行61、第二排列行62及第三排列行63之间的排列方向相同于基板3的第四侧壁37朝向第三侧壁36的方向,且第一排列行61、第二排列行62及第三排列行63中的每一排列行皆包含四个功率单元6。

于一些实施例中,功率单元6可将图4所示的两个开关元件Q1、Q2及电感L封装为单一结构,同时可以将供电系统中的一部分输入电容Cin集成于该单一结构,另一部分输入电容Cin设置于基板的第二面。多个输入电容Cin设置于基板3的第二面32上,且依序排列设置于基板3的第一侧壁34及第二侧壁35之间,且多个输入电容Cin与多个功率单元6交错设置。由上可知,本实施例的供电系统1的功率单元6及输入电容Cin皆设置于基板3的第二面32上,因此功率单元6及输入电容Cin之间不需要设置额外连接线,使得功率单元6及输入电容Cin之间的连接阻抗大幅降低,而输入电容Cin上的电压不易衰减,且电能的电压波动经由输入电容Cin滤波后不易对功率单元6造成影响,因此功率单元6的输入电压较为稳定,且由于输入电容Cin设置于基板3的第二面32上,而可减少系统板2上的电子元件的数量,进一步缩小系统板2的面积。而在另一些实施例中,为了减少功率单元6的体积,可将全部的输入电容Cin设置于基板的第二面,仅将图4所示的两个开关元件Q1、Q2及电感L封装为一体成型的单一结构,而不再在功率单元6内部集成输入电容Cin。

于一些实施例中,为了提升功率单元6的供电性能,输出电容4的数量需大幅增加,而基板的容置槽的数量亦须随之提升,以容置对应数量的输出电容4。请参阅图6并配合图1,其中图6为图1所示的供电系统的基板的另一实施例的结构示意图。如图6所示,本实施例的基板3a除了包含第一容置槽331外,还包含多个第二容置槽331a、多个第三容置槽331b及多个第四容置槽331c。多个第二容置槽331a由基板3a的第一面31内凹所构成,且贯穿于基板3a的第三侧壁36及第四侧壁37,其中部分的第二容置槽331a位于正输出导接区51及正输入导接区53之间,另外部分的第二容置槽331a位于负输出导接区52及正输入导接区53之间,其中多个第二容置槽331a用以容置额外增加的输出电容4。

多个第三容置槽331b由基板3a的第一面31内凹所构成,且贯穿于基板3a的第三侧壁36及第四侧壁37,其中部分的第三容置槽331b将正输出导接区51区分为多个子正输出导接区511,例如两个,每一正输出导接区51的两个子正输出导接区511依序排列且间隔设置,两个子正输出导接区511的排列方向相同于基板3的第一侧壁34朝向第二侧壁35的方向。另外部分的第三容置槽331b将负输出导接区52区分为多个子负输出导接区521,例如两个,每一负输出导接区52的两个子负输出导接区521依序排列且间隔设置,两个子负输出导接区521的排列方向相同于基板3的第一侧壁34朝向第二侧壁35的方向,其中多个第三容置槽331b用以容置额外增加的输出电容4。另外部分的第三容置槽331b将负输入导接区54区分为多个子负输入导接区541,例如两个,每一负输入导接区54的两个子负输入导接区541依序排列且间隔设置,两个子负输入导接区541的排列方向相同于基板3的第一侧壁34朝向第二侧壁35的方向,其中多个第三容置槽331b用以容置额外增加的输出电容4。

多个第四容置槽331c由基板3a的第一面31内凹所构成,每一第四容置槽331c与对应的第一容置槽331相连通,其中第四容置槽331c将正输入导接区53区分为多个子正输入导接区531,例如四个,每一正输入导接区53的四个子正输入导接区531依序排列且间隔设置,四个子正输入导接区531的排列方向相同于基板3的第三侧壁36朝向第四侧壁37的方向,其中多个第四容置槽331c用以容置额外增加的输出电容4。

请参阅图7并配合图1及图2,其中图7为图1所示的供电系统的基板的第二面的结构上视图。如图7所示,基板3的第二面32上包含控制器焊盘381、多个输入电容焊盘382及多个功率单元焊盘39。控制器焊盘381相邻于基板3的第一侧壁34及第三侧壁36的连接处,用以供控制器7以例如焊接方式进行设置,以使控制器7设置于第二面32上并经由控制器焊盘381与基板3电性耦接,且控制器7所输出的控制信号可经由控制器焊盘381传递至基板3内的布线。

基板3上的多个功率单元焊盘39构成三个排列行,且基板3上的多个功率单元焊盘39所构成的三个排列行的设置位置对应于功率单元6设置于基板3上的三个排列行的设置位置,故于图7中亦以第一排列行61、第二排列行62及第三排列行63代表基板3上的多个功率单元焊盘39所构成的三个排列行,且于此不再赘述三个排列行的设置方式。每一功率单元焊盘39用以供对应的功率单元6以例如焊接方式进行设置,以使功率单元6设置于第二面32上并经由对应的功率单元焊盘39而与基板3电性耦接,且功率单元6所输出的电能可经由功率单元焊盘39传递至基板3内的布线。

于本实施例中,每一功率单元焊盘39包含多个信号引脚391,每一信号引脚391经由基板3内的布线与控制器7电性耦接,其中当功率单元6设置于对应的功率单元焊盘39上时,控制器7所输出的控制信号经由对应的信号引脚391传递至功率单元6,其中每一功率单元焊盘39的多个信号引脚391设置于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,以图7为例,基板3的中心点O预设为基板3上的多个功率单元焊盘39所构成的三个排列行的中心位置,且于本实施例中,基板3的中心点O位于第二排列行62的第二个功率单元6及第三个功率单元6之间的位置,而第一排列行61中的四个功率单元焊盘39的信号引脚391皆位于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,即功率单元焊盘39的四个侧边中相邻于基板3的第四侧壁37的一侧边。第二排列行62中相邻于基板3的第一侧壁34的两个功率单元焊盘39的信号引脚391皆位于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,即功率单元焊盘39的四个侧边中相邻于基板3的第一侧壁34的一侧边。第二排列行62中相邻于基板3的第二侧壁35的两个功率单元焊盘39的信号引脚391皆位于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,即功率单元焊盘39的四个侧边中相邻于基板3的第二侧壁35的一侧边。第三排列行63中的四个功率单元焊盘39的信号引脚391皆位于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,即功率单元焊盘39的四个侧边中相邻于基板3的第三侧壁36的一侧,而上述功率单元焊盘39的信号引脚391的设置位置可使得基板3内的布线排列方式更加灵活。

当然,每一功率单元焊盘39还包含更多种类的引脚,例如输入端引脚392、输出端引脚393及接地引脚394等,其中信号引脚391、输入端引脚392、输出端引脚393及接地引脚394可为但不限为由阻焊层定义焊盘(SolderMaskDefined,SMD)或非阻焊层定义焊盘(NonSolderMaskDefined,NSMD)的方式所构成。而输入端引脚392、输出端引脚393及接地引脚394的设置方式将于后详细叙述。

多个输入电容焊盘382以四个排列行的方式依序排列于基板3的第三侧壁36及第四侧壁37之间,且多个输入电容焊盘381所构成的四个排列行与多个功率单元焊盘39所构成的三个排列行相互交错设置,即多个输入电容焊盘381中每两个相邻的排列行之间具有对应的功率单元焊盘39所构成的一个排列行。其中位于每一排列行的多个输入电容焊盘382依序排列,且设置方向相同于基板3的第一侧壁34朝向第二侧壁35的方向,其中每一输入电容焊盘382与对应的输入电容Cin相接触,以使输入电容Cin经由对应的输入电容焊盘382而与基板3电性耦接,以进行基板3与输入电容Cin之间的电能传递。

于一些实施例中,位于基板3的第一面31的各种导接区以及位于基板3的第二面32的功率单元焊盘39的各种引脚之间的相互连接可以多种方式实现,例如于基板3中设置连接孔以进行电性连接。请参阅图8并配合图1、图2及图7,其中图8为图1所示的供电系统示出连接孔的剖面结构示意图。如图8所示,基板3还包含多个连接孔332,每一连接孔332贯穿于基板3的第一面31及第二面32,且每一连接孔332可为具有导电功能的通孔结构或盲埋孔结构,连接孔332的一端的设置位置对应于功率单元焊盘39的输入端引脚392、输出端引脚393或接地引脚394,连接孔332的另一端的设置位置对应于正输入导接区53、正输出导接区51、负输出导接区52或负输入导接区54,其中每一功率单元焊盘39的输入端引脚392经由对应的连接孔332连接于正输入导接区53,而功率单元6的正输入端经由基板3上的功率单元焊盘39的输入端引脚392、对应的连接孔332及正输入导接区53接收来自系统板2的电能。每一功率单元焊盘39的输出端引脚393经由对应的连接孔332连接于正输出导接区51,而功率单元6的正输出端电能经由基板3上的功率单元焊盘39的输出端引脚393、对应的连接孔332及正输出导接区51而传递至系统板2。每一功率单元焊盘39的接地引脚394经由对应的连接孔332连接于负输出导接区52或负输入导接区54,而功率单元6的负输出端电能经由基板3上的功率单元焊盘39的接地引脚394、对应的连接孔332及负输出导接区52而传递至系统板2,功率单元6的负输入端电能经由基板3上的功率单元焊盘39的接地引脚394、对应的连接孔332及负输入导接区54而传递至系统板2。其中图8仅以输出端引脚393经由对应的连接孔332连接于正输出导接区51,以及功率单元焊盘39的接地引脚394经由对应的连接孔332连接于负输出导接区52进行示例,而输入端引脚392经由对应的连接孔332连接于正输入导接区53,以及接地引脚394经由对应的连接孔332连接于负输入导接区54亦可以相似的方式连接,而不再赘述。由上可知,由于基板3位于功率单元6及系统板2之间,系统板2上的所接收的输入电能可直接经由基板3内的连接孔332而传送至功率单元6,而功率单元6将输入电能转换后再经由基板3内的连接孔332而传送至系统板2,且由于输出电容4直接表贴于系统板2的第二面22,因此系统板2所接收的转换电能可再直接经由系统板2内的布线而传送至输出电容4及负载RL,故可知,本公开的供电系统1的设置方式使得输出电容4及负载RL之间的连接路径较短,而大幅降低了输出电容4及负载RL之间的传输阻抗。

为了避免基板3的第一面31在利用铣槽工艺设置第一容置槽331时造成基板3的弯曲,影响了基板3与系统板2之间的焊接,于一些实施例中,可以对还未设置第一容置槽331的原始基板(以下称原始基板3)进行优化,例如提升原始基板3内相邻于原始基板3的第一面31的布线层密度,且降低原始基板3内相邻于原始基板3的第二面32的布线层密度,使得邻近于原始基板3的四个侧壁的部分原始基板3的应力较小,且邻近于原始基板3的中心位置的另外部分原始基板3的应力较大,造成原始基板3的预先弯曲,而当原始基板3的第一面31利用铣槽工艺设置第一容置槽331而构成基板3时,基板3的中心位置的应力可获得释放,以确保基板3的平整度。而于另一些实施例中,当基板3的第一面31利用铣槽工艺设置第一容置槽331时,基板3的第二面32亦同步利用铣槽工艺或钻孔方式设置额外的槽体,而使得基板3的第一面31及第二面32的应力释放程度相同,以确保基板3的平整度。

请参阅图9,其为本公开第二实施例的供电系统的剖面结构示意图。本实施例的供电系统1a相似于图1所示的供电系统1,而相较于图1所示的供电系统1利用连接孔连通于导接区与功率单元焊盘39所对应的引脚之间,本实施例的供电系统1a包含多个铜柱333,每一铜柱333内埋于基板3内,铜柱333的一端的设置位置对应于功率单元焊盘39的输入端引脚392、输出端引脚393或接地引脚394,铜柱333的另一端的设置位置对应于正输入导接区53、正输出导接区51、负输出导接区52或负输入导接区54,其中每一功率单元焊盘39的输入端引脚392经由对应的铜柱333连接于正输入导接区53,每一功率单元焊盘39的输出端引脚393经由对应的铜柱333连接于正输出导接区51,每一功率单元焊盘39的接地引脚394经由对应的铜柱333连接于负输出导接区52或负输入导接区54。因此本实施例的供电系统1a可达到基板3的第一面31上对应的导接区与基板3的第二面32上功率单元焊盘39所对应的引脚之间的通流需求,而当基板3的第一面31上对应的导接区与基板3的第二面32上功率单元焊盘39所对应的引脚之间的电流较大时,铜柱333所能达到的有效导通面积较大,而使得电流传输的稳定性较高,此外,由于基板3位于系统板2及功率单元6之间,因此功率单元6所产生的热能可经由基板3内的铜柱333导通至系统板2,并经由系统板2上的散热器(未图示)进行散热。

请参阅图10及图11,其中图10为本公开第三实施例的供电系统的剖面结构示意图,图11为图10所示的供电系统的分解结构示意图。本实施例的供电系统1b相似于图1所示的供电系统1,而相较于图1所示的供电系统1的基板3的第一面31直接贴合于系统板2的第二面22,且利用铣槽方式于基板3的第一面31上形成第一容置槽331,本实施例的供电系统1b的基板3的第一面31与系统板2的第二面22相间隔,且供电系统1b还包含多个导电结构334,每一导电结构334由导电柱所构成,每一导电结构334可为一体成型的结构或多个元件组成的分段式结构,每一导电结构334的一端连接于系统板2的第二面22,每一导电结构334的另一端连接于基板3的第一面31上的正输出导接区51、负输出导接区52、正输入导接区53或负输入导接区54中对应的导接区。此外,每一导电结构334、相邻的另一导电结构334、基板3的第一面31及系统板2的第二面22之间共同定义出第一容置槽331,每一第一容置槽331用以容置对应的输出电容4。于一些实施例中,每一导电结构334上用以焊接的两端可为波浪状表面,以达到排出气体的效果,当然,导电结构334的形成方式及设置位置并不局限,于此不再赘述。由上可知,由于输出电容4位于基板3及系统板2之间,且输出电容4直接表贴于系统板2的第二面22,因此功率单元6所传送的电能依序经由基板3及导电结构334以传递至系统板2,并经由系统板2内的布线而传送至输出电容4及负载RL。

于一些实施例中,导电结构334不仅可以导电柱的结构构成,还可以锡球的结构构成,且其形成方式可为球栅阵列封装(Ball Grid Array,BGA),如图12所示,图12为本公开第四实施例的供电系统的剖面结构示意图。且为了避免锡球可能出现的塌陷问题,可使用高温核心的锡球构成导电结构334,例如铜芯或高熔点焊料芯。而于一些实施例中,为了同时兼顾锡球的塌陷问题及成本考量,则于基板3的第一面31上的四个边角处设置高温核心的锡球,基板3的第一面31上的其余位置则设置常规的锡球,以利用基板3的四个边角处的锡球控制基板3的其余位置的锡球的塌陷,进而提升本实施例的供电系统1c的工艺良率。此外,由于前一实施例的供电系统1b及本实施例的供电系统1c直接设置导电结构334连接基板3及系统板2,而不需对基板3进行额外工艺,因此前一实施例的供电系统1b及本实施例的供电系统1c的平整性较高。

于一些实施例中,多个正输出导接区51及多个负输出导接区52设置于基板3的第一面31上的位置并不仅局限于图2、图3A所示的设置位置,而可根据需求进行调整。请参阅图13及图14,其中图13为图1所示的供电系统的各种导接区的另一实施例的设置位置示意图,图14为图13所示的正输出导接区及相邻的输出电容的极性关系示意图。如图13所示,本实施例的基板3b的多个正输出导接区51及多个负输出导接区52相互交错设置,且每两个正输出导接区51之间具有对应的一个负输出导接区52,每两个负输出导接区52之间具有对应的一个正输出导接区51,其中每一输出电容4设置于相邻的两个导接区之间,例如对应的正输出导接区51及对应的负输出导接区52之间。如图13所示,在本实施例中,与输出电容4连接的正输出导接区51和负输出导接区52沿着第一方向S1交错排列,沿着第二方向S2亦交错排列,第二方向S2垂直于第一方向S1。电流从正输出导接区51流经输出电容4到负输出导接区52形成输出回路,沿着第一方向,相邻输出回路的电流方向相反,使得该相邻输出回路的寄生电感部分抵消,供电系统的效率有进一步提升;沿着第二方向,相邻输出回路的电流方向亦相反,使得该相邻输出回路的寄生电感亦部分抵消,供电系统的效率有进一步提升。

图14中以正输出导接区51与相邻的输出电容4为例以示出输出电容4的引脚的极性,图14中输出电容4上的一个引脚以Vo标示,代表其与正输出端Vout+电性连接,图14中输出电容4上的另一个引脚以GND标示,代表其与负输出端Vout-电性连接,如图14所示,根据图13的设置方式,每一输出电容4的两个引脚中相邻于正输出导接区51的引脚的极性相同于正输出导接区51的极性,当然,负输出导接区52与相邻的输出电容4的引脚的极性亦相似于图14,即每一输出电容4的两个引脚中相邻于负输出导接区52的引脚的极性相同于负输出导接区52的极性,于此不再赘述。而由于上述的输出电容4的引脚的极性特性,因此若与正输出导接区51相连接的导电结构以及与负输出导接区52相连接的导电结构因意外发生相互连接的情况,亦不会产生短路。于本实施例中,每一正输出导接区51的形状及每一负输出导接区52的形状分别为圆形,而使得正输出导接区51及负输出导接区52于基板3的第一面31上所占的面积较小,故于基板3的第一面31的面积固定的前提下,可增加输出电容4的数量,又由于多个输出电容4之间并联连接,因此数量上升的输出电容4的等效串联电阻下降,使得供电系统的输出电压的稳定性提高。

而于另一些实施例中,每一正输出导接区51的形状不仅局限于图14所示的圆形,如图15所示,其中图15为图13所示的正输出导接区及相邻的输出电容的另一实施例的极性关系示意图。如图15所示,每一正输出导接区51的形状分别为正方形,相较于为圆形的正输出导接区51,每一正输出导接区51的面积得到提升,使得流经正输出导接区51的电流密度较小。当然,每一负输出导接区52的形状亦可为正方形,于此不再赘述。

于一些实施例中,基板3的第二面32上的控制器焊盘381、多个输入电容焊盘382及多个功率单元焊盘39不仅局限于图7所示的排列方式。请参阅图16及图17,其中图16为本公开第五实施例的供电系统的基板的第二面的结构示意图,图17为图16所示的供电系统的功率单元焊盘的第一种实施例的放大示意图。本实施例的基板3c的第二面32相似于图7所示的基板3的第二面32,而包含控制器焊盘381、多个输入电容焊盘382及多个功率单元焊盘39。相较于图7所示的多个功率单元焊盘39的设置位置构成三个排列行,本实施例的多个功率单元焊盘39的设置位置构成四个排列行,即第一排列行61、第二排列行62、第三排列行63及第四排列行64,当然,对应与多个功率单元焊盘39相连接的多个功率单元6亦以四个排列行的方式设置,于此不再赘述。

于本实施例中,每一功率单元焊盘39包含多个信号引脚391,其中每一功率单元焊盘39的多个信号引脚391设置于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,如图16所示,基板3的中心点O位于第二排列行62的第二个功率单元6、第二排列行62的第三个功率单元6、第三排列行63的第二个功率单元6及第三排列行63的第三个功率单元6之间的中心位置,而第一排列行61中的两个功率单元焊盘39的信号引脚391皆位于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,即功率单元焊盘39的四个侧边中相邻于基板3的第四侧壁37的一侧边。而第二排列行62中分别相邻于基板3的第一侧壁34及第二侧壁35的两个功率单元焊盘39的信号引脚391分别位于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,即分别位于功率单元焊盘39的四个侧壁中相邻于基板3的第一侧壁34的一侧边及第二侧壁35的一侧边。第二排列行62中相邻于基板3的中心点O的两个功率单元焊盘39的信号引脚391皆位于对应的功率单元焊盘39相邻于基板3的第四侧壁37的一侧边。第三排列行63中分别相邻于基板3的第一侧壁34及第二侧壁35的两个功率单元焊盘39的信号引脚391分别位于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,即分别位于对应的功率单元焊盘39的四个侧边中相邻于基板3的第一侧壁34的一侧及第二侧壁35的一侧边。第三排列行63中相邻于基板3的中心点O的两个功率单元焊盘39的信号引脚391皆位于对应的功率单元焊盘39相邻于基板3的第三侧壁36的一侧边。而第四排列行64中的两个功率单元焊盘39的信号引脚391皆位于对应的功率单元焊盘39的四个侧边中相对较远离于基板3的中心点O的一侧边,即位于对应的功率单元焊盘39的四个侧边中相邻于基板3的第三侧壁36的一侧边。

上述设置方式缩短了与功率单元焊盘39连接的功率单元6以及与控制器焊盘381连接的控制器7之间的路径距离,且减少了功率单元6的控制信号的信号延迟。且于本实施例中,每一输入电容焊盘382皆相邻于对应的功率单元焊盘39的信号引脚391,而使与输入电容焊盘382连接的输入电容Cin以及与功率单元焊盘39连接的功率单元6之间的路径距离缩小。此外,综合上述的焊盘设置方式,连接于基板3的第二面32的功率单元6以及连接于基板3的第一面31的负载RL的路径距离亦缩短,使得功率单元6与负载RL之间的阻抗降低,且提升了功率单元6的均流性。于本实施例中,每一功率单元6可为一相、两相或多相的BUCK电路,其中若功率单元6为多相电路,则可大幅提高每一功率单元6的功率密度,使得供电系统中的功率单元6的所需数量较低,即可提供负载RL所需的电能。

如图17所示,每一功率单元焊盘39具有第一侧壁395、第二侧壁396、第三侧壁397及第四侧壁398,其中功率单元焊盘39的第一侧壁395及第二侧壁396相对设置,功率单元焊盘39的第三侧壁397及第四侧壁398相对设置,且位于第一侧壁395及第二侧壁396之间。而每一功率单元焊盘39除了多个信号引脚391外,更具有多个输入端引脚392、多个输出端引脚393及多个接地引脚394。多个信号引脚391相邻于功率单元焊盘39的第一侧壁395且依序排列设置,多个输出端引脚393设置于功率单元焊盘39的中心位置,多个输入端引脚392及多个接地引脚394依序围绕多个输出端引脚393设置,其中多个输入端引脚392中的部分输入端引脚392相邻于功率单元焊盘39的第三侧壁397,多个输入端引脚392中的部分输入端引脚392相邻于功率单元焊盘39的第四侧壁398,多个输入端引脚392中的另外部分输入端引脚392位于信号引脚391及输出端引脚393之间,多个接地引脚394中的部分接地引脚394相邻于功率单元焊盘39的第三侧壁397,多个接地引脚394中的部分接地引脚394相邻于功率单元焊盘39的第二侧壁396,多个接地引脚394中的另外部分接地引脚394相邻于功率单元焊盘39的第四侧壁398。于本实施例中,与各种引脚所连接的基板3内的连接孔可为盲孔结构,以减小多个连接孔之间的间距,进而增加基板3内的连接孔的数量,以达到较高的电流流通能力。

而于另一些实施例中,功率单元焊盘上的各种引脚的设置位置并不仅局限于图17所示,请参阅图18,其为图16所示的供电系统的功率单元焊盘的第二种实施例的放大示意图。本实施例的功率单元焊盘39a的多个信号引脚391相邻于功率单元焊盘39的第一侧壁395且依序排列设置,多个接地引脚394相邻于功率单元焊盘39的第二侧壁396且依序排列设置,多个输入端引脚392依序排列设置且位于多个信号引脚391及多个输出端引脚393之间,多个输出端引脚393依序排列设置且位于多个输入端引脚392及多个接地引脚394之间。由于流经输出端引脚393的电流较大。于一些实施例中,为了电路的实际需求而增加输出端引脚393的设置范围,导致输出端引脚393的设置位置可能凸出于功率单元焊盘39的第三侧壁397及第四侧壁398,如图19所示,其为图16所示的供电系统的功率单元焊盘的第三种实施例的放大示意图。而为了对应连接凸出于功率单元焊盘39的第三侧壁397及第四侧壁398的输出端引脚393,基板3上可设置数量更多的连接孔332以连接凸出于功率单元焊盘39的第三侧壁397及第四侧壁398的输出端引脚393,而上述设置方式可达到较高的电流流通能力。

本公开的实施例还提供一种电子设备,该电子设备包含负载RL和前述各实施例的供电系统1、1a、1b和1c,供电系统1、1a、1b和1c用以供电给负载RL。

综上所述,本公开提供一种供电系统及电子设备,其中供电系统的输出电容表贴于系统板的第二面,且负载设置于系统板的第一面,而使得输出电容与负载之间的连接路径非常短,即输出电容与负载之间的连接路径仅为系统板内连接于输出电容与负载之间的布线,而使输出电容与负载之间的连接阻抗亦较低,进而提升了功率单元的供电性能,因此本公开的供电系统的整体性能亦随之提升。此外,由于每一输出电容设置于基板上对应的容置槽内,而输出电容位于对应的正输出导接区及对应的负输出导接区之间,即输出电容上的电流可平均流向正输出端及负输出端,使得构成正输出端的正输出导接区及构成负输出端的负输出导接区之间的均流效果十分显著。

- 可弯曲电子设备、可弯曲电子设备的控制方法、装置及电子设备

- 电子设备的显示屏盖板、电子设备及电子设备的控制方法

- 电子设备和制造该电子设备的壳体的方法

- 供电系统、控制供电系统的方法及电子设备

- 移动电子设备供电系统和移动电子设备