一种适用于SRAM型FPGA产品的系统级空间单粒子防护方法

文献发布时间:2023-06-19 10:06:57

技术领域

本发明涉及一种适用于SRAM型FPGA产品的系统级空间单粒子防护方法,特别是对SRAM型FPGA从五个层级协同实施的全面防护体系结构和层级间协同关联的交互机制,属于空间飞行器单粒子防护技术领域。

背景技术

空间辐射环境对空间飞行器的电子产品有着严重的影响,单粒子效应(SEE)是主要要考虑的影响,会产生潜在的严重后果,包括信息丢失和功能失效等。宇宙空间存在着各种粒子,如质子、电子、重离子等,当具有足够转移能量的带电粒子击中器件时,就可能发生单粒子效应,进而引发系统故障。根据粒子能量大小和击中器件的位置,单粒子效应可能产生损坏或瞬时效应。单粒子效应包括单粒子翻转(SEU-存储单元中的位翻转)、单粒子锁定(SEL-瞬态电流导致设备功能性损坏)、单粒子烧毁(SEB-场效应管漏源极烧毁)、单粒子栅击穿(SEGR-功率MOSFETs器件的栅氧化物中形成导电路径的烧毁)等。

近年来,空间飞行器的电子系统大量采用SRAM型FPGA这种大规模集成电路器件,以满足数字化设计、融合化设计等带来的信息交互复杂、数据处理量增加、算法实现大量增加的需求,实现更多功能和更优性能。SRAM型FPGA在空间飞行器上的应用数量越来越多,对应门电路的门数越来越高,发生的单粒子事件越来越多,已成为近年来空间飞行器发生数量较多、影响较大的重大威胁之一。

SRAM型FPGA的门数越高,可实现的加固措施越少,更别提单粒子免疫的实现可能。对国内器件来说,还受限于国内器件加固的工艺水平,可实现的加固程度相对欧美更低。因此,仅仅通过器件选用,无法避免SRAM型FPGA单粒子事件的发生,也无法有效应对单粒子事件的影响。单粒子效应可能造成瞬时效应,也可能造成不可恢复的损坏;对瞬时效应,可以通过容错等方法纠正或恢复;对不可恢复的损坏,只能通过备份手段实现功能保证或将影响减低到最小。目前情况下,最可能的单粒子防护理想目标是:发生单粒子事件时尽量不中断正常工作、无法避免中断时尽量降低中断的破坏性影响和恢复正常前的中断时间。为了实现这个可能的理想目标,需要建立各个层级协同统一的防护体系结构,并通过层级间协同关联的交互机制,实现协同应对单粒子事件的全面防护,提升空间飞行器不间断稳定运行的能力。

发明内容

本发明解决的问题:克服现有技术的不足,提出了一种适用于SRAM型FPGA产品的系统级空间单粒子防护方法,避免或降低目前较多空间飞行器存在的单粒子防护重芯片但系统性不足、有一定系统考虑但针对性、协调性不足带来的防护漏洞的问题。

本发明的技术解决方案:

一种适用于SRAM型FPGA产品系统级空间单粒子防护方法,步骤如下:

(1)进行器件空间单粒子防护设计,所述器件是指SRAM型FPGA;

(2)进行模块空间单粒子防护设计,所述模块是指单机中SRAM型FPGA所在的功能模块,即FPGA所在模块;

(3)进行单机空间单粒子防护设计,所述单机是指SRAM型FPGA所在单机,该单机包含FPGA所在模块;

(4)进行分系统空间单粒子防护设计,所述分系统是指SRAM型FPGA所在单机归属的分系统;

(5)进行系统空间单粒子防护设计,所述系统是指空间飞行器整体,包含FPGA所在分系统。

进一步的,进行器件空间单粒子防护设计,具体为:

(1.1)确认器件满足单粒子防护基本指标后,进行硬件层面的器件单粒子防护设计;

(1.2)进行参数、变量寄存器选用和处理;

(1.3)在参数、变量寄存器选用和处理后,进行参数、寄存器、逻辑的三模冗余,如果资源条件无法实现全三模冗余,则对重要参数、寄存器、逻辑进行三模冗余;

(1.4)进行周期性定时刷新;

(1.5)在周期性定时刷新后,进行回读,如果全回读无法实现,对配置地址寄存器回读;

(1.6)器件复位:FPGA所在模块给器件发送自复位信号,器件响应该自复位信号而恢复正常,或FPGA所在模块给器件直接实施硬复位。

进一步的,单粒子防护基本指标包括SEU、SEL、SEB、SEGR防护指标;进行硬件层面的器件单粒子防护设计包括先后进行的抗单粒子锁定硬件设计和Half-Latch处理的硬件设计;

进行参数、变量寄存器选用和处理,具体为:采用Slice替代SRL16和分布式RAM;Slice是指FPGA的最小逻辑单元,SRL16是指16bit移位寄存器查找表。

进一步的,所述全三模冗余是指:对全部参数、寄存器、逻辑进行三模冗余处理;所述重要参数、寄存器、逻辑是指:错误后会导致FPGA产品功能性能重大变化,无法通过周期性定时刷新和回读恢复,也无法随FPGA运行而获得足够短时间的动态更新的参数、寄存器、逻辑。

进一步的,所述步骤(1.4)进行周期性定时刷新,具体为:选择JTAG或SelectMAP配置方式进行周期性定时刷新;如选用SelectMAP配置方式,最初产生配置文件时需设置SelectMAP配置端口在配置后保持配置功能,不被复用为普通I/O口;如果资源条件无法去除BRAM的使用,对BRAM采用运算代替周期性定时刷新,缩短运算流水更新周期使其不大于定时刷新周期。

进一步的,所述全回读是指:对全部配置寄存器进行回读。所述对配置地址寄存器回读是指:根据选用的配置方式是JTAG还是SelectMAP,相应对JTAG或SelectMAP配置地址寄存器回读。

进一步的,进行模块空间单粒子防护设计,具体为:FPGA所在模块监测FPGA器件工作状态,实施对器件的故障诊断,诊断确认其故障后,给FPGA器件发送自复位信号实施FPGA器件自复位,或直接实施硬复位;所述硬复位是指:通过硬件对FPGA复位,复位后会重新加载FPGA;所述自复位是指:通过软件给FPGA一个复位信号,FPGA自己复位,复位后不需要进行FPGA的加载,只是配置芯片的初始化;

FPGA所在模块将自身状态信息发送给FPGA所在单机的管控模块,在收到该管控模块的复位命令后实施自复位、直接由该管控模块对FPGA所在模块进行复位或者切换备份模块;FPGA所在模块与所述管控模块之间通过电平信号或串并行接口形式的数据方式进行交互;

所述FPGA所在单机的管控模块是指:FPGA所在单机中用于管控所有模块的功能模块,采取对单粒子不敏感的反熔丝FPGA器件实现。

进一步的,进行单机空间单粒子防护设计,具体为:FPGA所在单机的管控模块监测FPGA所在模块上报的状态信息,诊断确认FPGA所在模块故障后,给FPGA所在模块发送自复位信号实施FPGA所在模块的自复位、直接实施硬复位或者切换备份模块;

FPGA所在单机将其自身状态信息发送给FPGA所在分系统的管控单机,在收到该管控单机的复位命令后实施FPGA所在单机的自复位、直接由该管控单机对FPGA所在单机进行复位、关机再开机或者切换单机备份;FPGA所在单机与该管控单机之间通过串并行接口形式的数据、遥测数据和遥控指令、电平信号或者总线数据方式进行交互;

所述FPGA所在分系统的管控单机是指:FPGA所在分系统中,用于管控分系统中所有其他单机的单机。

进一步的,进行分系统空间单粒子防护设计,具体为:

FPGA所在分系统的分系统管控单机监测FPGA所在单机上报的状态信息,诊断确认FPGA所在单机故障后,给FPGA所在单机发送自复位信号实施FPGA所在单机的自复位、直接实施硬复位、关机再开机或者切换单机备份;

FPGA所在分系统的分系统管控单机将该分系统的状态信息发送给全系统管控单机;在收到该全系统管控单机的模式调整命令后,调整设置该分系统各单机的工作状态;分系统管控单机与该全系统管控单机之间通过遥测数据和遥控指令、串并行接口形式的数据或者总线数据方式进行交互;

所述全系统管控单机是指:空间飞行器整体中,用于管控所有分系统的单机。

进一步的,进行系统空间单粒子防护设计,具体为:

全系统管控单机监测FPGA所在分系统管控单机上报的状态信息,诊断确认FPGA所在分系统故障后,给FPGA所在分系统管控单机发送模式调整命令实施该分系统各单机工作状态的调整。

本发明与现有技术相比的优点在于:

(1)本发明给出了实现系统级空间单粒子防护的流程,按此流程实现,能够避免现有技术实现时逻辑关系不协调造成的防护覆盖不全的漏洞;

(2)本发明给出的系统级单粒子防护体系结构具备系统性,在目前情况下能够更加全面地防护单粒子事件的漏洞,而不是仅选择某个层级单独应对;

(3)本发明给出的五个层级间协同关联的交互机制,规范了单粒子防护时各层级的作用和相互关系,具有协调性、通用性,逻辑清晰,能够容易地统一设计和实现,可以被各种空间飞行器采用。

(4)本发明SRAM型FPGA产品系统级空间单粒子防护方法,从器件、模块、单机、分系统、系统五个层级构建的单粒子全面防护体系结构。层级间采用邻级上报状态和邻级发送恢复命令的邻级交互机制,即本级向相邻上级上报本级状态(模块向单机、单机向分系统、分系统向系统上报状态);本级向相邻下级发送恢复命令(系统恢复分系统、分系统恢复单机、单机恢复模块、模块恢复器件)控制下级恢复工作状态。

(5)本发明基于全面防护体系结构和协同关联交互机制的系统级空间单粒子防护方法,实现目前情况下最可能的单粒子防护理想目标“发生单粒子事件时尽量不中断正常工作、无法避免中断时尽量降低中断的破坏性影响和恢复正常前的中断时间”,避免或降低目前较多空间飞行器存在的单粒子防护重芯片但系统性不足、有一定系统考虑但针对性、协调性不足带来的防护漏洞。而任何这些防护漏洞都可能成为SRAM型FPGA发生单粒子事件的威胁突破点。

附图说明

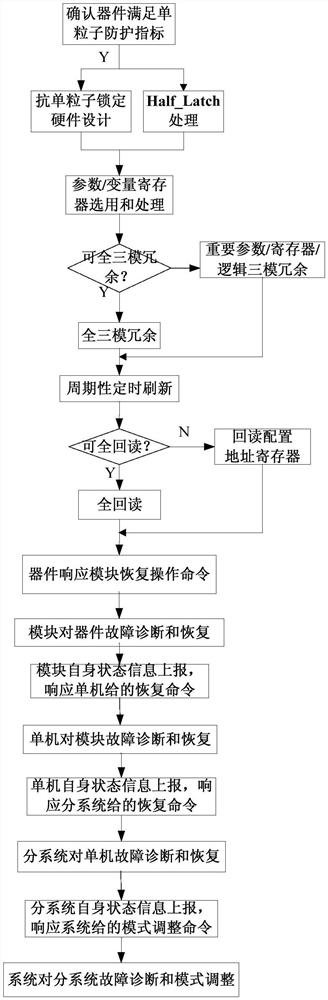

图1为本发明的系统级空间单粒子防护方法流程图;

图2为本发明的系统级空间单粒子防护体系结构和交互机制;

图3为本发明实施例中器件、单机级单粒子防护的示意图;

图4为本发明实施例中单机、分系统、系统级单粒子防护的示意图;

图5为本发明实施例中的各级交互实现的逻辑示意图。

具体实施方式

如图1所示,本发明SRAM型FPGA产品系统级空间单粒子防护方法,按照器件、模块、单机、分系统、系统五个层级,分级实施:

(1)按以下步骤顺序进行器件级单粒子防护实施

1)确认单粒子防护基本指标,包括SEU、SEL、SEB、SEGR等不同单粒子效应的防护指标。

2)进行硬件层面的器件单粒子防护设计,包括抗单粒子锁定硬件设计,以及Half-Latch处理的硬件设计。Half-Latch处理的硬件设计一般采取器件管脚去电平上拉等措施。

3)进行参数/变量寄存器选用和处理。在编译的时候,通过设置约束条件,用Slice(FPGA的最小逻辑单元)替代SRL16(16bit移位寄存器查找表)和分布式RAM。

4)进行参数/寄存器/逻辑的三模冗余。如果资源条件无法实现全三模冗余,对重要参数/寄存器/逻辑实现三模冗余。所述全三模冗余是指:对全部参数、寄存器、逻辑进行三模冗余处理。所述重要参数、寄存器、逻辑是指:错误后会导致FPGA产品功能性能重大变化,无法通过周期性定时刷新、回读恢复,也无法随FPGA运行而获得足够短时间的动态更新的参数、寄存器、逻辑。

5)进行周期性定时刷新。选择JTAG或SelectMAP配置方式进行周期性定时刷新;如选用SelectMAP配置方式,最初产生配置文件时需设置SelectMAP配置端口在配置后保持配置功能,不被复用为普通I/O口。如果资源条件难以去除BRAM的使用,对BRAM采用优化逻辑和算法设计代替周期性定时刷新,缩短运算流水更新周期使其不大于定时刷新周期。

6)进行回读。如果全回读无法实现,对配置地址寄存器回读。所述全回读是指:对全部配置寄存器进行回读。所述对配置地址寄存器回读是指:根据选用的配置方式是JTAG还是SelectMAP,相应对JTAG或SelectMAP配置地址寄存器回读。

7)器件复位:FPGA所在模块给器件发送自复位信号,器件响应该自复位信号而恢复正常,或FPGA所在模块给器件直接实施硬复位。

(2)模块级单粒子防护实施。

FPGA所在模块监测FPGA器件工作状态,诊断确认其故障后,给其发送自复位信号实施其自复位,或直接实施硬复位;FPGA所在模块将其自身状态信息发送给FPGA所在单机管控模块,在收到该管控模块的复位命令后实施其自复位、直接由该管控模块对其进行复位或者切换备份模块;其与该管控模块之间通过电平信号或串并行接口形式的数据方式进行交互。

所述硬复位是指:通过硬件对FPGA复位,复位后会重新加载FPGA。所述自复位是指:通过软件给FPGA一个复位信号,FPGA自己复位,复位后不需要进行FPGA的加载,只是配置芯片的初始化。所述FPGA所在单机管控模块是指:FPGA所在单机中用于管控所有模块的功能模块,一般采取对单粒子不敏感的反熔丝FPGA器件等实现。

(3)单机级单粒子防护实施。

FPGA所在单机的管控模块监测FPGA所在模块上报的状态信息,诊断确认FPGA所在模块故障后,给其发送自复位信号实施其自复位、直接实施硬复位或者切换备份模块。FPGA所在单机将其自身状态信息发送给FPGA所在分系统管控单机,在收到该管控单机的复位命令后实施其自复位、直接由该管控单机对其进行复位、关机再开机或者切换单机备份;其与该管控单机之间通过串并行接口形式的数据、遥测数据和遥控指令、电平信号或者总线数据方式进行交互。

所述FPGA所在分系统管控单机是指:FPGA所在分系统中,用于管控分系统所有单机的单机。

(4)分系统级单粒子防护实施。

FPGA所在分系统的分系统管控单机监测FPGA所在单机上报的状态信息,诊断确认FPGA所在单机故障后,给FPGA所在单机发送自复位信号实施FPGA所在单机的自复位、直接实施硬复位、关机再开机或者切换单机备份;

FPGA所在分系统的分系统管控单机将该分系统的状态信息发送给全系统管控单机;在收到该全系统管控单机的模式调整命令后,调整设置该分系统各单机的工作状态;分系统管控单机与该全系统管控单机之间通过遥测数据和遥控指令、串并行接口形式的数据或者总线数据方式进行交互;

所述全系统管控单机是指:空间飞行器整体中,用于管控所有分系统的单机。

(5)系统级单粒子防护实施。

全系统管控单机监测FPGA所在分系统管控单机上报的状态信息,诊断确认FPGA所在分系统故障后,给FPGA所在分系统管控单机发送模式调整命令实施该分系统各单机工作状态的调整。

如图2所示为本发明实现的系统级空间单粒子防护体系结构,该系统级空间单粒子防护体系结构由5个层级组成,各层级主要实现如下:

1)LEVEL1(器件级),包括器件选用、硬件防护(抗单粒子锁定硬件设计以及Half-Latch处理的硬件设计)、容错(参数/变量寄存器选用和处理、参数/寄存器/逻辑的三模冗余、周期性定时刷新、回读措施),响应FPGA所在模块控制命令而恢复自身工作。

2)LEVEL2(模块级),包括FPGA所在模块对FPGA器件工作状态的监测,控制恢复FPGA器件工作,将其自身状态信息上报FPGA所在单机(发送给FPGA所在单机管控模块),响应FPGA所在单机(FPGA所在单机管控模块发出的)控制命令恢复自身工作。与FPGA所在单机管控模块之间通过电平信号或串并行接口形式的数据方式进行交互。

3)LEVEL3(单机级),包括FPGA所在单机对FPGA所在模块上报的状态信息进行监测,控制恢复FPGA所在模块工作,将其自身状态信息上报FPGA所在分系统(发送给FPGA所在分系统管控单机),响应FPGA所在分系统(FPGA所在分系统管控单机发出的)控制命令恢复自身工作。与FPGA所在分系统管控单机之间通过串并行接口形式的数据、遥测数据和遥控指令、电平信号或者总线数据方式进行交互。

4)LEVEL4(分系统级),包括FPGA所在分系统对FPGA所在单机上报的状态信息进行监测,控制恢复FPGA所在单机工作,将其自身状态信息上报系统(发送给全系统管控单机),响应系统(全系统管控单机发出的)控制命令恢复自身工作。与系统管控单机之间通过遥测数据和遥控指令、串并行接口形式的数据或者总线数据方式进行交互。

5)LEVEL5(系统级),包括系统对FPGA所在分系统上报的状态信息进行监测,控制恢复FPGA所在分系统工作。

实施例

以某卫星为例,其测控分系统相同设计、相互备份的测控应答机A、测控应答机B(均为单机)中采用了SRAM型FPGA器件。

如图3所示,为本发明实施例中测控应答机采用SRAM型FPGA后的模块级、单机级单粒子防护示意图。其中,模块A、模块B为测控应答机中实现相同功能的相互备份、相同设计的模块;模块A、模块B中的计算FPGA为SRAM型FPGA,模块管控FPGA为单粒子不敏感的反熔丝FPGA。计算FPGA与模块管控FPGA之间通过电平信号形式交互(高电平有效),模块管控FPGA与单机管控模块之间通过电平信号形式交互(高电平有效),测控应答机经由其的单机管控模块,通过RS422串口以速率4Kbps与测控分系统管控单机(测控上位机)进行交互。

如图4所示,为本发明实施例中单机、分系统、卫星系统级单粒子防护的示意图。其中,每个分系统管控单机均对该分系统的多个单机进行管控,分系统1为测控分系统,分系统N为有效载荷分系统。测控分系统管控单机(分系统1管控单机,即测控上位机)通过RS422串口以速率4Kbps与测控分系统的各单机分别进行交互,有效载荷分系统管控单机(分系统N管控单机,即有效载荷上位机)通过155B总线分别与有效载荷分系统的各单机进行交互。各个分系统管控单机与系统管控单机(整星管理单元)均通过1553B总线进行交互,1553B总线以448ms为最小通信周期。

如图5所示,为本发明实施例中的各级上报、诊断、恢复的交互逻辑示意图,其中的器件为测控应答机采用的SRAM型FPGA,模块为测控应答机中的模块A、模块B,单机为测控应答机A、测控应答机B,分系统为测控分系统,系统为该卫星整体。

本发明实施例中建立的单粒子全面防护体系结构实现如下:

1)根据计算量的需要,对测控应答机中模块A、模块B的计算FPGA采用百万门级SRAM型FPGA,不是单粒子免疫器件,必须采用各级防护措施。首先在硬件层面采取标准化的电路设计实现了抗单粒子锁定硬件设计,对Half-Latch处理采取器件管脚去电平上拉的硬件设计,并采取后续的其它防护措施。

2)计算FPGA为防护单粒子事件,不适合采用SRL16和分布式RAM,因此在编写FPGA代码的时候,设置约束条件,编译的时候将代码映射到芯片的硬件资源,用Slice替代SRL16和分布式RAM。

3)鉴于该FPGA为百万门级,估算即使实现三模冗余,FPGA资源仍能足够保证FPGA运行后实现的功能性能,因此对计算FPGA的参数/寄存器/逻辑设计实现了全三模冗余。

4)设计周期性定时刷新。周期性定时刷新的刷新芯片选择单粒子免疫的ASIC芯片,根据数据使用的频率需求和资源条件,综合考虑选择刷新周期为2秒,选择JTAG配置方式实现周期性定时刷新。鉴于资源条件难以对BRAM全部去除,设计BRAM时只保留不进行定时刷新而单粒子事件发生后也不影响后续运行的内容,同时采用优化逻辑和算法设计代替周期性定时刷新,缩短运算流水更新周期使其不大于定时刷新周期,通过运算流水自动更新BRAM内容。

5)鉴于实现了前序措施后,FPGA资源不足以实现全回读,否则FPGA运行后实现的功能性能会受到影响,选择只对配置地址寄存器回读设计;鉴于配置方式为JTAG,选择对JTAG配置地址寄存器回读。

6)设计测控应答机的模块A或模块B中的计算FPGA收到模块管控FPGA发出的复位命令后,完成自复位。

7)设计测控应答机的模块A或模块B中的模块管控FPGA监测计算FPGA的工作状态(喂狗状态等),确认故障(如不连续喂狗)后,给计算FPGA发送复位命令;模块管控FPGA将所在模块的状态信息(工作模式等)上报给测控应答机中的单机管控模块,收到单机管控模块发出的复位命令后,完成所在模块的自复位。

8)设计测控应答机的单机管控模块监测模块A、模块B上报的状态信息,确认某个模块故障(如工作模式异常标志、上报勤务信息中断)后,给该故障模块的模块管控FPGA发送复位命令;在不成功时将该模块关机,将备份模块开机使用,即切换备份模块。设计单机管控模块将单机状态信息(模块A/模块B电源状态、工作模式等)综合后,通过RS422串口上报给测控上位机(测控分系统管控单机);收到测控上位机发出的复位或开关机命令后,完成测控应答机单机复位或开关机。

9)设计测控上位机(测控分系统管控单机)通过RS422串口,接收监测测控应答机A、测控应答机B的状态信息,确认某个测控应答机(如模块A电源状态异常)故障后,给该测控应答机发送复位或开关机命令(由测控应答机的单机管控模块接收);在不成功时将该单机关机,将备份单机开机使用,即切换备份单机。设计测控上位机收集测控分系统各单机的状态信息(测控应答机A、测控应答机B电源状态、工作模式、输出标志等),通过1553B总线上报给整星管理单元(系统管控单机);收到整星管理单元(系统管控单机)发出的模式调整命令(如设置测控分系统统一切换到备份测控体制)后,完成测控分系统各单机的工作模式设置,即调整测控分系统部分单机的开关机状态和单机的工作模式,以新的工作状态工作(如测控应答机A、测控应答机B统一切换到备份测控体制模式),实现卫星整体需要测控分系统提供的功能性能。

10)设计整星管理单元(系统管控单机)通过1553B总线,接收监测各分系统的状态信息;确认测控分系统(如测控应答机B故障导致测控分系统无输出)故障后,给测控上位机(测控分系统管控单机)发送测控分系统模式调整命令。

- 一种适用于SRAM型FPGA产品的系统级空间单粒子防护方法

- SRAM型FPGA在轨单粒子翻转防护量化评估方法