一种自动测试设备测试激励输出通道的扩展方法及装置

文献发布时间:2023-06-19 11:05:16

技术领域

本发明涉及自动测试设备仪器技术领域,尤其是涉及一种自动测试设备测试激励输出通道的扩展方法及装置。

背景技术

自动测试设备中可以产生测试激励的通道数量跟测试设备的等级有关,低端的测试设备往往只有一个测试激励通道,中端的测试设备一般有8个或16个测试激励通道,只有高端的测试设备才会采用per pin的结构,配备独立的测试激励通道,测试激励通道的数目也会高达256个以上。

在使用自动测试设备时,若使用低端或中端的测试设备,因其测试激励通道数目有限,只能通过共享的方式逐次使用,在需要同时使用时,无法满足测试要求,因此必需采用高端的测试设备才能完成测试。

发明内容

为解决现有技术的不足,实现单测试激励输出通道扩展为2个以上各通道的目的,本发明采用如下的技术方案:

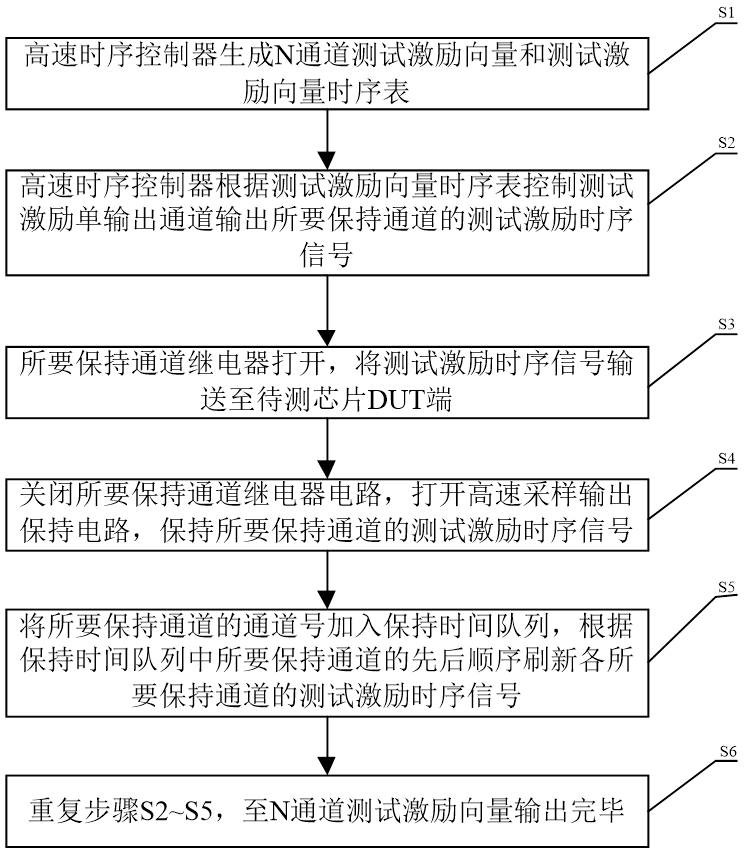

一种自动测试设备测试激励输出通道的扩展方法,包括如下步骤:

S1:高速时序控制器生成N通道测试激励向量和测试激励向量时序表;

S2:高速时序控制器根据测试激励向量时序表控制测试激励单输出通道输出所要保持通道的测试激励时序信号;

S3:所要保持通道继电器打开,将测试激励时序信号输送至待测芯片DUT端;

S4:关闭所要保持通道继电器电路,打开高速输出保持电路,保持所要保持通道的测试激励时序信号;

S5:将所要保持通道的通道号加入保持时间队列,根据保持时间队列中所要保持通道的先后顺序刷新各所要保持通道的测试激励时序信号;

S6:重复步骤S2~S5,至N通道测试激励向量输出完毕。

进一步的,所述步骤S5具体包括如下步骤:

S51:将所要保持通道的通道号x根据所述测试激励向量时序表中定义的先后顺序依次加入所述保持时间队列中;

S52:所述高速时序控制器在所述测试激励单输出通道输出测试激励信号空闲时,将所述测试激励单输出通道接入所述保持时间队列头中保存的通道号所对应的通道,重新刷新保持时间;

S53:将所述保持时间队列中的队列的通道号x从所述保持时间队列头中删除并重新加入队列尾中。

进一步的,所述步骤S1中的高速时序控制器的工作频率大于等于1GHz。

进一步的,所述步骤S1中的N为大于等于2的整数。

进一步的,所述步骤S2中的测试激励时序信号的脉冲幅值范围为0~10V,脉冲宽度大于等于10ns。

进一步的,所述步骤S4中高速输出保持电路为高速采样输出保持电路,采样时间小于等于1ns,保持时间大于等于100us。

一种自动测试设备测试激励输出通道的扩展装置,包括高速时序控制器、测试激励单输出通道、高速输出保持继电器电路组,所述高速输出保持继电器电路组包括N组高速输出保持电路和继电器电路的组合,高速时序控制器根据其生成的测试激励向量时序表控制测试激励单输出通道输出所要保持通道的测试激励时序信号,时序信号分别接入N组高速输出保持电路和继电器电路的组合,当需要一组输出时序信号时,首先将该组的继电器打开,将时序信号输送给待测芯片DUT端,然后关闭继电器并启动高速输出保持电路,保持该组的输出信号,并能在下一个测试激励单输出通道输出间隙重新刷新该组的输出信号。

进一步的,所述高速输出保持继电器电路组为高速采样输出保持继电器电路组,包括N组高速采样输出保持电路和继电器电路的组合。

进一步的,设置保持时间队列,将所要保持通道的通道号加入保持时间队列,根据保持时间队列中所要保持通道的先后顺序刷新各所要保持通道的测试激励时序信号。

本发明的优势和有益效果在于:

本发明通过采样输出保持电路将单测试激励输出通道扩展为多个测试激励输出通道,节省了自动测试设备测试激励输出通道资源,降低自动测试设备的结构复杂度和成本,并能增加自动测试设备测试激励输出通道的数目。

附图说明

图1为本发明的方法流程图。

图2为本发明中高速采样输出保持继电器电路组的内部结构示意图。

图3为本发明中测试激励单输出通道扩展的结构示意图。

图4为本发明中测试激励单输出通道组扩展的结构示意图。

具体实施方式

以下结合附图对本发明的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

如图1所示,一种自动测试设备测试激励输出通道的扩展方法,包括如下步骤:

S1:高速时序控制器生成N通道测试激励向量和测试激励向量时序表。

优选地,高速时序控制器的工作频率大于等于1GHz,N通道测试激励向量时序表由所述高速时序控制器根据所述N通道测试激励向量生成,其中N为大于等于2的整数。

S2:高速时序控制器根据测试激励向量时序表控制测试激励单输出通道输出所要保持通道的测试激励时序信号。

优选地,测试激励时序信号的脉冲幅值范围为0~10V,脉冲宽度大于等于10ns。

S3:所要保持通道继电器打开,将测试激励时序信号输送至待测芯片DUT端。

S4:关闭所要保持通道继电器电路,打开高速采样输出保持电路,保持所要保持通道的测试激励时序信号。

优选地,高速采样输出保持电路的采样时间小于等于1ns,保持时间大于等于100us。

S5:将所要保持通道的通道号加入保持时间队列,根据保持时间队列中所要保持通道的先后顺序刷新各所要保持通道的测试激励时序信号。

具体的,保持时间队列里的通道号所对应的保持通道根据队列“先进先出”的原则刷新保持时间,具体包括如下步骤:

S51:将所要保持通道的通道号x根据所述测试激励向量时序表中定义的先后顺序依次加入所述保持时间队列中。测试激励向量时序表定义的先后顺序也是保持通道输出保持的执行顺序,执行完后立即加入保持时间队列中。

S52:所述高速时序控制器在所述测试激励单输出通道输出测试激励信号空闲时,将所述测试激励单输出通道接入所述保持时间队列头中保存的通道号所对应的通道,重新刷新保持时间。高速时序控制器在所述测试激励单输出通道输出测试激励信号空闲时是指某两个保持输出通道输出的间隙时间。

S53:将所述保持时间队列中的队列的通道号x从所述保持时间队列头中删除并重新加入队列尾中。

S6:重复步骤S2~S5,至N通道测试激励向量输出完毕。

工作原理说明:如图2所示,本发明提供的一种自动测试设备测试激励输出通道的扩展方法,其原理如下:

测试激励单输出通道输出的信号输入高速采样输出保持继电器电路组,经过高速采样输出保持继电器电路组扩展为N通道测试激励输出通道给待测芯片DUT端。高速采样输出保持继电器电路组由N组高速采样输出保持电路和继电器电路组成,每一组包括1个高速采样输出保持电路和1个继电器电路,其中N为大于等于2的整数。测试激励单输出通道的输出信号分别接入N组高速采样输出保持电路和继电器电路,当需要某一组输出信号时,首先将该组的继电器打开,将信号输送给待测芯片DUT端,而后关闭继电器并启动高速采样输出保持电路工作,保持该组的输出信号,并能在下一个测试激励单输出通道输出间隙重新刷新该组的输出信号。其中,高速采样输出保持继电器电路组还可通过模拟电压锁存的方式的来实现。

实施例一,如图3所示,系统采样一组测试激励单输出通道和一组高速采样输出保持继电器电路组对一组测试激励单输出通道的测试激励信号进行扩展。

实施例二,如图4所示,系统采样M组测试激励单输出通道和M组高速采样输出保持继电器电路组对M组测试激励单输出通道的M组测试激励信号进行扩展,其中M为大于等于2的整数。

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的范围。

- 一种自动测试设备测试激励输出通道的扩展方法及装置

- 测试接头装置、测试电缆及自动测试设备