一种具有令牌桶结构的多通道DMA的控制方法和装置

文献发布时间:2023-06-19 10:24:22

技术领域

本发明涉及计算机应用技术领域,特别是涉及一种具有令牌桶结构的多通道DMA控制器的处理方法和装置。

背景技术

令牌桶技术,是一种常用的流量控制技术。令牌桶的优点之一是其不使用策略,在系统中处理的数据量取决于其投入令牌的数量,可以针对不同的通道标记配置不同的流量策略,而且算法灵活。令牌桶算法有多种不同的算法,例如单速单筒,是指在向令牌桶投放令牌的速率(CIR)只有一个,以及一个桶(C桶);单速(CIR)双通(E桶、C桶)和双速(CIR、PIR)双桶(C桶、P桶)等不同的配速和计算统计形式。

DMA(Direct Memory Access,直接存储存取),它允许在一个SOC处理器系统当中不占用大量的CPU资源,将不同速度的硬件装置间的数据互相传输。而传统的多通道DMA控制器一般的做法是对不同的通道分配不同的优先级,根据优先级来仲裁选择通道数据传输,因此当某一个高优先级DMA通道突发产生大量传输请求时,会占用较多的总线资源,导致总线或者其他通道的阻塞。

发明内容

本发明提供了具有令牌桶结构的多通道DMA控制器的处理方法和装置,该方法和装置主要使用了令牌桶算法技术,对每个通道配置DMA的传输带宽,并根据令牌的计算来判断该DMA请求是否执行。对于允许执行的DMA请求,DMA控制器将其处理执行,对于计算不满足通过的请求,DMA控制器将该请求消息重新写入请求队列FIFO。

本发明为实现上述目的所采用的技术方案是:

一种具有令牌桶结构的多通道DMA的控制方法,包括以下步骤:

1)初始化DMA通道并通过寄存器配置模块配置DMA读写请求;

2)将DMA读写请求转换为请求消息;

3)将请求消息写入请求队列;

4)具有令牌桶结构的流量统计仲裁器根据请求消息中的通道号读取令牌表;

5)计算令牌表中的令牌是否满足条件,若满足条件,则更新令牌表并处理读写请求,直至完成数据传输;否则重新计算令牌并更新令牌表,返回步骤3)。

所述初始化DMA通道具体为:配置外设的寄存器地址、存储器的寄存器地址、数据传输方向、传输方式,以及DMA传输外设对应通道的传输速率即配置令牌表中的配置CIR、CBS的值。

所述步骤2)具体为:

根据读写请求中请求的通道、外设的寄存器地址、存储器的寄存器地址、传输方向的配置,将读写请求转换为一周期的指令信息。

所述令牌表包括:上一次命中该DMA通道传输的时间Hit_time、承诺信息速率CIR、承诺突发尺寸CBS、桶内令牌的数量Token、表项的状态Status。

令牌的计算过程为:

首先用具有令牌桶机构的流量统计仲裁器中的计数器的值减去令牌表中的Hit_time值,得到时间差△Time;

再计算△Time乘以令牌表中的cir得到当前时间累积的令牌数量值,记作new_tmp_token;

最后使用new_tmp_token加上读写请求中传输数据的数量-buf_num,得到新的令牌数量值,记作new_token。

判断令牌是否满足条件具体为:

比较new_token与令牌表中的+CBS,若new_token大于+CBS,则读写请求允许通过,并将+CBS的值写入令牌表的Token值的位置;若new_token小于+CBS且大于0,则读写请求允许通过,并将new_token的值写入令牌表的Token值的位置;若new_token小于0,则读写请求不允许通过,令牌表的Token值不变。

一种具有令牌桶结构的多通道DMA的控制装置,包括:

总线接口转换模块,用于将DMA总线形式的读写请求转换成模块内部的消息格式;

请求队列FIFO,用于将总线接口转换模块所转换的DMA操作请求按先进先出的队列方式存储;

具有令牌桶机构的流量统计仲裁器,用于使用投放令牌形式的通道流量统计,并根据流量的计算仲裁该读写请求是否通过;

DMA读写控制器,用于配置的总线数据读写接口;

寄存器配置模块,用于配置外设的寄存器地址、存储器的寄存器地址、数据传输方向、传输方式,以及DMA传输外设对应通道的传输速率即配置令牌表中的配置CIR、CBS的值。

所述模块内部的消息格式为一个时钟周期的DMA操作指令,包含DMA通道号、DMA操作地址、DMA操作模式。

所述令牌储存在令牌表中,所述令牌表包括:上一次命中该DMA通道传输的时间Hit_time、承诺信息速率CIR、承诺突发尺寸CBS、桶内令牌的数量Token、表项的状态Status。

令牌桶结构的仲裁器有2个数据出口,如果仲裁通过的读取请求,输出至DMA读写控制器模块,如果是仲裁不通过的读写请求,输出至请求队列FIFO,等待下一次仲裁判断。

本发明具有以下有益效果及优点:

1.本发明通使用令牌桶结构的仲裁器,可以根据计算流量来判断该数据请求是否处理,避免传统根据优先级判断的DMA控制器,由于某一高优先级数据流量突发导致总线被过度占用的情况。

2.本发明的DMA控制器可以根据不同功能需求配置不同参数,灵活性高。

3.本发明的DMA控制器可以兼容现有微控制器系统平台,兼容性好。

附图说明

图1本发明在典型微处理器内核流水线中的架构位置;

图2本发明的内部模块结构图;

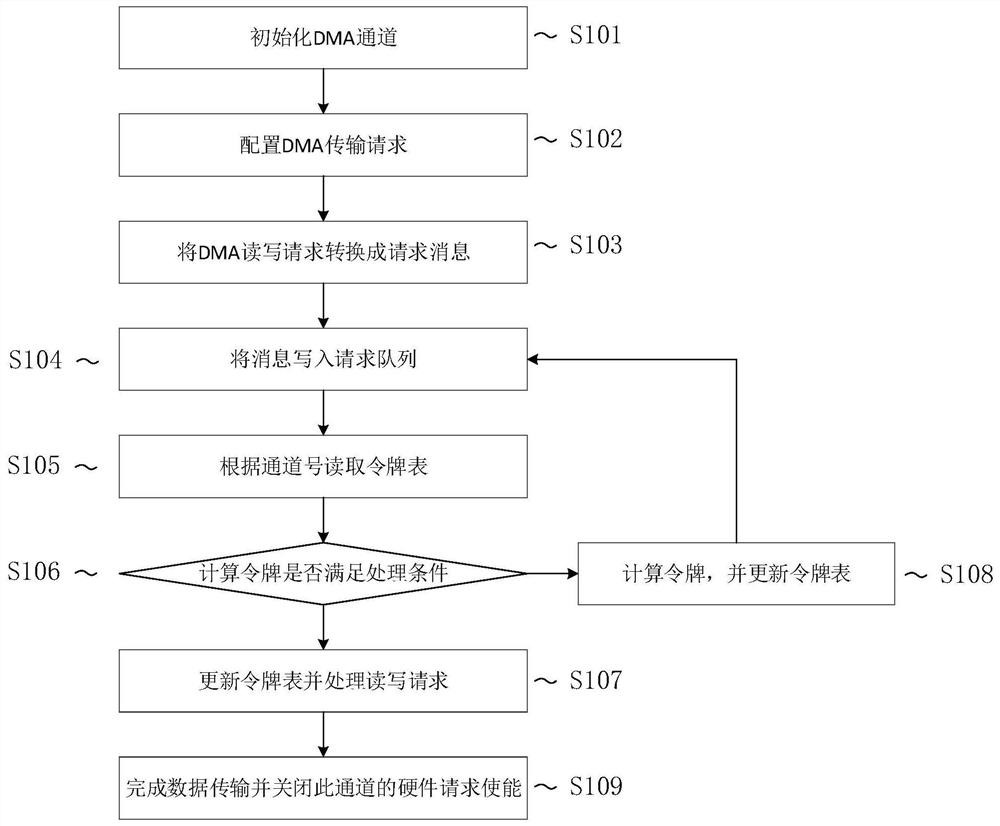

图3本发明的工作流程图;

图4本发明令牌桶模块逻辑图;

图5本发明的令牌表的表项数据结构图;

图6本发明令牌计算方法示意图。

具体实施方式

下面结合附图及实施例对本发明做进一步的详细说明。

本发明为该DMA控制器的处理方法提供一种实现装置,其结构如图2所示,包含总线接口转换模块、请求队列FIFO、具有令牌桶结构的流量统计仲裁器、任意个通道的DMA读写控制器、寄存器配置模块。

本发明适用在各种微处理器体系架构中,典型的使用场景如图1所示。在一个包含CPU、BUS Matrix(总线互联)、BUS1(高级总线)、Brige(总线桥)、BUS2(低级总线)、Flash、SRAM、外设1、外设2等。

一种具有令牌桶结构的多通道DMA控制器的处理方法,包括:在对于多通道DMA控制器的通道仲裁处理时使用令牌桶算法结构,每个DMA通道处理的数据量取决于于其投入令牌的数量。

该DMA控制器的处理方法提供一种实现装置,其结构如图2所示,包含总线接口转换模块、请求队列FIFO、具有令牌桶结构的流量统计仲裁器、任意个通道的DMA读写控制器、寄存器配置模块。;

所述总线接口转换模块,将DMA总线形式的请求转换成模块内部的消息格式,消息格式为一个时钟周期的DMA操作指令,包含DMA通道号、DMA操作地址、DMA操作模式等操作信息。

所述请求队列FIFO,可将总线接口转换模块所转换的DMA操作请求按先进先出的队列方式存储,存储空间需大于通道数量。

如图4所示,所述具有令牌桶结构的流量统计仲裁器,使用投放令牌形式的通道流量统计,并根据流量的计算仲裁该传输是否通过。实现方法为由该模块维护一个ram存储区域,称作Token_tbl(令牌表)。该模块结构如图4所示,RAM存储如的Token_tbl内容结构图5所示,包括Hit_time、CIR、CBS、Token、Status等。

其中的Hit_time字段含义为上一次命中该DMA通道传输的时间,该字段信号由该DMA模块外提供一个单独的32位计数器(根据精度的需要可以每毫秒加1,也可以每秒钟加1)。Hit_time字段在DMA初始化时写0,伺候在每次命中该通道表项时,更新至当前时刻的计数器值,标识命中时间。

其中的CIR(Committed Information Rate),承诺信息速率。字段含义为每单位周期时间内需要向令牌桶内投放令牌的数量,该字段在DMA初始化时进行配置。

其中的CBS(CommittedBurstSize),承诺突发尺寸。字段含义为突发流量的上限,也可以理解为令牌桶容量的大小,该字段在DMA初始化时进行配置。

其中的Token字段,其含义为桶内令牌的数量,该字段在DMA初始化时写0,在每次命中该表项时,根据该通道数据是否通过、数据大小、通过时间进行计算,并在数据处理完成后更新写回该内容。

其中的Token字段,表示该表项的状态,其状态可以标识为上次的处理情况,比如该表项上次处理的数据正常通过、上次由于令牌不足而被等待等状态。

该令牌桶结构的仲裁器有2个数据出口,如果是仲裁通过的数据请求,输出至DMA读写控制器模块,如果是仲裁部通过的数据请求,输出至请求队列FIFO,等待下一次仲裁判断。

所述DMA读写控制器,可支持灵活配置的总线数据读写接口,对于跨总线的数据传输,内部使用FIFO,进行数据的缓存和异步时钟的处理。

如图3所示,本发明的系统具体的处理流程图,具体实施流程如下:

S101:初始化DMA通道,该初始化过程类似于一般的DMA控制器配置,相同的部分包括配置外设的寄存器地址及存储器的寄存器地址配置数据传输方向、传输方式等。不同的地方为根据DMA传输的外设的功能不同,配置对应通道的传输速率,其意涵就是配置CIR、CBS的值。例如想配置DMA通道1的传输速率为10MB/S、突发流量为20MB,系统提供的计数时钟为1秒增长1,CBS为0x186A0(100000的16进制),CIR为0x30D40(200000的16进制)。此过程的操作即是初始化Token_tbl,将该地址内数据写成{32’h0,32’h186A0,32’hd0D40,4’h0};

S102:配置DMA传输请求,请求可以由外设直接通过REQ信号发起,也可以通过软件配置发起;

S103:将DMA读写请求转换成请求消息,该步骤根据请求的通道、外设的寄存器地址、存储器的寄存器地址、传输方向的配置,将传输请求转换为一周期的指令信息;

S104:将消息写入请求队列,即将该请求指令信息,按照一般FIFO写入方式写入队列请求FIFO;

S105:根据通道号读取令牌表,即根据通道号读取Hit_time、CIR、CBS、Token、Status信息;

S106:计算令牌是否满足处理条件,该计算过程即是令牌的计算过程,计算方法如图6所示。首先根据系统提供的计数器和从令牌表中的Hit_time做减法得到△Time,再计算△Time×cir计算当前时间累积的令牌数量值,计做new_tmp_token。然后根据传输的请求中,传输数据的数量得到-buf_num。用new_tmp_token-buf_num,得到new_token的值。比较new_token如果大于+cbs,则该传输请求允许通过,并将+cbs的值写入Token_tbl表项的Token值的位置;如果new_token如果小于+cbs且大于0,则该传输请求也允许通过,并将new_token的值写入Token_tbl表项的Token值的位置,后跳转至S107步骤;若new_token的值小于0,则该传输请求不允许通过,表项Token的值不变,后跳转至S108步骤;

S107:更新令牌表并处理读写请求,该步骤类似于一般的DMA传输操作,根据指令中请求的通道、外设的寄存器地址、存储器的寄存器地址、传输方向的配置,通过状态机和总线,执行数据搬移动作。

S108:计算令牌并更新令牌表,计算方法在S106步骤中有叙述,该步骤更新表项Status部分字段,Status可用来辅助作为下一次的仲裁条件,也可以不适用,只用来做debug调试查看的信息。

S109:完成数据传输并关闭此通道的硬件请求使能,根据DMA传输的功能,结束DMA传输过程。

- 一种具有令牌桶结构的多通道DMA的控制方法和装置

- 一种基于令牌桶算法的IOPS控制方法及装置