压力式半导体封装及其制造方法

文献发布时间:2023-06-19 12:25:57

技术领域

本发明涉及一种压力式半导体封装及其制造方法,其通过至少一个加压部件而对半导体芯片物理加压并进行电连接,从而,提高半导体封装的耐用性并简化制造工艺。

背景技术

通常,半导体芯片封装为将半导体芯片贴装而附着在基板,通过夹子结构或接合线电连接半导体芯片和引线框架,并由热固性材料注塑半导体芯片而形成封装。

另外,现有的半导体封装是为了与半导体芯片的端子电连接而执行焊锡的导电胶,因导电胶的熔点的影响,而存在不适用于高温的驱动环境,且对于使用银烧结料或铜浆的情况,因价格高而导致制造成本上升的问题。

并且,在完成半导体封装的组装之后,执行特性检查,在进行特性检查时,在确认组装不合格或元件的破损时,无法单个更换相应部件,而需废弃整个半导体封装,由此,导致生产收益率低下。

作为解决该问题的现有技术,公开韩国注册专利公报第10-2051639号,图1显示的压力式半导体功率元件封装包括:第一金属板300,与二极管芯片的阳极端子连接而作为阳极;第二金属板400,与二极管芯片的阴极端子连接而作为阴极,另外,在第一金属板300和第二金属板400之间介有隔片500及二极管芯片600。由此,二极管封装2的结构面的特征为利用加压部件100而将第一金属板300及第二金属板400在结构上坚固地连接为一体,并将二极管芯片600的各自的电路端子准确并稳定地与第一及第二金属板300、400电连接,且保持导通状态。

但作为通过加压部件而对上部金属板和下部金属板的棱角区域加压而间接对之间的半导体芯片加压而固定结构,而提出因向半导体芯片而施加的阻焊加压降低而进一步提高耐用性的必要性。

现有技术文献

专利文献

(专利文献0001)韩国注册专利公报第10-2051639号(压力式半导体功率元件封装,2019.12.04))

(专利文献0001)韩国注册专利公报第10-2008209号(压力式半导体封装,2019.08.07))

发明的内容

发明要解决的技术问题

要实现本发明的思想的技术课题为提供一种压力式半导体封装及其制造方法,通过至少一个加压部件而对半导体芯片物理加压并电连接,从而,提高半导体封装的耐用性,并简化制造工艺。

用于解决问题的技术方案

为了实现上述目的,本发明的一实施例提供一种压力式半导体封装,其包括:引线框架,具有一个以上垫板和形成于所述垫板上的一个以上第一终端端子;至少一个半导体芯片,放置在所述引线框架上;至少一个加压部件,层叠形成在所述半导体芯片上,以加压所述半导体芯片,以用于电连接所述第一终端端子和所述半导体芯片;及封装外壳,形成于所述垫板上,而保护所述半导体芯片。

并且,所述引线框架是指介有导电胶或非导电胶而附着所述垫板和所述第一终端端子的结构。

而且,所述第一终端端子通过结合部件而附着在所述垫板。

并且,所述引线框架是指将所述垫板和所述第一终端端子通过超声波焊接或激光焊接而附着形成的结构。

而且,向所述半导体芯片而施加所述加压部件的阻焊加压,无需另外的粘合剂,也能够电连接所述第一终端端子和所述半导体芯片而进行正常运行,并向所述半导体芯片去除所述加压部件的阻焊加压,而使得解除所述第一终端端子和所述半导体芯片的电连接而不进行正常运行。

并且,所述加压部件包括:第一加压部件,处于所述半导体芯片上,以对所述半导体芯片加压;一个以上另外加压部件,对所述第一加压部件另外施加阻焊加压而完善与所述半导体芯片的电连接。

并且,所述半导体芯片被放置在所述第一终端端子的一端侧或放置在所述引线框架的垫板上。

而且,所述半导体芯片为在所述引线框架介有导电胶或非导电胶而附着,或未在所述引线框架使用另外的粘合剂,并通过所述加压部件的阻焊加压而附着。

并且,所述第一终端端子由所述垫板而以垂直方向弯曲形成,所述加压部件包括:第一加压部件,其包括:加压件,对所述半导体芯片的上端弹性加压;第二终端端子,与所述加压件连接而固定在所述垫板上,并以垂直方向弯曲形成。

而且,所述加压部件还包括:第二加压部件,层叠形成于所述第一加压部件的加压件上端,固定在所述垫板上,而以与所述加压件交叉的方向另外加压。

而且,还包括:第三加压部件,贯通所述第二加压部件而以所述半导体芯片方向对所述第一加压部件的加压件另外加压。

并且,所述第一终端端子由所述垫板按垂直方向弯曲,并向所述封装外壳的内侧方向或外侧方向弯曲而最终形成。

另外,本发明的另一实施例提供一种压力式半导体封装制造方法,包括以下步骤:准备具有一个以上垫板和形成于所述垫板上的一个以上第一终端端子的引线框架;在所述引线框架上放置至少一个半导体芯片;在所述半导体芯片上层叠形成至少一个加压部件,以对所述半导体芯片加压,以用于电连接所述第一终端端子和所述半导体芯片;形成在所述垫板上形成而保护所述半导体芯片的封装外壳。

并且,向所述半导体芯片施加所述加压部件的阻焊加压,无需另外的粘合剂,也能够电连接所述第一终端端子和所述半导体芯片而进行正常运行,向所述半导体芯片去除所述加压部件的阻焊加压而解除所述第一终端端子和所述半导体芯片的电连接而不进行正常运行。

并且,所述加压部件包括:第一加压部件,处于所述半导体芯片上,以对所述半导体芯片加压;一个以上另外加压部件,对所述第一加压部件另外施加阻焊加压而完善与所述半导体芯片的电连接。

而且,所述半导体芯片在所述引线框架未使用另外的粘合剂,并通过所述加压部件的阻焊加压附着。

并且,所述第一终端端子由所述垫板而以垂直方向弯曲形成,所述加压部件包括:第一加压部件,其包括:加压件,对所述半导体芯片的上端弹性加压;第二终端端子,与所述加压件连接而固定在所述垫板上,并以垂直方向弯曲形成。

而且,所述加压部件还包括:第二加压部件,层叠形成于所述第一加压部件的加压件上端,固定在所述垫板上,而以与所述加压件交叉的方向另外加压。

而且,还包括:第三加压部件,贯通所述第二加压部件而以所述半导体芯片方向对所述第一加压部件的加压件另外加压。

并且,所述第一终端端子由所述垫板而按垂直方向弯曲,并向所述封装外壳的内侧方向或外侧方向弯曲而最终形成。

发明的效果

本发明具有如下效果,通过至少一个加压部件而对半导体芯片物理加压并电连接,从而,提高半导体封装的耐用性,并简化制造工艺,未使用另外的粘合剂,而与粘合剂的熔点无关,在半导体的高温环境中能够进行驱动,而提高耐用性,并在通过半导体封装组装后的特性检查而确认的组装误差或组装错误或半导体芯片破损的情况下,在纠正错误或漏洞之后,或更换半导体芯片之后,容易进行重新组装。

附图说明

图1为例示现有技术的压力式半导体功率元件封装的附图;

图2为显示本发明的一实施例的压力式单个半导体封装的立体图;

图3为显示图2的压力式单个半导体封装的内部结构的附图;

图4为显示图2的压力式单个半导体封装的分解立体图;

图5为显示图2的压力式单个半导体封装的截面图;

图6为分别显示图2的压力式单个半导体封装的半导体芯片附着结构的各种示例的附图;

图7为显示本发明的另一实施例的压力式单个半导体封装制造方法的顺序图;

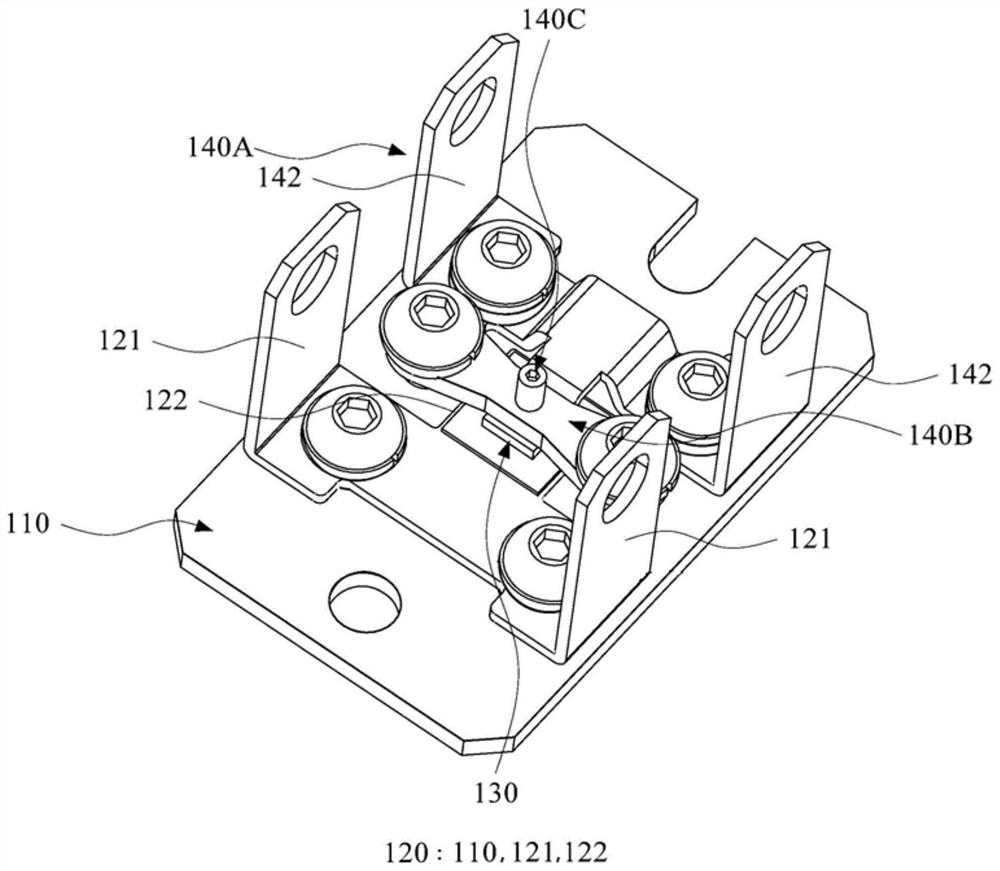

图8为显示本发明的一实施例的压力式双半导体封装的立体图;

图9为显示图8的压力式双半导体封装的分解立体图;

图10为显示图8的压力式双半导体封装的制造方法的顺序图;

图11为分别分离压力式单个半导体封装及压力式双半导体封装的第一加压部件的附图;

图12为制造本发明的一实施例的压力式半导体封装的照片。

附图标记说明

110:垫板 111、112、113,114:螺栓结合孔

120:引线框架 121:第一终端端子

122:垫板区域 123:螺栓

123a:垫环 123b:绝缘环

124:贯通孔 130:半导体芯片

140:加压部件 140A:第一加压部件

140B:第二加压部件 140C:第三加压部件

140D:第二加压部件 141:加压件

142:第二终端端子 143a:垫环

143b:绝缘环 144:螺栓

145:贯通孔 146:螺栓

146a:垫环 150:封装外壳

具体实施方式

下面,参照附图而对本发明的实施例进行具体说明,以使本发明所属技术领域的普通技术人员容易实施。本发明通过各种不同的形式实现,并非通过在此说明的实施例限定。

图2至图6为显示本发明的一实施例的压力式单个半导体封装的结构的附图,图8及图9为显示本发明的另一实施例的压力式双半导体封装的结构的附图,图7为显示本发明的一实施例的压力式单个半导体封装制造方法的附图,图10为显示本发明的另一实施例的压力式双半导体封装制造方法的附图,图11为显示本发明的压力式单个半导体封装及压力式双半导体封装的第一加压部件140A的弹性加压结构的附图。

参照图2至图6,本发明的一实施例的压力式单个半导体封装,具体地,包括:引线框架120,具有垫板110的第一终端端子121;半导体芯片130;加压部件140,层叠形成以对半导体芯片130加压;封装外壳150,保护半导体芯片130,另外,以通过加压部件而对半导体芯片物理加压并电连接,从而,提高半导体封装的耐用性,并简化制造工艺为要旨。

首先,对于引线框架120,垫板110构成为至少一个而提供附着第一终端端子121或半导体芯片130或加压部件140的空间。

例如,如图6(a)显示所示,在垫板110上直接附着形成第一终端端子121,在配置在第一终端端子121的一端侧的垫板区域122放置半导体芯片130,或如图6(b)显示所示,半导体芯片130与第一终端端子121保持一定间距分隔,而放置在垫板110上,并通过形成于垫板110上的金属图案(未图示)而电连接第一终端端子121和半导体芯片130,或如图6(c)显示所示,在垫板110和第一终端端子121连接为一体的引线框架上放置半导体芯片130,也能够对垫板和半导体芯片和第一终端端子的附着结构及电连接结构进行各种变形。

下面,对于引线框架120,在垫板110上设置至少一个第一终端端子121。

例如,第一终端端子121在与半导体芯片130电连接的至少一个第一终端端子121的一端侧配置供放置半导体芯片130的垫板区域122,但并非限定于此,如上言及所示,半导体芯片130与第一终端端子121分隔一定间距而放置在垫板110上(参照图6(b)),或也能够一体连接垫板110和第一终端端子121而构成(参照图6(c))。

并且,第一终端端子121由供放置半导体芯片130的垫板区域122或从垫板110以垂直方向弯曲而终端(另一端侧)直立形成。

另外,第一终端端子121在垫板110上附着各种方式,例如,引线框架120在垫板110介有导电胶或非导电胶而附着第一终端端子121,或通过超声波焊接或激光焊接而附着形成。或如图4及图5显示所示,第一终端端子121通过结合部件而附着在垫板110上,例如,在垫板110的螺栓结合孔111通过第一终端端子121的贯通孔124,并介有垫环123a和陶瓷材质的绝缘环123b而结合螺栓123,从而,固定形成。

下面,半导体芯片130构成为至少一个,被放置在配置在第一终端端子121的一端侧的垫板区域122,或如上言及所示,直接放置在垫板110上,或也能够放置在垫板110和第一终端端子121连接为一体的引线框架上(参照图6(b)及(c))。

另外,半导体芯片在引线框架120未使用另外的粘合剂,通过下面所述的加压部件140的阻焊加压附着,但并非限定于此,根据需要,半导体芯片130也能够在引线框架120上介有导电胶或非导电胶而附着。

并且,半导体芯片130不仅包括二极管,也包括:绝缘栅双极型晶体管(IGBT)、金氧半场效晶体管(MOSFET)、碳化硅(SiC)材料半导体、氮化镓(GaN)材料半导体。

下面,加压部件140至少构成一个,而层叠形成于半导体芯片130上而在结构上对半导体芯片130弹性加压,从而,固定在引线框架120,具体地固定在第一终端端子121的一端侧配置的垫板区域122。

即,加压部件140如图4及图5显示所示,按垫板区域122方向对半导体芯片130加压,而将半导体芯片130固定附着在垫板区域122,并电连接第一终端端子121和半导体芯片130。

例如,向半导体芯片130施加加压部件140的阻焊加压,而无需另外的粘合剂,电连接第一终端端子121和半导体芯片130而进行正常运行,并去除加压部件140的阻焊加压而解除第一终端端子121和半导体芯片130电连接而使无法进行正常运行,在通过半导体封装组装后的特性检查确认的组装误差或组装错误时,或半导体芯片发生破损时,将加压部件140从半导体芯片130分解,在纠正误差或错误之后或执行半导体芯片的更换之后,容易执行重新组装。

另外,如图2(a)、图5及图12显示所示,至少一个加压部件140的上端一部分形成得裸露至封装外壳150外部而由外部施加电信号,也能够将裸露的加压部件140的上端一部分向封装外壳150内侧方向或外侧方向弯曲而最终形成,其也同样适用于第一终端端子121。

具体地,如图3至图5显示所示,加压部件140包括:第一加压部件140A,其包含:加压件141,对半导体芯片130的上端弹性加压;第二终端端子142,与加压件141连接而与垫板110螺栓连接而固定,终端按垂直方向弯曲而形成,通过第一加压部件140A而对半导体芯片130进行第一次物理加压而固定并进行电连接。

例如,参照图4,第一加压部件140A在垫板110的螺栓结合孔112通过第二终端端子142的贯通孔142a而介有垫环143a和陶瓷材质的绝缘环143b而结合螺栓143而固定形成。

并且,除了第一加压部件140A之外,加压部件140还包括第二加压部件140B,而对第一加压部件140A的加压件141进行加压而对半导体芯片130进行第二次物理加压固定。其中,所述第二加压部件140B,层叠形成于第一加压部件140A的加压件141上端,而通过结合部件固定在垫板110上,而以与加压件141交叉的方向另外加压。

例如,参照图4,第二加压部件140B在垫板110的螺栓结合孔113介有垫环144a而结合螺栓144,从而,固定形成。

并且,除了如上所述的第一加压部件140A及第二加压部件140B之外,加压部件140还包括第三加压部件140C,而对第一加压部件140A的加压件141加压而对半导体芯片130进行第三次另外的物理加压而固定。其中,所述第三加压部件140C,贯通第二加压部件140B而按半导体芯片130方向对第一加压部件140A的加压件141上端另外加压,。

例如,参照图4,第三加压部件140C向形成于第二加压部件140B的中央的贯通孔145引入,而对第一加压部件140A的加压件141加压,具有弹簧而由对加压件141弹性加压的测试探针构成,或由按旋转方式加压而与贯通孔145进行螺栓结合的螺栓构成,或也能够由推动方式加压的加压部件构成。

并且,将第三加压部件140C的上端一部分裸露至封装外壳150外部而形成,对裸露至封装外壳150外部的第三加压部件140C加压而对半导体芯片130施加阻焊加压而固定。

换言之,加压部件140包括:第一加压部件140A,直接处于半导体芯片130上,以对半导体芯片130加压;一个以上另外加压部件140B、140C,对第一加压部件140A另外施加阻焊加压而完善与半导体芯片130的电连接。

因而,在半导体芯片130上端依次层叠形成如上所述的第一加压部件140A和第二加压部件140B及第三加压部件140C,对半导体芯片130加压而坚固地固定在引线框架120,由此,无需另外的粘合剂,通过加压部件的阻焊加压而附着固定,由此,与粘合剂的熔点无关,能够进行在半导体芯片130的高温环境的驱动,从而,提高耐用性。

下面,封装外壳150作为半导体电路保护用绝缘体,在垫板110上裸露第一终端端子121的上端一部分、第二终端端子142的上端一部分或第三加压部件140C的上端一部分,由EMC(环氧树脂模塑料,Epoxy Molding Compound)、PPS(聚苯硫醚,Poly PhenyleneSulfide)或PBT(聚对苯二甲酸丁二醇酯,Poly Butylene Terephtalate)材料形成,以使保护半导体芯片130。例如,封装外壳150通过传递注塑方式形成。

参照图7,对本发明的一实施例的压力式单个半导体封装的制造方法进行具体如下说明。

具体地,如图7(a)显示所示,准备形成有多个螺栓结合孔111、112、113的一个以上垫板110,如图7(b)显示所示,在垫板110上螺栓结合一个以上第一终端端子121而准备引线框架120。

后续,如图7(c)显示所示,将至少一个半导体芯片130放置在引线框架120的垫板区域122上。

此时,第一终端端子121通过各种方式附着在垫板110上,例如,引线框架120为在垫板110上介有导电胶或非导电胶而附着形成第一终端端子121,或通过超声波焊接或激光焊接而附着形成,或如图4及图5显示所示,第一终端端子121通过结合部件附着在垫板110上,例如,在垫板110的螺栓结合孔111通过第一终端端子121的贯通孔124,并介有垫环123a和陶瓷材质的绝缘环123b而结合螺栓123而固定形成。

如上言及所示,如图6(a)显示所示,在垫板110上直接附着形成第一终端端子121,在配置在第一终端端子121的一端侧的垫板区域122放置半导体芯片130,或如图6(b)显示所示,半导体芯片130与第一终端端子121分隔一定间距而放置在垫板110上,并通过形成于垫板110上的金属图案(未图示)而电连接第一终端端子121和半导体芯片130,或如图6(c)显示所示,在垫板110和第一终端端子121连接为一体的引线框架上放置半导体芯片130,由此,也能够对垫板和半导体芯片和第一终端端子的附着结构及电连接结构进行各种变形而构成。

下面,如图7(d)及(e)显示所示,为了电连接第一终端端子121和半导体芯片130,以对半导体芯片130加压的方式在半导体芯片130上层叠形成具有一个以上第二终端端子142的至少一个加压部件140A、140B、140C,对半导体芯片130加压而坚固地固定在垫板110和引线框架120之间。

最终,如图7(f)及(g)显示所示,形成于垫板110上,以裸露第一终端端子121另一端侧一部分及/或第二终端端子142的终端一部分的方式,形成保护半导体芯片130的封装外壳150。

参照,参照如下图2至图7,对本发明的一实施例的压力式单个半导体封装及其制造方法进行了说明,下面,参照图8至图10,对本发明的另一个实施例的压力式双半导体封装及其制造方法进行说明,仅对与压力式单个半导体封装对比的压力式双半导体封装的差别结构进行简单说明。

首先,对于引线框架120,垫板110构成为至少一个,而提供用于附着第一终端端子121或半导体芯片130或加压部件140的空间。

下面,如图9及图10(a)显示所示,第一终端端子121在垫板110上构成为至少一个,相对的一对进行物理分离而分别与垫板110上螺栓结合而附着。

在此,第一终端端子121另一端侧由放置半导体芯片130的第一终端端子121的一端侧垫板区域122向垂直方向弯曲而终端直立形成。

下面,如图9及图10(b)显示所示,至少一个半导体芯片130放置在各个垫板区域122上,半导体芯片130不仅包含二极管,也包含IGBT、MOSFET、SiC材料半导体、GaN材料半导体。

下面,如图9及图10(c)显示所示,加压部件140至少构成一个,按多个半导体芯片130分别层叠至上端,对半导体芯片130进行结构性弹性加压而固定在垫板区域122。

具体地,加压部件140包括:第一加压部件140A,包含加压件141,按相对的一对分离而构成为多个,对半导体芯片130的上端弹性加压;第二终端端子142,与加压件141连接而螺旋结合在垫板110上而固定,且终端按垂直方向弯曲形成,从而,通过第一加压部件140A而对半导体芯片130进行第一次物理加压而固定并电连接。

并且,如图9及图10(d)显示所示,除了第一加压部件140A之外,加压部件140还包括:第二加压部件140D,层叠形成于第一加压部件140A的加压件141上端,在垫板110上通过结合部件固定而以与加压件141交叉的方向另外加压,分别对两端的第一加压部件140A的加压件141加压而对半导体芯片130进行第二次物理加压。

例如,参照图9,第二加压部件140D在垫板110的螺栓结合孔114介有垫环146a而结合螺栓146而固定形成,并且,第二加压部件140D的两端分别对第一加压部件140A的加压件141加压。

因而,在半导体芯片130上端依次层叠第一加压部件140A和第二加压部件140D而形成,对半导体芯片130加压而坚固的固定在引线框架120,而未使用另外的粘合剂,通过加压部件的阻焊加压而附着固定,由此,与粘合剂的熔点无关,能够进行在半导体芯片130的高温环境的驱动而提高耐用性。

下面,如图9及图10(e、f)显示所示,封装外壳150在垫板110上裸露第一终端端子121的另一端侧一部分及/或第二终端端子142的终端一部分,并由EMC、PBT或PPS材料形成,以保护半导体芯片130。

另外,图11(a)为显示压力式单个半导体封装的第一加压部件140A的附图,加压件141弯曲形成,以由第二终端端子142的水平板阶梯形成,而对半导体芯片130弹性加压,(b)为显示压力式双半导体封装的第一加压部件140A的附图,各个加压件141由第二终端端子142的水平板按皱纹结构延伸形成,而对半导体芯片130分别加压,由此,在不存在另外的粘合剂的情况下,对半导体芯片130进行物理固定。

因此,通过如上所述的压力式半导体封装及其制造方法的结构,借助至少一个加压部件而对半导体芯片进行物理加压,并进行电连接,而提高半导体封装的耐用性,且简化制造工艺,不使用另外的粘合剂,而与粘合剂的熔点无关,能够进行半导体的高温环境的驱动,而提高耐用性,并在通过半导体封装组装之后的特性检查而确认的组装误差或组装错误时或半导体芯片的破损时,在纠正误差或错误后,或执行半导体芯片的更换之后,容易进行重新组装。

综上,参照附图所示的实施例而对本发明进行了说明。但本发明并非限定于此,本发明所属技术领域的普通技术人员能够进行与本发明同等范围所属范围的各种变形或其它实施例。因此,本发明的真正保护范围通过权利要求范围限定。

- 压力式半导体封装及其制造方法

- 半导体封装的制造方法、半导体封装方法和溶剂型半导体封装环氧树脂组合物