信息处理系统

文献发布时间:2023-06-19 10:06:57

技术领域

本发明涉及信息处理系统。

背景技术

以往,提出了通过将多个信息处理装置与中继装置连接来进行信息处理装置间的数据通信的信息处理系统。

进而,在信息处理系统中,还提出了在一个装置内除了多个信息处理装置之外还内置中继装置,从而在多个信息处理装置之间经由中继装置进行通信的技术。在该信息处理系统中,根据要处理的数据而包括各种类型的信息处理设备。在这样的信息处理系统中,中继装置有时在发生了故障等的情况下重新启动。在这种情况下,为了继续进行经由中继装置的通信,要求该信息处理系统内的信息处理装置配合中继装置的重新启动而进行初始化等处理。

现有技术文献

专利文献

专利文献1:日本特开2005-275818号公报

专利文献2:日本特开2007-274375号公报

发明内容

发明要解决的问题

但是,在信息处理系统中,由于包含支持/不支持热插拔(例如HPD(Hot PlugDetect))等的各种信息处理装置,所以在中继装置重新启动的情况下,需要进行与信息处理装置相应的处理。

本发明是鉴于上述问题而完成的,其目的在于,在信息处理装置之间继续进行经由中继装置的通信。

用于解决问题的手段

根据本发明的第1方面的信息处理系统经由中继装置将第1信息处理装置和多个第2信息处理装置连接成可通信,所述第1信息处理装置具有与作为电源接通时的插拔的热插拔对应的第1连接部。所述第2信息处理装置具有:第2连接部,其与所述中继装置连接;以及第1重新启动部,其执行所述第2信息处理装置的重新启动。所述中继装置具有:电源控制单元,其在所述中继装置重新启动时也向所述第1信息处理装置及所述第2信息处理装置供给电力;以及第2重新启动部,其在检测出通信故障的情况下重新启动所述中继装置。所述第1信息处理装置具有:与所述中继装置连接的所述第1连接部;第1检测部,其检测重新启动的所述中继装置;以及初始化部,在所述第1检测部检测到所述中继装置的情况下,所述初始化部对与经由所述中继装置的通信相关的设定进行初始化。

发明效果

本发明的信息处理系统具有防止不能进行经由中继装置的通信的效果。

附图说明

图1是表示本实施例的中继装置内置计算机的整体结构的一例的图。

图2是表示中继装置内置计算机的各装置的硬件结构的一例的图。

图3是表示电源控制单元的硬件结构的一例的图。

图4是用于说明本实施例的平台间的通信处理的一例的图。

图5是表示中继装置内置计算机所具有的各部的功能的一例的功能框图。

图6是表示本实施例的恢复处理的一例的时序图。

具体实施方式

以下,基于附图详细说明本发明的信息处理系统的实施例。另外,并不是利用该实施例来限定本发明

【实施例1】

图1是表示本实施例的中继装置内置计算机1的整体结构的一例的图。中继装置内置计算机1是将具有与电源接通时的插拔即热插拔对应的接口的平台(platform)10-1和多个平台10-2~10-8经由中继装置30连接成可通信的信息处理系统。如图1所示,实施例的中继装置内置计算机1具备平台10-1~10-8和中继装置30。

平台10-1~10-8经由中继装置30连接成可通信。平台10-1~10-8例如插入到设置有中继装置30的板上的插槽(slot)中。另外,多个插槽中的任意一个插槽也可以是未插入有平台10-1~10-8的空闲状态。在以下的说明中,在不需要区分各平台10-1~10-8而表示任意平台10-1~10-8的情况下,记载为平台10。

平台10-1是第1信息处理装置的一例。平台10-1是管理平台10-2~10-8并使平台10-2~10-8执行各种处理的主(main)信息处理装置。

在平台10-1连接有监视器21和输入装置22。监视器21显示例如液晶显示装置等的各种画面。输入装置22接受例如键盘或鼠标等的各种操作。

平台10-2~10-8是第2信息处理装置的一例。平台10-2~10-8是根据平台10-1的请求,执行例如AI(Artificial Intelligence,人工智能)推理处理或图像处理等的子(sub)信息处理装置。另外,平台10-2~10-8可以各自具有不同的功能,也可以按照每多个平台10而具有功能。

平台10-1~10-8具有能够作为主机侧进行工作的根复合体(RC:Root Complex)11-1~11-8。在以下说明中,在不需要区分各根复合体11-1~11-8而表示任意的根复合体11-1~11-8的情况下,记载为根复合体11。

根复合体11执行与中继装置30的各端点(end point)31-1~31-8的通信。即,平台10和中继装置30通过PCIe(Peripheral Component Interconnect Express,周边装置互联高速)等通信标准连接成可通信。平台10和中继装置30不限于PCIe,也可以通过其他通信标准连接。

中继装置30具有多个端点(EP:End Point)31-1~31-8。另外,中继装置30对具有与端点31-1~31-8连接的根复合体11的多个平台10之间的通信进行中继。

端点31-1~31-8执行与平台10的根复合体11的通信。在以下说明中,在不需要区分各端点31-1~31-8而表示任意的端点31-1~31-8的情况下,记载为端点31。

接着,对中继装置内置计算机1的各装置的硬件结构进行说明。图2是表示中继装置内置计算机1的各装置的硬件结构的一例的图。在此,以平台10-1的硬件结构为例进行说明。但是,平台10-2~10-8也是同样结构。

平台10-1是进行AI处理或图像处理等运算处理的计算机。平台10具备根复合体11-1、处理器12-1、存储器(memory)13-1、存储部14-1和通信部15-1。另外,它们经由总线连接成可通信。

处理器12-1控制整个平台10-1。处理器12-1可以是多处理器。另外,处理器12-1例如是CPU(中央处理单元,Central Processing Unit)、MPU(微处理单元,Micro ProcessingUnit)、GPU(图形处理单元,Graphics Processing Unit)、DSP(数字信号处理器,DigitalSignal Processor)、ASIC(特定应用集成电路,Application Specific IntegratedCircuit)、PLD(可编程逻辑器件,Programmable Logic Device)、FPGA(场可编程门阵列,Field Programmable Gate Array)中的任意一个。另外,处理器12也可以是CPU、MPU、GPU、DSP、ASIC、PLD、FPGA中的2种以上的要素的组合。在以下说明中,在不需要区分处理器12-1~12-8而表示任意的处理器12-1~12-8的情况下,记载为处理器12。

存储器13-1是包括ROM(只读存储器)和RAM(随机存取存储器)的存储器。在存储器13-1的ROM中写入有各种软件程序、该程序用的数据类。存储器13-1上的软件程序被CPU 12适当地读入并执行。此外,存储器13-1的RAM被用作易失性存储器或工作存储器。在以下说明中,在不需要区别存储器13-1~13-8而表示任意的存储器13-1~13-8的情况下,记载为存储器13。

存储部14-1是硬盘驱动器(Hard Disk Drive:HDD)、SSD(固态驱动器,SolidState Drive)、存储类存储器(Storage Class Memory:SCM)等存储装置,用于存储各种数据。例如,在存储部14-1中存储各种软件程序。在以下说明中,在不需要区别存储部14-1~14-8而表示任意的存储部14-1~14-8的情况下,记载为存储部14。

在平台10中,处理器12通过执行存储在存储器13或存储部14中的软件程序来实现各种功能。

另外,上述各种软件程序不一定必须存储在存储器13或存储部14中。例如,平台10也可以读出存储在介质读取装置等可读取的存储介质中的程序并执行。平台10可读取的存储介质例如对应于CD-ROM或DVD盘、USB(通用串行总线)存储器等可移动型记录介质、闪存等半导体存储器、硬盘驱动器等。另外,也可以使与公用线路、因特网、LAN等连接的装置存储该信息处理程序,平台10从它们中读出信息处理程序并执行。

通信部15-1是用于执行与电源控制单元40通信的接口。例如,通信部15-1根据I2C(内置集成电路,Inter-Integrated Circuit)等通信标准来执行通信。在以下说明中,在不需要区分通信部15-1~15-8而表示任意的通信部15-1~15-8的情况下,记载为通信部15。

接着,对中继装置30进行说明。中继装置30具备针对每个平台10设置的端点31-1~31-8、处理器32、存储器33、存储部34、内部总线35、PCIe总线36和电源控制单元40。在以下说明中,在不需要区分各端点31-1~31-8而表示任意的端点31-1~31-8的情况下,记载为端点31。

端点31针对每个平台10设置,执行数据的发送接收。例如,在从所连接的平台10接收到数据的情况下,端点31经由PCIe总线36向与发送目的地的平台10连接的端点31发送所接收的数据。

例如,根复合体11通过DMA(直接存储器存取,Direct Memory Access)传输向其他平台10发送数据。另外,端点31在经由PCIe总线36从与数据的发送源的平台10连接的端点31接收到数据的情况下,向所连接的平台10发送接收到的数据。

处理器32控制中继装置30整体。处理器32可以是多处理器。另外,处理器32例如可以是CPU、MPU、GPU、DSP、ASIC、PLD、FPGA中的任意一个。另外,处理器32也可以是CPU、MPU、GPU、DSP、ASIC、PLD、FPGA中的2种以上的要素的组合。

存储器33是包括ROM和RAM的存储装置。在ROM中写入有各种软件程序和该程序用的数据类。存储在存储器33中的程序被读取到处理器32中并被执行。此外,RAM被用作工作存储器。

存储部34是硬盘驱动器、SSD、存储类存储器等存储装置,存储各种数据。例如,在存储部34中存储各种软件程序。

内部总线35与处理器32、存储器33、存储部34及PCIe总线36连接成可通信。

PCIe总线36与多个端点31和内部总线35连接成可通信。即,PCIe总线36连接成能够在多个端点31间传送数据。另外,PCIe总线36例如是基于PCIe标准的总线。

电源控制单元40控制向平台10的电力供应。电源控制单元40例如是被称为微型计算机或微控制器的集成电路。电源控制单元40在中继装置30重新启动时也向平台10供给电力。另外,电源控制单元40与平台10-1以及中继装置30的处理器32连接。

接着,对电源控制单元40的硬件结构进行说明。图3是表示电源控制单元40的硬件结构的一例的图。

电源控制单元40包括处理器41、存储器42、第1连接部43和第2连接部44。处理器41、存储器42、第1连接部43和第2连接部44经由总线45连接成可通信。

处理器41控制电源控制单元40整体。处理器41可以是多处理器。另外,处理器41例如可以是CPU、MPU、GPU、DSP、ASIC、PLD、FPGA中的任意一个。另外,处理器41也可以是CPU、MPU、GPU、DSP、ASIC、PLD、FPGA中的2种以上的要素的组合。

存储器42是包括ROM和RAM的存储装置。在ROM中写入有各种软件程序和该程序用的数据类。存储在存储器42中的程序被读取到处理器41中并被执行。此外,RAM被用作工作存储器。

第1连接部43是用于与平台10-1连接的接口。例如,第1连接部43是I2C等接口。

第2连接部44是用于与中继装置30的处理器32连接的接口。例如,第2连接部44经由GPIO(通用输入输出,General Purpose Input Output)连接。

接着,对与中继装置30连接的平台10-1和平台10-2之间的通信处理的一例进行说明。图4是用于说明本实施例的平台10间的通信处理的一例的图。在此,对平台10-1与平台10-2间的通信处理的一例进行了说明,其他平台10间也同样地进行通信。

如图4所示,中继装置内置计算机1例如具有由PCIe的标准规定的层构造。而且,中继装置内置计算机1经由各层来执行平台10间的通信。

发送源的平台10-1将软件所指定的数据经由事务层、数据链路层以及物理层(PHY)传送到中继装置30的物理层(PHY)。

中继装置30将从发送源的平台10-1传送来的数据经由物理层(PHY)以及数据链路层传递给事务层。中继装置30在事务层中,通过隧道(tunneling)将数据传送到与发送目地的平台10-2对应的端点31。中继装置30经由事务层、数据链路层及物理层(PHY)向发送目的地的平台10-2的物理层(PHY)传送。这样,中继装置30通过在端点31之间使数据通过隧道传输,从发送源的平台10-1向发送目的地的平台10-2传送数据。

在发送目的地的平台10-2中,数据经由物理层(PHY)、数据链路层和事务层被传递到软件。

另外,在数据的传送没有集中于与中继装置30连接的多个平台10中的一个平台10的情况下,能够在不同的任意组合的平台10之间并行地传送数据。

例如,在平台10-2及平台10-3与平台10-1通信的情况下,中继装置30通过串行处理执行与平台10-2和平台10-3的通信。另一方面,在不同的平台10之间进行通信且通信不集中于特定的平台10的情况下,中继装置30通过并行处理来执行平台10之间的通信。

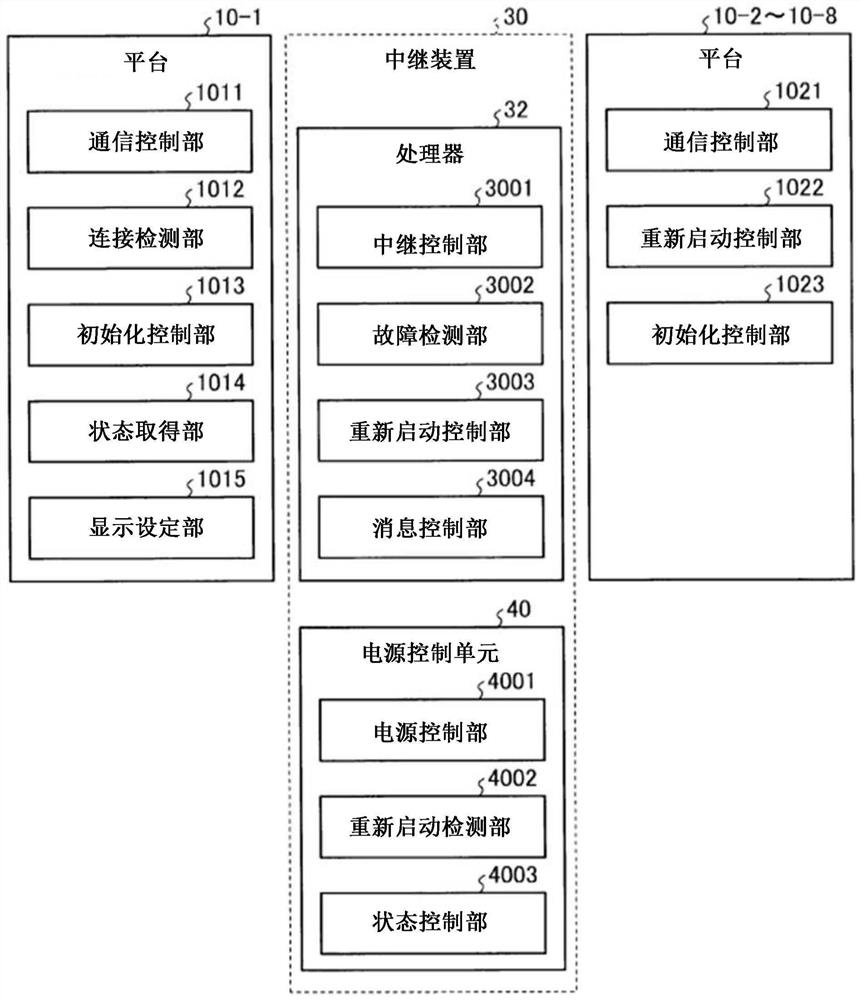

接着,对本实施方式的中继装置内置计算机1所具有的各部的特征性功能进行说明。图5是表示中继装置内置计算机1所具有的各部的功能的一例的功能框图。

首先,对平台10-1进行说明。

平台10-1的处理器12-1通过执行存储在存储器13-1、存储部14-1等中的程序来实现图5所示的功能。具体而言,处理器12-1具备通信控制部1011、连接检测部1012、初始化控制部1013、状态取得部1014及显示设定部1015作为功能部。

通信控制部1011是第1连接部的一例。通信控制部1011控制根复合体11-1,执行经由中继装置30的与平台10-2~10-8的通信。即,通信控制部1011与中继装置30连接。而且,通信控制部1011对中继装置30执行数据的发送接收。另外,平台10-1被设定为在系统BIOS(System BIOS(Basic Input Output System,基础输入输出系统))中支持HPD的设备。即,通信控制部1011支持电源接通时的插拔即热插拔。因此,平台10-1即使在电源接通时被插拔,也能够执行与中继装置30的通信。

连接检测部1012是第1检测部的一例。连接检测部1012检测中继装置30被连接的情况。例如,在中继装置30重新启动的情况下,连接检测部1012检测重新启动的中继装置30。

初始化控制部1013是初始化部的一例。初始化控制部1013在连接检测部1012检测到中继装置30的情况下,对与经由中继装置30的通信相关的设定进行初始化。更详细地说,初始化控制部1013在BIOS中检测出连接了中继装置30的情况下,对各种设定进行初始化。例如,初始化控制部1013对BAR(Base Address Register,基础地址寄存器)、中断寄存器、其他寄存器等进行初始化。

状态取得部1014获取表示中继装置30已重新启动的信息。更详细地说,状态取得部1014控制通信部15-1,向电源控制单元40请求表示中继装置30被重新启动的“ErrorStatus”。然后,状态取得部1014取得从中继装置30作为响应而发送的“Error Status”。

显示设定部1015是设定变更部的一例。显示设定部1015将用于切换是否切断平台10与中继装置30的连接的显示变更为非显示设定。例如,当在例如Windows(注册商标)的任务栏的“硬件的卸载”中输入了用于切断平台10与中继装置30的连接的操作时,切断平台10与中继装置30的连接。在这种情况下,由于平台10和中继装置30被切断,所以不能继续通信。因此,显示设定部1015在驱动程序内经由KMDF(Kernel-Mode Driver Framework,内核模式驱动框架)的API(Application Programming Interface,应用编程接口)变更注册表的值,从而变更为非显示。

另外,在Windows(注册商标)的控制面板的“设备和打印机”中,平台10和中继装置30的连接也被切断。因此,显示设定部1015通过在INF文件中直接改写注册表的值来变更为非显示。由此,显示设定部1015防止平台10与中继装置30的连接被切断。即,显示设定部1015能够使经由中继装置30的通信继续。

接着,对中继装置30进行说明。

中继装置30的处理器32通过执行存储在存储器33、存储部34等中的程序来实现图5所示的功能。具体而言,处理器32具备中继控制部3001、故障检测部3002、重新启动控制部3003及消息控制部3004作为功能部。

中继控制部3001控制平台10之间的通信。更详细地说,中继控制部3001如图4所示,控制平台10之间的数据传送。

故障检测部3002检测出平台10之间的通信发生了故障。例如,在规定期间内未进行通信的情况下,故障检测部3002检测为发生了故障。

重新启动控制部3003是第2重新启动部的一例。重新启动控制部3003在故障检测部3002检测出通信故障的情况下重新启动中继装置30。

消息控制部3004是通知部的一例。消息控制部3004将中继装置30重新启动的情况通知给平台10-1~10-8。更详细地说,消息控制部3004在中继装置30的重新启动完成的情况下,将表示进行了重新启动的信息发送到平台10-1~10-8。例如,消息控制部3004在PCIe的Linkup时向平台10-1~10-8发送“DRS(Device Readiness Status,设备就绪状态)消息(Message)”。

接着,对电源控制单元40进行说明。

电源控制单元40的处理器41通过执行存储在存储器42等中的程序来实现图5所示的功能。具体而言,处理器41具备电源控制部4001、重新启动检测部4002及状态控制部4003作为功能部。

电源控制部4001控制向平台10的电力供应。另外,电源控制部4001在中继装置30重新启动时也向平台10供给电力。

重新启动检测部4002是第2检测部的一例。重新启动检测部4002检测中继装置30重新启动的情况。更详细地说,重新启动检测部4002经由第2连接部44接收表示中继装置30已重新启动的信息。例如,重新启动检测部4002经由GPIO接收表示在FW(Firm Ware,固件)启动时中继装置30进行了重新启动的标记(flag)。

状态控制部4003在经由第1连接部43被请求了表示中继装置30进行了重新启动的信息的情况下,发送表示中继装置30的状态变化的信息。即,状态控制部4003在经由I2C被请求了表示中继装置30进行了重新启动的“Error Status”的情况下,作为响应而发送“Error Status”。

接着,对平台10-2~10-8进行说明。

平台10-2~10-8的处理器12-2~12-8通过执行存储在存储器13-2~13-8或存储部14-2~14-8等中的程序,实现图5所示的功能。具体而言,处理器12-2~12-8具备通信控制部1021、重新启动控制部1022及初始化控制部1023作为功能部。

通信控制部1021是第2连接部的一例。通信控制部1021控制根复合体11-2~11-8,经由中继装置30执行与平台10的通信。即,通信控制部1021与中继装置30连接。然后,通信控制部1021对中继装置30执行数据的发送接收。

重新启动控制部1022是第1重新启动部的一例。重新启动控制部1022执行平台10-2~10-8的重新启动。更详细地说,重新启动控制部1022在作为本装置的平台10-2~10-8发生了故障等的情况下,重新启动作为本装置的平台10-2~10-8。

初始化控制部1023随着平台10-2~10-8的重新启动,对平台10-2~10-8进行初始化。更详细地说,初始化控制部1023加载驱动器。另外,初始化控制部1023进行BAR等的寄存器初始化,分配“Base Address(基础地址)”。

接着,对恢复处理进行说明图6是示出根据本实施例的恢复处理的一例的时序图。恢复处理是在经由中继装置30的通信中,从通信故障中恢复的处理。

中继装置内置计算机1的各部成为工作状态(步骤S1)。

中继装置内置计算机1的各部执行经由中继装置30的通信(步骤S2)。例如,发送源的平台10-1的通信控制部1011指定发送目的地的平台10-2~10-8,将发送数据发送到中继装置30。设置在中继装置30中的处理器32的中继控制部3001将发送数据发送到被指定的平台10-2~10-8。发送目的地的平台10-2~10-8的通信控制部1021接收发送数据。

处理器32的故障检测部3002生成“Bus Fault(总线故障)”(步骤S3)。即,故障检测部3002检测出在PCIe总线36中发生通信故障。

处理器32的故障检测部3002将“Bus Transaction Error(总线事务处理故障)”发送到平台10-1(步骤S4)。即,故障检测部3002发送在平台10之间的通信中发生了错误的情况。

处理器32的重新启动控制部3003重新启动本装置(步骤S5)。重新启动控制部3003初始化各种设定(步骤S6)。

处理器32的重新启动控制部3003在步骤S6的重新启动中完成了启动的情况下,发送启动完成通知(步骤S7)。更详细地说,重新启动控制部3003使启动完成信号有效,发送启动完成通知。

处理器32的消息控制部3004设定“DRS消息”(步骤S8)。即,消息控制部3004生成表示中继装置30仅写了重新启动的信息。

电源控制单元40的重新启动检测部4002基于启动完成通知,检测处理器32的重新启动(步骤S9)。另外,电源控制单元40的重新启动检测部4002向平台10-2~10-8发送处理器32的重新启动的检测通知(步骤S10)。

处理器32的重新启动控制部3003结束启动完成通知的发送(步骤S11)。更详细地说,重新启动控制部3003使启动完成信号无效,结束启动完成通知的发送。

平台10-1和中继装置30成为“PCIe上行链路(Link up)”(步骤S12)。即,平台10-1和中继装置30连接成能够在PCIe中通信。

处理器32的消息控制部3004发布“DRS消息”(步骤S13)。即,消息控制部3004向平台10发送表示中继装置30进行了重新启动的信息。

平台10-1的连接检测部1012随着处理器32的重新启动完成,检测中继装置30被连接的情况(步骤S14)。

平台10-1的初始化控制部1013执行BIOS的初始化(步骤S15)。即,初始化控制部1013对寄存器等进行初始化并分配“基础地址(Base Address)”。

平台10-1的初始化控制部1013执行驱动器的初始化(步骤S16)。

平台10-2~10-8的重新启动控制部1022在检测到处理器32的重新启动的情况下,开始重新启动本装置的处理(步骤S17)。例如,在本装置发生了通信故障等的情况下,重新启动控制部1022执行重新启动。

平台10-2~10-8的重新启动控制部1022随着步骤S3的重新启动而启动(步骤S18)。

平台10-2~10-8的初始化控制部1023加载驱动器(步骤S19)。初始化控制部1023执行寄存器等的初始化(步骤S20)。即,初始化控制部1023分配“基础地址(BaseAddress)”。

中继装置30和平台10-2~10-8成为“PCIe上行链路(Link up)”(步骤S21)。即,平台10-2~10-8和中继装置30连接成能够在PCIe中通信。

处理器32的消息控制部3004发布“DRS消息”(步骤S22)。

中继装置内置计算机1的各部成为工作状态(步骤S23)。

平台10-1的状态取得部1014请求“故障状态(Error Status)”(步骤S24)。

电源控制单元40的状态控制部4003发送“故障状态(Error Status)”作为“故障状态(Error Status)”请求的响应(步骤S25)。

如上所述,本实施例的中继装置内置计算机1经由中继装置30与平台10-1~10-8连接成能够通信。平台10-1~10-8中的至少平台10-1支持HPD。然而,平台10-2~10-8中的任何一个不支持HPD。在这样的情况下,例如当由于平台10-2~10-8重新启动而在经由中继装置30的通信中发生故障时,中继装置30重新启动本装置。由此,产生平台10与中继装置30的连接被热插拔那样的状态。平台10-1在检测到中继装置30的重新启动的情况下,初始化驱动器或寄存器值等与经由中继装置30的通信相关的设定。由此,中继装置内置计算机1能够在不使平台10-1重新启动的情况下进行经由中继装置30的通信。因此,内置中继装置计算机1能够继续进行经由中继装置30的通信。

在上述实施方式中,作为各部的总线(例如,扩展总线)或I/O接口,以PCIe为例进行了说明,但总线或I/O接口不限于PCIe。例如,各部的总线或I/O接口是能够通过数据传输总线在设备(周边控制控制器)与处理器之间进行数据传输的技术即可。数据传输总线可以是能够在设置于一个壳体等的本地环境(例如,一个系统或一个装置)中高速地传输数据的通用总线。I/O接口可以是并行接口和串行接口中的任意一方。

在串行传输的情况下,I/O接口只要能够执行点对点连接并具有能够利用分组来传输数据的结构即可。另外,在串行传输的情况下,I/O接口可以具有多个通道(lane)。I/O接口的层结构还可以具有进行分组的生成和解码的事务(transaction)层、进行错误检测等的数据链路层和对串行和并行进行转换的物理层。I/O接口还可以包括具有一个或多个端口且层级最高的根复合体、作为I/O设备的端点、用于增加端口的交换机(switch)以及用于转换协议的桥接器等在内。I/O接口也可以通过多路复用器对要发送的数据和时钟信号进行复用并发送。在这样的情况下,接收侧也可以通过解复用器来分离数据和时钟信号。

标号说明

1中继装置内置计算机

10平台

30中继装置

40电源控制单元

1011、1021通信控制部

1012连接检测部

1013、1023初始化控制部

1014状态取得部

1015显示设定部

3001中继控制部

3002故障检测部

1022、3003重新启动控制部

3004消息控制部

4001电源控制部

4002重新启动检测部

4003状态控制部

- 细胞观察信息处理系统、细胞观察信息处理方法、细胞观察信息处理程序、细胞观察信息处理系统具有的记录部和细胞观察信息处理系统具有的装置

- 服务器装置、信息处理系统、介质以及信息处理系统的工作方法