一种超宽频带低杂散双锁相环频率源

文献发布时间:2023-06-19 10:11:51

技术领域

本发明涉及一种频率源设计技术,尤其涉及一种超宽频带低杂散双锁相环频率源。

背景技术

在电子系统中,时钟相当于系统的心脏,时钟信号的性能直接影响系统的性能及稳定性。随着电子技术的发展,对于时钟信号的性能要求越来越高,所以频率源在电子通信系统中的作用越来越重要。在雷达通信、无线通信、微波测试设备和频谱监测等系统的射频前端中,都需要使用宽频带、低杂散、低相位噪声的微波频率源来提高系统的抗干扰能力以及通信的保密能力。随着大量微波测试设备厂商的产品不断更新发展,信号源、频谱分析仪、矢量网络分析仪等射频微波测试设备的测试项目测试精度不断提高,对频率源的各方面指标的要求也越来越高。因此,研究宽频带、低相噪、低杂散的频率源是微波技术发展的必然,其现实应用的意义也愈发明显。

频率源从最初的运用晶体振荡器的加减乘除运算来实现几个频率,到现在使用较为广泛的是直接频率合成技术(DDS)和锁相环技术(PLL)。随着这些技术的使用,现有的频率源可基本实现不同频带以及低相噪的各种需求,但同时也伴随着一些问题,比如杂散问题。而一般情况下,单一的频率合成技术,不管是DDS还是锁相环都只能依靠在频率源中选择特定的频率点来规避杂散或者使用滤波器来虑除杂散。所以,在使用这些技术的同时要合理设计方案,综合考虑频率源的指标需求,在满足设计需求的前提下,通过一些指标的牺牲来平衡其他指标的参数,以使得频率源的最终输出指标满足系统设计需求。

发明内容

本发明的目的是提供一种超宽频带低杂散双锁相环频率源。

本发明的目的是通过以下技术方案实现的:

本发明的超宽频带低杂散双锁相环频率源,包括参考时钟信号、第一级锁相环部分、滤波部分、第二级锁相环部分;

所述参考时钟信号用于向第一级锁相环部分提供参考信号;

所述一级锁相环部分根据参考时钟信号及第二级锁相环的输出频率进行频率计算,选出与第二级锁相环输出频率相应的低杂散、低噪声频率;

所述滤波部分对第一级锁相环部分输出的低杂散频点进行窄带滤波,滤波后信号可作为第二级锁相环的参考信号;

所述第二级锁相环部分根据前级提供的参考信号进行宽带调频,获得低杂散、低噪声的超宽带信号。

由上述本发明提供的技术方案可以看出,本发明实施例提供的超宽频带低杂散双锁相环频率源,通过第一级和第二级锁相环的配合很好的实现了低杂散、低相噪、宽频带的设计目标,可以有效改善杂散指标,同时电路设计简单易实现,并可提高系统的可靠性,有极好的经济效益和应用前景。

附图说明

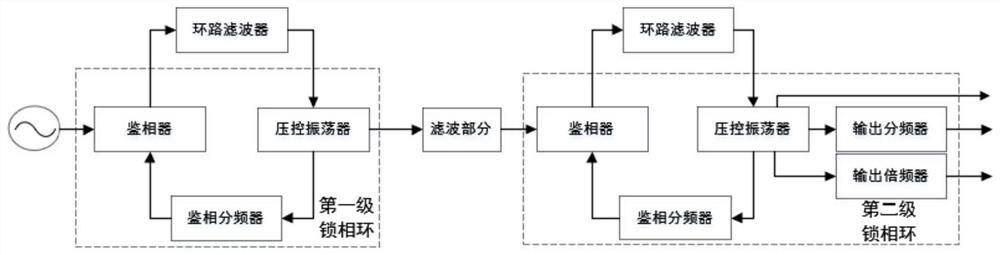

图1为本发明实施例提供的超宽频带低杂散双锁相环频率源结构示意图。

图2为本发明实施例第一级锁相环路部分的结构框图。

图3为本发明实施例的椭圆滤波器电路图。

图4为本发明实施例椭圆滤波器电路S参数仿真曲线。

图5为本发明实施例第二级锁相环路部分的结构框图。

图6为本发明实施例第二级锁相环整个VCO输出频段的杂散仿真结果图。

图7为本发明实施例第二级锁相环输出的相噪仿真结果图。

图8为本发明实施例第二级锁相环N值仿真结果图。

图9为本发明实施例第二级锁相环输出频率对应N/M及电荷泵电流计算结果图。

具体实施方式

下面将对本发明实施例作进一步地详细描述。本发明实施例中未作详细描述的内容属于本领域专业技术人员公知的现有技术。

本发明的超宽频带低杂散双锁相环频率源,其较佳的具体实施方式是:

包括参考时钟信号、第一级锁相环部分、滤波部分、第二级锁相环部分;

所述参考时钟信号用于向第一级锁相环部分提供参考信号;

所述一级锁相环部分根据参考时钟信号及第二级锁相环的输出频率进行频率计算,选出与第二级锁相环输出频率相应的低杂散、低噪声频率;

所述滤波部分对第一级锁相环部分输出的低杂散频点进行窄带滤波,滤波后信号可作为第二级锁相环的参考信号;

所述第二级锁相环部分根据前级提供的参考信号进行宽带调频,获得低杂散、低噪声的超宽带信号。

所述第一级锁相环部分为内置压控振荡器(VCO)的锁相环,锁相环芯片电荷泵输出后与三阶无源环路滤波器相连,从而将参考时钟信号转化为平均电压信号输出,然后锁相环内部的压控振荡器(VCO)根据平均电压信号生成对应的频率信号。

所述参考时钟信号为恒温晶振,所述晶体振荡器提供的参考信号为100MHz参考信号,所述第一级锁相环部分选频后输出270MHz至300MHz的低杂散、低相噪频率信号。

所述滤波部分为根据第一级锁相环输出信号频率设计的窄带带通滤波器,第一级锁相环部分选出的频点经滤波器滤波后生成第二级锁相环部分参考信号。

所述第二级锁相环部分为内置压控振荡器(VCO)的超宽带低噪声锁相环,锁相环芯片电荷泵输出后与三阶无源环路滤波器相连,从而将滤波部分输入的参考信号转化为平均电压信号输出,然后锁相环内部的压控振荡器(VCO)根据平均电压信号生成对应的频率信号,最终锁相环根据输出频点设置内部的分频及倍频电路,输出最终设置的频率。

所述第二级锁相环采用LMX2595芯片。

所述第一级锁相环采用HMC830芯片。

所述频率计算使用ADI公司的设计软件ADIsimFrequencyPlanner。

本发明的超宽频带低杂散双锁相环频率源,通过第一级和第二级锁相环的配合很好的实现了低杂散、低相噪、宽频带的设计目标,可以有效改善杂散指标,同时电路设计简单易实现,并可提高系统的可靠性,有极好的经济效益和应用前景。

本发明中:

选定两级锁相环具体型号后,根据输出频带及第二级锁相环特性选定第一级锁相环输出频率范围为270MHz~300MHz;然后使用ADI公司的设计软件ADIsimFrequencyPlanner进行频点计算,选定第二级锁相环不同频点输出对应的鉴相分频因数N、对应的第一级锁相环鉴相分频因数M以及相应的电荷泵电,根据结果进行第一级、第二级锁相环的配置。

本发明选用的锁相环为内置VCO的锁相环,减小外部电路布局对锁相环相噪的恶化,环路为无源环路滤波器,可以避免环路滤波中有源器件引入噪声导致的相噪恶化。

晶体振荡器为高稳定度的恒温晶振,输出频率为100MHz,相位噪声达到-155dBc/Hz@1kHz。所述晶体振荡器提供的参考信号为100MHz参考信号,所述第一级锁相环部分选频后输出270MHz至300MHz的低杂散频率信号。

滤波部分为根据第一级锁相环输出信号频率设计的窄带带通滤波器,第一级锁相环部分选出的频点经滤波器滤波后生成第二级锁相环部分参考信号。

第二级锁相环部分为内置压控振荡器(VCO)的超宽带低噪声锁相环;所述锁相环芯片电荷泵输出后与三阶有源环路滤波器相连,从而将滤波部分输入的参考信号转化为平均电压信号输出;然后锁相环内部的VCO根据平均电压信号生成对应的频率信号;第二级锁相环的输入参考频率根据ADIsimFrequencyPlanner中的计算结果进行设置,在不同频率输出选取相应的鉴相频率,将整数边缘杂散等杂散信号有效降低。

第一级锁相环采用Hittite的低相位噪声锁相环芯片HMC830,HMC830具有小数分频的功能,可以实现最小3Hz的分辨率。它还具有优秀的低相位噪声性能,在小数分频输出300MHz,鉴相频率为50MHz的情况下,相位噪声可达到-110dBc/Hz@1kHz、-110dBc/Hz@10kHz、-120dBc/Hz@100kHz。

第二级锁相环芯片采用TI的低相位噪声锁相环芯片LMX2595。它具有小数分频的功能,在鉴相为300MHz时,可以实现最小0.1Hz的极小分辨率。它还具有优秀的低相位噪声性能,在闭环模式下鉴相200MHz、18GHz输出时相位噪声可达到-93dBc/Hz@1kHz、-98dBc/Hz@100kHz。在设计中结合第二级锁相环的性能,计算出相应的参考输入频率,可有效降低输出频率的整数边界杂散以及其他类型杂散,使得锁相环输出实现低杂散的效果。

本发明的有益效果:

(1)本发明通过第一级和第二级锁相环的配合,可有效的改善锁相环的整数边缘杂散,改善杂散指标,提高系统的可靠性,有极好的经济效益和应用前景,特别适用于需要宽频带、小频率步进的军用雷达、无线通信和电子侦测以及电子对抗等通信系统。

(2)本发明第一级锁相环主要进行参考时钟的变频选频,选择出锁定后性能指标最好且作为第二级锁相环的参考信号可降低第二级锁相环输出杂散的频点,然后经过滤波作为第二级锁相环的参考信号。第二级锁相环主要根据输出的参考信号,变频输出宽频带的输出信号。

(3)本发明第一级锁相环采用Hittite的低相位噪声锁相环芯片HMC830,在小数分频输出300MHz,鉴相频率为50MHz的情况下,相位噪声可达到-110dBc/Hz@1kHz、-110dBc/Hz@10kHz、-120dBc/Hz@100kHz,可有效的保障为第二级锁相环提供的参考信号的频率准确度以及相位噪声需求;第二级锁相环芯片采用TI的低相位噪声锁相环芯片LMX2595。它具有小数分频的功能,在鉴相为300MHz时,可以实现最小0.1Hz的极小分辨率。它还具有优秀的低相位噪声性能,在闭环模式下鉴相200MHz、18GHz输出时相位噪声可达到-93dBc/Hz@1kHz、-98dBc/Hz@100kHz。

(4)本发明第一级锁相环输出频率即第二级锁相环的参考信号频率,都通过ADIsimFrequencyPlanner的杂散计算确定,可保证有效降低输出频率的整数边界杂散以及其他类型杂散,使得锁相环输出实现低杂散的效果。第一级锁相环输出添加带通滤波器,可有效滤除所需信号的谐波以及无用的杂散信号,降低为第二级锁相环作为参考信号所带来的杂散影响及风险。

具体实施例:

如图1所示,发明提供的一种超宽频带低杂散双锁相环频率源,其主要参考时钟信号、第一级锁相环部分、滤波部分、第二级锁相环部分组成;参考时钟信号用于向第一级锁相环部分提供参考信号;一级锁相环部分根据参考时钟信号及第二级锁相环的输出频率进行选频;滤波部分对第一级锁相环部分输出的低杂散频点进行窄带滤波,滤波后信号可作为第二级锁相环的参考信号;第二级锁相环部分根据前级提供的参考信号进行宽带调频,获得低杂散的宽带信号。

本发明综合考虑成本和性能,第一级锁相环采用Hittite的低相位噪声锁相环芯片HMC830,HMC830具有小数分频的功能,可以实现最小3Hz的分辨率。它还具有优秀的低相位噪声性能,在小数分频输出300MHz,鉴相频率为50MHz的情况下,相位噪声可达到-110dBc/Hz@1kHz、-110dBc/Hz@10kHz、-120dBc/Hz@100kHz。第二级锁相环芯片采用TI的低相位噪声锁相环芯片LMX2595。它具有小数分频的功能,在鉴相为300MHz时,可以实现最小0.1Hz的极小分辨率。它还具有优秀的低相位噪声性能,在闭环模式下鉴相200MHz、18GHz输出时相位噪声可达到-93dBc/Hz@1kHz、-98dBc/Hz@100kHz。在设计中结合第二级锁相环的性能,计算出相应的参考输入频率,可有效降低输出频率的整数边界杂散以及其他类型杂散,使得锁相环输出实现低杂散的效果。

(1)第一级锁相环设计

第一级锁相环的结构框图如图2所示,参考时钟信号部分的100MHz作为第一级锁相环部分的基准频率。此100MHz参考信号是整个频率源电路的时钟基准,因此对它的性能要求很高。

本发明在设计时,第一级锁相环为内置VCO的锁相环,工作模式选择小数分频模式和电荷泵输出。鉴相器的电荷泵输出后与低通滤波器相连,从而将参考信号转化为平均电压输出,此平均电压一般是通过低通滤波器的电容进行电荷积累产生,并且低通滤波器同时对噪声及鉴相输出的纹波等干扰进行抑制。电荷泵输出和鉴相器直接输出不同,它把输出转化为误差电流而不是误差电压,具有低功耗、高速、低抖动等优秀特点。由于此锁相环为内置VCO的锁相环,不存在鉴相电压不能满足VCO电压控制范围的问题,所有可以使用无源的环路滤波,从而避免使用有缘环路滤波器对电路相噪的影响;而高阶环路滤波器可在保证相同的鉴相杂散抑制的同时,可以允许更宽的环路带宽和更高的鉴相频率,降低了分频比,从而改善锁相环的带内相位噪声性能,因此第一级锁相环路采用三阶无源环路滤波器。

提高鉴相频率整体可降低锁相环的相位噪声,HMC830的最高鉴相频率为100MHz,但考虑到最高鉴相易出现失锁等问题,折中考虑采用50MHz的鉴相频率。输出频率根据第二级锁相环的鉴相频率范围10~400MHz,此实例中选择为270MHz~300MHz的输出。

(2)滤波部分设计

这部分电路起着衔接两级锁相环路的作用,所以在处理第一级输出信号的过程中要着重考虑降低噪声、抑制谐波及控制功率等方面设计。

滤波电路,主要是将谐波和杂波就行抑制,降低信号的杂散。本实例根据目标设计采用5阶椭圆滤波器,在软件中的电路结构和仿真曲线如图3、4所示,由图3可以看到当270MHz信号经过此滤波器的时候,损耗较小且对高频杂波及谐波抑制较好,满足设计目标。

(3)第二级锁相环路设计

第二级锁相环路主要实现宽带调频的性能。第二级的锁相环芯片采用TI的低相位噪声锁相环芯片LMX2595。它具有小数分频的功能,在鉴相为300MHz时,可以实现最小0.1Hz的极小分辨率。它还具有优秀的低相位噪声性能,在闭环模式下鉴相200MHz、18GHz输出时相位噪声可达到-93dBc/Hz@1kHz、-98dBc/Hz@100kHz。第二级锁相环路的结构框图如图5所示。

由于第二级锁相环也为内置VCO的锁相环,不存在鉴相电压不能满足VCO电压控制范围的问题,所以可以使用无源的环路滤波,从而避免使用有缘滤波器给电路带来额外噪声的影响。

(4)杂散及相噪分析

在锁相环设计中,小数N分频PLL/VCO相比鉴相器参考频率虽然具有更为精细的频率步进,但它会产生称为整数边界杂散(IBS)的杂散输出。不同的鉴相频率、不同的N/M值设置以及电荷泵的电流大小都影响着最终输出信号的杂散水平。在设计中结合第二级锁相环的性能,通过ADIsimFrequencyPlanner计算出相应的参考输入频率,可有效降低输出频率的整数边界杂散以及其他类型杂散,使得锁相环输出实现低杂散的效果。此部分为双锁相环频率源的关键部分,根据不同的频率输出配置不同的参考输入,同时计算相应的锁相环中N(主锁相环即第二级锁相环的鉴相分频因数)和M(第一级锁相环的鉴相分频因数)的值,以及根据不同频率设置不同的电荷泵电流,来达到输出信号低杂散的目的。

图6为第二级锁相环整个VCO输出频段的最差整数边界杂散功率仿真结果;图7为噪声计算结果;图8为N值结果;图9为输出频率对应N/M及电荷泵电流计算结果。

通过仿真结果图6可知整个锁相环VCO的输出频段上,最差整数边界<-105dBc,以可满足绝大部分射频系统的杂散需求。

频率源的相位噪声指标主要受参考时钟和锁相环的影响,以下对两种因素分别进行分析:参考时钟:将参考时钟倍频到本振频率时相位噪声理论上恶化20lg(N),采用100MHz晶振的相位噪声-145dBc/Hz@1kHz,以输出最高本振(19GHz)进行最差情形的计算相位噪声可达到-99.4dBc/Hz@1kHz。

锁相环的相位噪声计算公式如下:

闪烁噪声:

PNflick=PLL_flicker_Norm+20log(Fvco/1GHz)-10log(offset/10kHz)

基底噪声:PNfloor=FloorFOM+20log(Fpd)-10log(Fvco/Fpd)

总噪声:PN=-10log{10(PNflick/10)+10(PNfloor/10)}

上面的3个公式中PLL_flicker_Norm数据手册中提供的值为-129dBc/Hz,Fvco是PLL的输出频率,Foffset是PLL相位噪声偏移量(比如计算1kHz处的相位噪声,则Foffset为103),FloorFOM数据手册中提供的值为-236dBc/Hz,Fpd是PLL的鉴相频率。

如直接使用参考信号100MHz作为第二级锁相环的参考时钟,取Fpd为鉴相频率,根据上述公式可以计算出19GHz输出时相位噪声为-92dBc/Hz@1kHz。

实际的锁相环输出相位噪声应取两种计算结果中最差的噪声-92dBc/Hz@1kHz,但以上的计算结果均为使用但锁相环的结果,采用双锁相环,由于第一级锁相环也存在闪烁噪声,所有最终输出信号的近端相位噪声要比但锁相环差,具体可恶化6dBc到8dBc。

第二级锁相环输出频带范围10MHz~19GHz,为一个宽频带、低相噪的锁相环,通过双锁相环的操作,牺牲少量的相位噪声,来将杂散有效的降低,从而得到满足指标需求的超宽带低相噪低杂散频率源。

本实例设计的超宽频低杂散频率源指标如下:

表1设计指标

本发明可产生超宽频带、低杂散、低相噪的频率信号,特别适用于雷达通信、无线通信、微波测试设备和频谱监测等系统。通常宽频带频率源往往杂散较多,采用该频率源后可大大改善杂散指标,提高系统的可靠性,有极好的经济效益和应用前景。

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明披露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求书的保护范围为准。

- 一种超宽频带低杂散双锁相环频率源

- 一种低杂散锁相环频率综合器电路