一种具有低近场辐射EMI噪声的功率模块

文献发布时间:2023-06-19 11:49:09

技术领域

本发明涉及一种功率模块,尤其涉及一种具有低近场辐射EMI噪声的功率模块。

背景技术

大功率、高频以及高速度开关是碳化硅器件的主流发展趋势,充分发挥碳化硅大功率器件高速开关和高频运行的性能优势正成为碳化硅器件扩大市占的核心优势。功率模块方案成为碳化硅器件的大功率化的必经之路,大功率意味着模块内部并联的芯片数量更多。如果这些并联芯片的栅-源极路径或者漏源极路径不合理,碳化硅功率模块在高速开关和高频运用将存在较严重的电磁干扰(electromagnetic interference,EMI)噪声问题。

在高功率密度集成系统中,高频运行的碳化硅功率模块除了存在较高的传导辐射EMI外,其近场辐射EMI引起的耦合失效问题也引起了大家的广泛关注。因此,降低模块近场辐射EMI噪声的结构设计成为消除高功率密度集成系统因近场耦合导致失效的关键。

功率模块内部各并联芯片栅-源极路径之间存在较大差异时功率模块的近场辐射EMI频谱中将出现更多数量的辐射尖峰,功率模块内部栅-源路径和漏-源路径设计不合理时,模块也会存在异常的近场辐射EMI噪声。

发明内容

为了解决上述现有技术的一个或多个技术问题,本发明提出了一种具有低近场辐射EMI噪声的功率模块及其栅-源极路径的结构设计。通过提高并联芯片栅-源极路径的对称性和均一性,以及优化模块内部DBC结构上层铜箔布局来实现降低功率模块近场辐射EMI噪声。

根据本发明一实施例提出了一种具有低近场辐射EMI噪声的功率模块,包括:热沉底板;第一焊料层,位于热沉底板上表面;DBC结构,位于所述第一焊料层上表面,其中的DBC结构包括下层铜箔、中间陶瓷层和上层铜箔;第二焊料层,位于DBC结构上层铜箔的上表面;功率芯片,位于第二焊料层上表面;以及半桥拓扑结构电路,位于DBC结构中间陶瓷层的上方,包括功率电极、功率芯片、栅极电组、金属引线、信号端子、铜桥、双绞线以及不同形状图案的上层铜箔,所述功率模块的栅-源极路径包括信号端子、金属引线、双绞线、栅极电阻、以及DBC结构上层铜箔中呈“L”形的栅极路径和源极路径,其中上桥栅-源极路径采用金属引线和DBC结构上层铜箔布线相结合的结构设计方案,下桥栅-源极路径采用双绞线和DBC结构上层铜箔布线相结合的结构设计方案。

根据本发明又一实施例提出了一种具有低近场辐射EMI噪声的功率模块,包括:热沉底板;第一焊料层,位于热沉底板上表面;DBC结构,位于所述第一焊料层上表面,其中的DBC结构包括下层铜箔、中间陶瓷层和上层铜箔;第二焊料层,位于DBC结构上层铜箔的上表面;功率芯片,位于第二焊料层上表面;以及半桥拓扑结构电路,位于DBC结构中间陶瓷层的上方,包括功率电极、功率芯片、栅极电阻、金属引线、信号端子、铜桥、双绞线以及不同形状图案的上层铜箔,所述功率模块的栅-源极路径包括信号端子、DBC结构上层铜箔中的栅极路径和源极路径、栅极电阻、双绞线、铜桥和金属引线,其中上桥栅-源极路径采用金属引线和DBC结构上层铜箔布线相结合的结构设计方案,由金属引线实现信号端子和上桥DBC结构上层铜箔中的栅极和源极路径的电气连接,上桥DBC结构上层铜箔中的栅极路径组合和源极路径组合均呈“匚”形且均以模块长轴中心线为对称轴;下桥栅-源极路径采用双绞线和DBC结构上层铜箔布线相结合的结构设计方案,由双绞线实现信号端子和DBC结构上层铜箔中的栅-源极路径的电气连接,下桥DBC结构上层铜箔中的栅极路径组合和源极路径组合也均呈“匚”形且以模块长轴中心线为对称轴;DBC结构上层铜箔中上桥栅极路径组合和下桥栅极路径组合对称分布于模块短轴中心线两侧,DBC结构上层铜箔中上桥源极路径组合和下桥源极路径组合对称分布于模块短轴中心线两侧,而且源极路径的“匚”形组合嵌套与栅极路径的“匚”形组合内部;以及单一桥臂对应的DBC结构上层铜箔图案设计,包括由布局功率芯片,布局栅极路径,布局源极路径以及布局其它结构的DBC结构上层铜箔所组合成的图案设计,其中布局其它结构的DBC结构上层铜箔包括漏-源极路径中的源极路径,漏-源极路径中的源极路径组合紧挨着栅-源极路径中的源极路径组合布局且彼此被分隔开,上桥漏-源极路径中两并联的源极路径为实现相互之间电气连接而引入铜桥的结构设计。

本发明提出的具有低近场辐射EMI噪声的功率模块内部栅源极路径结构设计方案中,针对并联芯片栅-源极路径提高其对称性和均一性的结构设计可降低碳化硅功率模块的近场辐射EMI噪声,所述功率模块可运用于高速开关和高频领域,在电动汽车、电力机车等对功率密度要求较高的应用场合具有显著的实用价值。

附图说明

图1为根据本发明一实施例的具有低近场辐射EMI噪声的功率模块的结构设计示意图1000;

图2为根据本发明一实施例所述的具有低近场辐射EMI噪声的功率模块的电路拓扑结构示意图2000;

图3为根据本发明一实施例所述的具有低近场辐射EMI噪声的功率模块侧视结构示意图3000;

图4为根据本发明一实施例所述的具有低近场辐射EMI噪声的功率模块测试结构示意图3000中的功率芯片布局区域的横截面结构放大示意图4000;

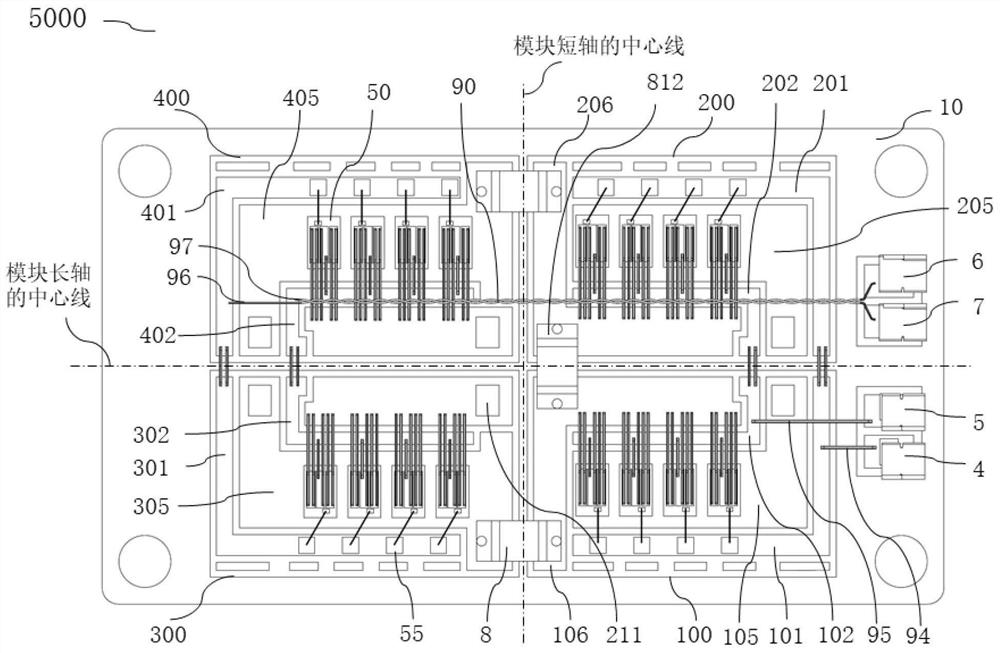

图5为根据本发明一实施例所述的具有低近场辐射EMI噪声的功率模块的栅-源极路径结构设计的平面布局示意图5000;

图6为根据本发明一实施例所述的具有低近场辐射EMI噪声的功率模块的DBC结构上层铜箔图案设计及其平面结构布局示意图6000。

具体实施方式

下面将结合附图详细描述本发明的具体实施例,应当注意,这里描述的实施例只用于举例说明,并不用于限制本发明。在以下描述中,为了便于对本发明的透彻理解,阐述了大量特定细节。然而,本领域普通技术人员可以理解,这些特定细节并非为实施本发明所必需。此外,在一些实施例中,为了避免混淆本发明,未对公知的电路、材料或方法做具体描述。

在整个说明书中,对“一个实施例”、“实施例”、“一个示例”或“示例”的提及意味着:结合该实施例或示例描述的特定特征、结构或特性被包含在本发明至少一个实施例中。因此,在整个说明书的各个地方出现的短语“在一个实施例中”、“在实施例中”、“一个示例”或“示例”不一定都指同一实施例或示例。此外,可以以任何适当的组合和/或子组合将特定的特征、结构或特性组合在一个或多个实施例或示例中。此外,本领域普通技术人员应当理解,在此提供的附图均是为了说明的目的,其中相同的附图标记指示相同的元件。这里使用的术语“和/或”包括一个或多个相关列出的项目的任何和所有组合。

本发明所述的功率模块所使用的功率芯片种类上包括但不限于碳化硅基(SiC)功率芯片,也包括硅基(Si)功率芯片、其他的宽禁带半导体基(wide band-gapsemiconductor)功率芯片,比如氮化镓基(GaN)功率芯片、金刚石基(Diamond)功率芯片等。

图1所示为本发明一实施例的具有低近场辐射EMI噪声的功率模块的结构设计示意图1000,所述功率模块包括“DC+”功率电极1、“DC-”功率电极2、“AC”功率电极3、上桥栅极信号端子4、上桥源极信号端子5、下桥栅极信号端子6、下桥源极信号端子7、上桥的DBC结构100和200、下桥的DBC结构300和400、连接上桥和下桥的铜桥8、金属引线9、热沉底板10、功率芯片50、栅极电阻55、上桥栅-源极路径中的栅极金属引线94、上桥栅-源极路径中的源极金属引线95、下桥栅-源极路径中的栅极金属引线96、下桥栅-源极路径中的双绞线90。此外,功率模块的结构还包括覆盖于如图1所述的功率芯片、DBC结构上层铜箔或者热层板上方的绝缘覆盖物和热固性塑料外壳等附属结构。

其中信号端子4、5、6和7并列的布局在功率模块的侧边且与模块短轴中心线平行,“DC+”功率电极1、“DC-”功率电极2、“AC”功率电极3并列地布局在模块长轴的中心线位置,模块实际制作中功率电极的顶端部分会被折弯90度,使其和模块底板平行。

图2所示为本发明一实施例所述的具有低近场辐射EMI噪声的功率模块的电路拓扑结构示意图2000,端口“DC+”和端口“DC-”分别用于连接直流母线的高电位和低电位,其中端口“DC+”对应于图1000中的“DC+”功率电极1,端口“DC-”对应于图100中的“DC-”功率电极2;而端口“AC”主要用于输出交流电流信号“AC”,对应于图1000中的“AC”功率电极3。虚线框结构50为功率芯片,并联数n代表功率芯片的并联数为n。半桥电路拓扑结构的上桥包括端口“DC+”、端口“AC”、两端口之间n个并联的功率芯片50及其相互之间的连接线。半桥电路拓扑结构的下桥包括端口“AC”、端口“DC-”、两端口之间n个并联的功率芯片50及其相互之间的连接线。

半桥拓扑电路中的上桥或者下桥也被称为半桥电路的桥臂,因此,半桥电路也被认为是包括两个桥臂,其中一个桥臂为上桥,另外一个桥臂为下桥。

图3所示为本发明一实施例所述的具有低近场辐射EMI噪声的功率模块的侧视结构示意图3000,其中包括“DC+”功率电极1、“DC-”功率电极2、“AC”功率电极3、连接上桥和下桥的铜桥8、连接上桥DBC结构100和200的铜桥812、金属引线9、热沉底板10、上桥栅-源极路径中的栅极金属引线94、上桥栅-源极路径中的源极金属引线95、下桥栅-源极路径中的双绞线90、下桥栅-源极路径中的栅极金属引线96、下桥栅-源极路径中的源极金属引线97、以及虚线圆圈4000所示的局部结构。

图4所示为图3000中虚线圆圈所示的功率芯片布局区域的的横截面结构放大示意图4000。该局部结构由下往上依次为热沉底板10、第一焊料层20、DBC下层铜箔层30、DBC中间陶瓷层31、DBC上层铜箔层32、第二焊料层40、功率芯片50和金属引线9。

图5所示为本发明一实施例所述的具有低近场辐射EMI噪声的功率模块的栅-源极路径结构设计的平面布局示意图5000,金属引线94实现栅极信号端子4和上桥DBC结构100上层铜箔中的栅极路径101的电气连接,金属引线95实现源极信号端子5和上桥DBC结构100上层铜箔中的源极路径102的电气连接;DBC结构200上层铜箔中的栅极路径和201和DBC结构100上层铜箔中的栅极路径和101通过金属引线实现电气连接、DBC结构200上层铜箔中的源极路径202和DBC结构100上层铜箔中的源极路径102通过金属引线实现电气连接;功率芯片50布局于DBC结构100上层铜箔区域105和DBC结构200上层铜箔区域205上,栅极电阻55布局于栅极路径101和201上,栅极电阻55和功率芯片50通过金属引线实现电气连接;铜桥812布局于DBC结构100的漏-源极路径中的源极路径106和DBC结构200的漏-源极路径中的源极路径206上。

双绞线90由下桥栅极金属引线96和下桥源极金属引线97组成,双绞线90的一端和栅极信号端子6和源极信号端子7连接,另外一端的栅极金属引线96和DBC结构400上层铜箔中的栅极路径401实现电气连接、而另外一端的源极金属引线97和DBC结构400上层铜箔中的源极路径402实现电气连接。

下桥DBC结构300上层铜箔中的栅极路径301和下桥DBC结构400上层铜箔中的栅极路径401通过金属引线实现电气连接、DBC结构300上层铜箔中的源极路径302和DBC结构400上层铜箔中的源极路径402通过金属引线实现电气连接、功率芯片50布局于DBC结构300上层铜箔区域305和DBC结构400上层铜箔区域405上,栅极电阻55布局于栅极路径301和401上,栅极电阻55和功率芯片50通过金属引线实现电气连接。

布局于上桥DBC结构100上层铜箔区域106和下桥DBC结构300中上层铜箔区域305上、以及布局于上桥DBC结构200上层铜箔区域206和下桥DBC结构400中上层铜箔区域405上的铜桥8实现功率模块上桥和下桥之间的电气连接。焊料211实现“DC-”功率电极2和DBC结构300和400上层铜箔区域的电气连接。

图6所示为本发明一实施例所述的具有低近场辐射EMI噪声的功率模块的DBC结构上层铜箔图案设计及其平面结构布局示意图6000。DBC结构上层铜箔中的栅极路径101、201、301和401、功率芯片布局区域105、205、305和405、源极路径102、202、302和402,以及布局铜桥8和812的漏-源极路径中的源极路径106和206的设计图案均为“L”形;布局“DC-”功率电极2的漏-源极路径中的源极路径306和406的设计图案均为“I”形且对称的分布于模块长轴中心线的两侧。信号端子4、5、6和7并列的布局于模块的一侧边,且平行于模块的短轴中心线。

本发明一实施例所述的功率模块,包括:热沉底板10,第一焊料层20位于热沉底板10的上表面;DBC结构100、200、300和400均位于第一焊料层20的上表面,其中DBC结构为覆铜陶瓷板(direct bond copper,DBC),其包括下层铜箔30、中间陶瓷层31和上层铜箔32;第二焊料层40位于DBC上层铜箔32的上表面;功率芯片50位于第二焊料层40的上表面;以及

半桥拓扑结构电路,位于DBC结构中间陶瓷层31的上方,包括:“DC+”功率电极1、“DC-”功率电极2、“AC”功率电极3、功率芯片50、栅极电组55、金属引线9、上桥的栅极金属引线94、上桥的源极金属引线95、下桥双绞线中的栅极金属引线96、下桥双绞线中的源极金属引线97、上桥的栅极信号端子4、上桥源极信号端子5、下桥栅极信号端子6、下桥的源极信号端子7、实现上桥和下桥连接的铜桥8、实现上桥DBC结构漏-源极路径中的源极路径相互之间电气连接的铜桥812、双绞线90、以及DBC结构中的不同形状图案的上层铜箔。

所述功率模块的栅-源极路径包括:信号端子4、5、6和7、金属引线9、双绞线90、栅极电阻55,以及DBC结构上层铜箔中呈“L”形的栅极路径和源极路径,其中上桥栅-源极路径采用金属引线94、95和DBC结构上层铜箔布线相结合的结构设计方案;下桥栅-源极路径采用双绞线90和DBC结构上层铜箔布线相结合的结构设计方案。

本发明一实施例所述的功率模块,其中上桥栅-源极路径的结构设计方案,包括:由金属引线94、95实现信号端子4、5和上桥DBC结构中的栅极路径和源极路径的电气连接;上桥DCB结构100中的栅极路径101和DBC结构200中的栅极路径102通过金属引线实现电气连接,两栅极路径101和201均呈“L”形且对称分布于功率模块的长轴中心线两侧,两栅极路径组合整体呈“匚”形且布局于上桥DBC结构边缘紧挨信号端子的模块外侧区域;同样的,上桥DCB结构100中的源极路径102和DBC结构200中的源极路径202也通过金属引线实现电气连接,两源极路径102和202均呈“L”形对称分布于功率模块的长轴中心线两侧,两源极路径组合整体呈“匚”形且紧挨模块中心布局;尺寸相对较小的源极路径的“匚”形组合嵌套于尺寸较大的栅极路径的“匚”形组合内部。

本发明一实施例所述的功率模块,其中下桥栅-源极路径的结构设计方案,包括:由双绞线90实现信号端子6、7和下桥DBC结构上层铜箔中的栅极路径和源极路径的电气连接,如图5所示双绞线90的一端中的栅极金属引线96和DBC结构400上层铜箔中的栅极路径401实现电气连接、源极金属引线97和DBC结构400上层铜箔中的源极路径402实现电气连接,而在双绞线的另外一端中的栅极金属引线96和下桥栅极信号端子6连接,而源极金属引线97和下桥源极信号端子7连接;下桥DBC结构300上层铜箔中的栅极路径301和DBC结构400上层铜箔中的栅极路径401通过金属引线实现电气连接,两栅极路径301和401均呈“L”形且对称分布于模块长轴中心线两侧,两栅极路径组合整体呈“匚”且布局于下桥DBC结构边缘的模块外侧区域;同样的,下桥DBC结构300上层铜箔中的源极路径302和DBC结构400上层铜箔中的源极路径402通过金属引线实现电气连接、两并联DBC结构中“L”形源极路径302和402对称分布于模块长轴中心线两侧,两源极路径组合整体呈“匚”形且紧挨模块中心布局;尺寸相对较小的源极路径的“匚”形组合嵌套于尺寸较大的栅极路径的“匚”形组合内部。

本发明一实施例的功率模块,其中上桥DBC结构上层铜箔中由栅极路径101和201组合成的呈“匚”形的栅极路径组合和下桥DBC结构上层铜箔中由栅极路径301和401组合成的呈“匚”形的栅极路径组合对称的分布于模块短轴中心线的两侧,上桥DBC结构上层铜箔中由源极路径102和202组合成的呈“匚”形的源极路径组合和下桥DBC结构上层铜箔中由栅极路径302和402组合成的呈“匚”形的源极路径组合也对称的分布于模块短轴中心线的两侧。

本发明一实施例所述的功率模块,其中单一桥臂对应的DBC结构上层铜箔图案设计,包括布局功率芯片,布局栅极路径,布局源极路径的上层铜箔设计,如图6所示的由上桥的DBC结构100和200的上层铜箔或者下桥的DBC结构300和400的上层铜箔组合成的图案设计,其中布局功率芯片的上层铜箔位于栅极路径和源极路径的中间,且将栅极路径和源极路径彼此分隔开,比如铜箔区域105将栅极路径101和源极路径102分隔开,铜箔区域205将栅极路径201和源极路径202分隔开,铜箔区域305将栅极路径301和源极路径302分隔开,铜箔区域405将栅极路径401和源极路径402分隔开。

本发明一实施例所述的的功率模块,还包括布局漏-源极路径中的源极路径的上层铜箔设计,比如漏-源极路径中的源极路径106、206、306和406的设计,其中上桥漏-源极路径中“L”形源极路径106和206的长边紧挨模块长轴中心线布局,上桥的两源极路径组合整体呈“T”形且以模块长轴中心线为对称轴并紧挨着模块短轴中心线布局;下桥漏-源极路径中“I”形源极路径306和406平行于模块长轴中心线,且紧挨着模块长轴中心线布局,下桥两源极路径组合整体呈“=”形且以模块长轴中心线为对称轴的同时也紧挨模块短轴中心线布局。

本发明一实施例所述的功率模块,其中单一桥臂的漏-源极路径中的源极路径组合紧挨着栅-源极路径中的源极路径组合布局且彼此被分隔开。如图6所示上桥漏-源极路径中的源极路径106和206的组合紧挨栅-源极路径中的源极路径102和202的组合布局且两组合被彼此分隔开,下桥漏-源极路径中的源极路径306和406的组合紧挨栅-源极路径中的源极路径302和402的组合布局且两组合被彼此分隔开。

本发明一实施例所述的功率模块,其中上桥漏-源极路径中两并联的源极路径为实现相互之间电气连接而引入铜桥的结构设计。如图5所示,为实现上桥漏-源极路径中两并联的源极路径106、206相互之间电气连接而在其上表面布局铜桥812。此外,铜桥812的布局特征是以模块长轴中心线为对称轴。

本发明一实施例所述的功率模块,其中上桥由信号端子到DBC结构100上层铜箔中的栅-源极路径的引线94、95和下桥由信号端子到DBC结构400上层铜箔中的栅-源极路径的双绞线90分别被布局在模块长轴中心线的两侧。

本发明所述的功率模块的栅-源极路径中还包括栅极电阻55的布局设计,栅极电阻55布局在栅极路径上,且每个栅极电阻55对应一个功率芯片50,栅极电阻55和功率芯片50之前通过金属引线时间电气连接。在同一个桥臂内,栅极电阻55的规格相同。

本发明一实施例中所述的栅极电阻是贴片电阻,栅极电阻均被布局在栅极路径上,如图5所示,栅极电阻的一端和栅极条使用类似锡焊的方式连接,而栅极电阻的另一端使用和芯片互连用的引线键合工艺实现连接。

本发明又一实施例提出了一种具有低近场辐射EMI噪声的功率模块,包括:热沉底板;第一焊料层,位于热沉底板上表面;DBC结构,位于所述第一焊料层上表面,其中的DBC结构包括下层铜箔、中间陶瓷层和上层铜箔;第二焊料层,位于DBC结构上层铜箔的上表面;功率芯片,位于第二焊料层上表面;以及

半桥拓扑结构电路,位于DBC结构中间陶瓷层的上方,包括功率电极、功率芯片、栅极电阻、金属引线、信号端子、铜桥、双绞线以及不同形状图案的上层铜箔,所述功率模块的栅-源极路径包括信号端子、DBC结构上层铜箔中的栅极路径和源极路径、栅极电阻、双绞线、铜桥和金属引线,其中

上桥栅-源极路径采用金属引线和DBC结构上层铜箔布线相结合的结构设计方案,由金属引线实现信号端子和上桥DBC结构上层铜箔中的栅极和源极路径的电气连接,上桥DBC结构上层铜箔中的栅极路径组合和源极路径组合均呈“匚”形且均以模块长轴中心线为对称轴;

下桥栅-源极路径采用双绞线和DBC结构上层铜箔布线相结合的结构设计方案,由双绞线实现信号端子和DBC结构上层铜箔中的栅-源极路径的电气连接,下桥DBC结构上层铜箔中的栅极路径组合和源极路径组合也均呈“匚”形且以模块长轴中心线为对称轴;

DBC结构上层铜箔中上桥栅极路径组合和下桥栅极路径组合对称分布于模块短轴中心线两侧,DBC结构上层铜箔中上桥源极路径组合和下桥源极路径组合对称分布于模块短轴中心线两侧,而且源极路径的“匚”形组合嵌套与栅极路径的“匚”形组合内部;以及

单一桥臂对应的DBC结构上层铜箔图案设计,包括由布局功率芯片,布局栅极路径,布局源极路径以及布局其它结构的DBC结构上层铜箔所组合成的图案设计,其中

布局其它结构的DBC结构上层铜箔包括漏-源极路径中的源极路径,漏-源极路径中的源极路径组合紧挨着栅-源极路径中的源极路径组合布局且彼此被分隔开,上桥漏-源极路径中两并联的源极路径为实现相互之间电气连接而引入铜桥的结构设计。

虽然已参照几个典型实施例描述了本发明,但应当理解,所用的术语是说明和示例性、而非限制性的术语。由于本发明能够以多种形式具体实施而不脱离发明的精神或实质,所以应当理解,上述实施例不限于任何前述的细节,而应在随附权利要求所限定的精神和范围内广泛地解释,因此落入权利要求或其等效范围内的全部变化和改型都应为随附权利要求所涵盖。

- 一种具有低近场辐射EMI噪声的功率模块

- 一种辐射EMI噪声超标分析方法