使用具有耦合到主动和被动服务器的逻辑单元的多个致动器驱动器的盘阵列

文献发布时间:2023-06-19 12:18:04

发明内容

本公开涉及利用具有耦合到主动和被动服务器的逻辑单元的多个致动器驱动器的盘阵列。在一个实施例中,阵列中的每一个盘驱动器包括外壳,该外壳封围电机和至少一个磁盘。外壳还封围第一致动器和第二致动器,该第一致动器和该第二致动器各自包括相应的第一头和第二头,该第一头和该第二头被配置为独立地从该至少一个磁盘读取和向该至少一个磁盘写入。该第一致动器映射到第一逻辑单元并且该第二致动器映射到第二逻辑单元。每一个盘驱动器的主机接口促进访问该第一逻辑单元和该第二逻辑单元。第一存储控制器作为第一主动服务器被附接到第一逻辑单元中的全部,并且作为第一被动服务器被附接到第二逻辑单元中的全部。该第二存储控制器与该第一存储控制器冗余地操作。该第二存储控制器作为第二主动服务器被附接到该第二逻辑单元中的全部,并且作为第二被动服务器被附接到该第一逻辑单元中的全部。

在另一个实施例中,阵列中的每一个盘驱动器包括N个逻辑单元,其中N>1。每一个盘驱动器的外壳封围电机、至少一个盘、以及N个致动器,每一个致动器与该N个逻辑单元中的相应的一个相关联并且被配置为独立地从该至少一个盘读取或向该至少一个盘写入。每一个盘驱动器的主机接口促进访问该N个逻辑单元。N个存储控制器各自作为主动服务器被附接到该每一个盘驱动器的该N个逻辑单元中相应的一个逻辑单元。该N个存储控制器中的每一个存储控制器作为被动服务器被附接到该每一个盘驱动器的该逻辑单元中的至少一个其他逻辑单元。根据以下详细讨论和附图,可以理解各个实施例的这些以及其他特征和方面。

附图说明

下文讨论参考以下附图,其中相同的附图标记可用于标识多个图中的相似/相同的部件。

图1是根据示例实施例的多致动器驱动器的图;

图2是根据示例实施例的盘阵列中驱动器池大小对重建时间的影响的图;

图3和图4是根据示例实施例的盘阵列的框图;

图5是根据示例实施例的示出了盘阵列中的重建操作的简化框图;

图6和图7示出了根据示例实施例的具有每驱动器N个逻辑单元和/或每阵列N个控制器的两个系统;以及

图8是根据示例实施例的方法的流程图。

具体实施方式

本公开大体涉及大规模数据存储系统。现代数据存储系统(例如,云存储)利用并行性和冗余来同时提高性能和可靠性。系统通常可以采用通常所说的RAID(独立磁盘冗余阵列),其中多个盘汇集在一起以形成逻辑卷。每一个盘保存数据的一部分(例如,分块(chunk)),并设置分块的子集来存储冗余数据(例如,奇偶校验)。存储控制器将这些分块组装到RAID条带(例如,具有六个数据分块和两个奇偶校验分块的RAID 6+2条带)中。添加奇偶校验数据允许在存储卷的条带的盘发生故障时重新创建数据。

在当前RAID系统中,将池的大小最大化是利用较大的池提高重建速度的一种方法。例如,在使用分簇(declustered)奇偶校验的系统中,分块的奇偶校验和数据分布在大量盘上,使得每一个盘都具有来自不同条带的奇偶校验和数据的组合。当驱动器发生故障时,可以通过一次性从大量驱动器读取数据来重建条带,从而缩短重建时间。

由于高可用性要求,盘阵列可以使用以主动-主动布置的两个控制器,其中每一个控制器主动管理存储阵列的一部分并且被动监测阵列的另一个部分。例如,一个控制器可以主动管理驱动器的第一半部分并且被动监测该驱动器的第二半部分。第二控制器主动管理该驱动器的该第二半部分并且被动监测该驱动器的该第一半部分。在该情况下,主动管理通常意味着控制器使用该控制器主动管理的驱动器为主机读取和写入请求提供服务。被动监测通常涉及监测驱动器的状态,但除非主动控制器发生故障,否则不执行从那些驱动器的任何读取或向那些驱动器的任何写入。

在该类型的高可用性布置中,每一个驱动器通常由仅一个控制器主动管理。因此,RAID系统中的最大池大小通常仅为包壳(或一组菊花链包壳)内可能的驱动器的一半。例如,具有用于106个驱动器和以主动-主动布置的两个存储控制器的空间的数据存储机架单元可以具有仅53个驱动器的最大池大小。这在一定程度上缩减重建时间(并相对应地提高了耐用性),但并不像具有更大的池所能缩减的那么多。例如,在图2中,图形示出了根据示例实施例的池大小可以如何影响重建时间。

在图2中,曲线示出了重建时间的估计,该估计是一组RAID 6条带的池大小的函数,每一个条带具有八个数据的分块和两个奇偶校验的条带。假设驱动器大小为14TB,用于读取和写入的重建吞吐量为50MB/s。对于53个驱动器的池,重建时间估计为28小时左右。利用106个驱动器,时间将缩短到16小时左右。

为了利用标准驱动器获得更大的池,将涉及对驱动器进行分区,并使两个控制器访问每一个驱动器上的一个分区。这将改善重建,但会损害性能,因为该两个控制器在尝试访问存储介质时将由于读取/写入头一次仅可以为一个请求提供服务而面临争用。但是,如果每一个驱动器可以同时为两个请求提供服务,则每一个存储控制器可以访问每一个驱动器的一部分,并且允许池将可用驱动器阵列(例如,上面示例中的具有106个驱动器的两个池)最大化,并且这样做不会损害性能。

在本文所描述的实施例中,具有多个控制器的存储阵列利用双致动器盘驱动器,该双致动器盘驱动器可以同时为来自多个存储阵列控制器的请求提供服务,该特征在本文中称为并行性。在图1中,图解图示了根据示例实施例的具有并行性特征的装置100(例如,数据存储驱动器)。装置100包括外壳101,该外壳101固持由主轴电机104驱动的至少一个磁盘102。滑动器106(也称为头、读取/写入头、读取头、写入头、记录头等)通过臂108被固持在盘102的第一表面102a上方。致动器114(例如,音圈电机或VCM)移动(例如,旋转)臂108,以将滑动器106放置在盘102上的不同轨道上方。滑动器包括读取换能器110和/或写入换能器112。读取换能器110响应于盘102上的变化的磁场而提供信号,并且耦合到控制器(未示出),在该控制器处单独的信号被独立地处理。写入换能器112接收来自控制器的信号,并将它们转换成改变盘102上的区域的磁取向的磁场。

装置100包括由第二臂118支撑的第二滑动器116。第二滑动器116被固持在盘102的第二表面102b上,并且致动器114使第二臂118移动到盘102上的不同轨道。臂118可以与臂108一起移动,或者臂108、臂118可以独立地移动(如致动器114上的虚线所指示的,该虚线指示具有两个VCM部分的分离式致动器)。在任一种配置中,臂108、臂118围绕同一轴旋转。滑动器116还包括读取和/或写入换能器120。换能器120能够与访问盘表面102a的读取/写入换能器110、112中的一个或这两个同时地从盘表面102b读取和/或向盘表面102b写入。

在另一个实施例中,装置100包括由第三臂128支撑的第三滑动器126。替代于或附加于第二滑动器116(及其相关联的致动硬件),可以包括第三滑动器126(及其相关联的致动硬件)。当第二致动器124使第三臂118移动到盘102上的不同轨道时,第三滑动器126被固持在盘102的第一表面102a上。臂128和致动器124独立于臂108和致动器114移动。滑动器126包括读取和/或写入换能器130。换能器130能够与第一滑动器106的换能器110、112同时地从同一盘表面102a读取和/或向同一盘表面102a写入。

在如图1中所示的示例中,可以使用多于一个的盘102,并且致动器114、124可以耦合到同时访问附加的盘表面中的一些或全部的附加的臂和头。在此上下文中,“访问(accessing)”通常是指电激活读取换能器或写入换能器,并将该换能器耦合到读取/写入通道以促进从盘读取和向盘写入。利用分离式致动器114的可独立移动的头通常可以同时访问不同的表面,例如,头106和头116同时访问不同的表面102a、102b。利用非同轴致动器114、124的可独立移动的头可以同时访问同一表面,例如,头106和头126两者可以同时访问表面102a。

如上所述,致动器114、124包括围绕各自的轴旋转臂108、臂118、臂128的VCM。VCM型致动器为磁头106、111、124提供粗略定位,例如用于长寻道。头106、头111、头124还可以由微致动器(未示出)精细定位,微致动器将头机械地耦合到臂108、臂118、臂128。这些微致动器可以独立于VCM 114、124并且彼此独立地移动,并且主要用于在轨道跟随期间保持头106、头116、头126在轨道上方的对准。

一个或多个系统控制器132耦合到相应的致动器114、124,并且控制致动器114、124的移动。系统控制器132可以包括芯片上系统,该芯片上系统执行诸如以下操作:伺服控制、对向盘102写入和从盘102读取的数据的编码和解码、对主机命令进行排队和格式化等。如果使用多于一个的系统控制器132,则多个控制器132可以具有并发地执行多个介质读取/写入操作的能力。例如,系统控制器132能够经由主机接口133向两个单独的存储阵列控制器(未示出)将装置100呈现作为两个单独的逻辑驱动单元,使得该装置可以在如本文所描述的高可用性存储阵列中使用。主机接口133可以使用现有数据存储协议(诸如SCSI、SATA、SAS、NVMe、以太网等)与存储控制器通信。

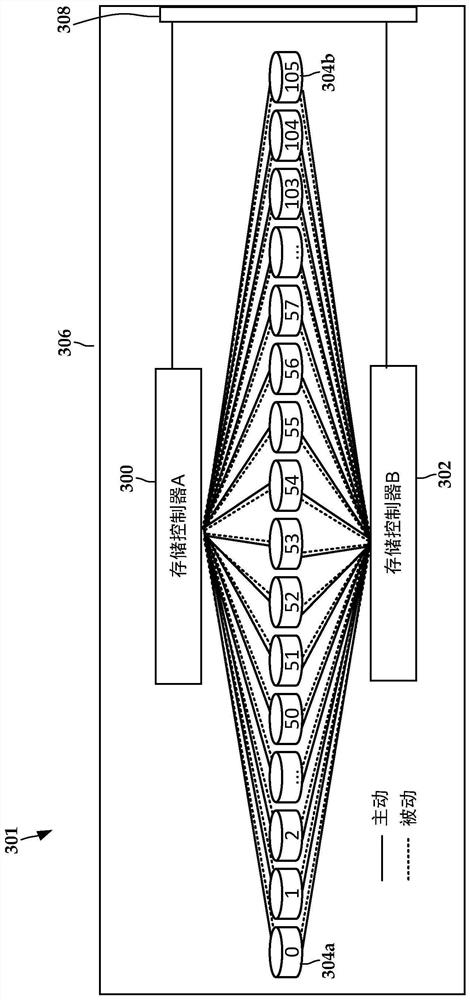

在图3中,框图示出了根据示例实施例的驱动器阵列系统301。第一存储控制器300和第二存储控制器302耦合到盘驱动器304的阵列。如相应的实线和虚线所指示的,控制器中的每一个以被动和主动模式耦合到驱动器中的一个驱动器。驱动器304中的每一个包括至少两个独立的致动器部分,并且其中的每一个致动器部分都由控制器300、302中的仅一个主动控制。驱动器阵列系统301可以包括包壳306(例如,机架安装包壳),该包壳306容纳驱动器304和控制器303、302。数据传输接口308(例如,以太网)可以用于促进数据中心的计算单元对阵列的访问。控制器到驱动器耦合的附加细节如图4所示。

在图4中,示出了驱动器304a和304b的内部细节。驱动器304a具有两个致动器部分304aa和304ab,它们分别被指示为被分配有驱动器304a内的上逻辑单元号码和下逻辑单元号码(LUN)。类似地,驱动器304b具有两个致动器部分304ba和304bb,它们分别被分配有上LUN和下LUN。请注意,这些驱动器中的致动器部分是围绕公共轴旋转的分离式致动器。这允许驱动器304a、304b的外壳保持现有的物理形状因子(例如,3.5英寸形状因子),尽管每一个致动器只能访问总表面积的一部分。请注意,指代驱动器LUN的术语“上”和“下”是任意应用的,并不旨在表示驱动器的任何特定取向或顺序、物理/逻辑地址的顺序等。此外,尽管存储控制器可以被描述为例如,耦合到多个盘驱动器的第一逻辑单元或第二逻辑单元,但这并不需要例如,第一逻辑单元都具有一些定义特性(诸如LUN标识符或逻辑地址范围)。术语“第一逻辑单元”和“第二逻辑单元”仅仅意味着每一个盘驱动器有两个单独的逻辑单元,该两个单独的逻辑单元以类似的方式与其他驱动器的其他逻辑单元分组。

当所示出的驱动器阵列发生故障时,第一存储控制器300将与服务器B重建故障驱动器的下LUN并行地重建故障驱动器的上LUN。在具有106个驱动器的经典分簇奇偶校验中,重建时间将预计为约16小时。然而,利用该建议的配置,重建时间将进一步减半,因为每一个服务器将与其他服务器并行重建其一半,因此预期的重建时间将减少到8小时。

在图5中,框图示出了根据示例性实施例的驱动阵列中重建的简化示例。第一控制器500和第二控制器501耦合到阵列503中的驱动器中的全部驱动器。驱动器全部被划分为第一逻辑单元504和第二逻辑单元505,每一个逻辑单元映射到驱动器内可独立操作的致动器。第一存储控制器500作为第一主动服务器被附接到第一逻辑单元504中的全部,并且作为第一被动服务器被附接到第二逻辑单元505中的全部。第二存储控制器501与第一存储控制器500冗余地操作,并且作为第二主动服务器被附接到第二逻辑单元505中的全部,并且作为第二被动服务器被附接到第一逻辑单元504中的全部。

在该示例中,第一逻辑单元504的第一条带包括分块1a-1d,并且第二逻辑单元505的第二条带包括分块2a-2d。这些分块1a-1d、2a-2d可以包括数据和奇偶校验的任何组合,并且在大多数布置中,条带将包括每条带多于四个分块。如阴影所指示的,驱动器506发生故障,这将触发重建操作,其中来自驱动器506的数据被复制到替换驱动器508上。

如箭头所指示的,第一存储控制器500可操作用于重建与故障驱动器506的第一逻辑单元504相关联的第一条带。与第一存储控制器500并行,第二存储控制器501可操作用于重建与故障驱动器506的第二逻辑单元505相关联的第二条带。对于第一条带,这涉及从分块1a-1c读取数据,并使用该数据在替换驱动器508上创建分块1d*,该分块1d*是故障驱动器506上的分块1d的重新创建。对于第二条带,这涉及从分块2b-2d读取数据,并使用该数据在替换驱动器508上创建分块2a*,该分块2a*是故障驱动器506上的分块1d的重新创建。这将对两个逻辑单元504、505的具有存储在故障驱动器506上的任何分块的任何条带重复。注意,如果驱动器的仅一个逻辑单元发生故障(例如,致动器中的一个上的头发生故障),则仅有与该逻辑单元相关联的主动存储控制器500、501需要执行重建,并且其他存储控制器可以正常操作,同时以被动模式跟踪重建。

虽然上述示例示出了具有每驱动器两个逻辑单元和每阵列两个控制器的系统,但是这可以扩展到每驱动器N个逻辑单元和/或每阵列N个控制器(其中N>2)。在图1中所示出和所描述的实施例中,驱动器可以具有被分离到围绕同一轴旋转的三个或更多个部分中的致动器。或者,驱动器可以具有围绕不同的轴旋转的两个分离式致动器。这可以提供多达N路控制器的冗余。在图6和图7中示出了根据示例实施例的具有N=4的两个系统。本领域技术人员将能够将图6和图7中所示出的概念扩展到N的其他值,例如N=3、N=5等。

在图6中,四个存储控制器600-603耦合到驱动器阵列,示出了该驱动器阵列中的两个驱动器604、605。每一个驱动器604、605被划分为4个逻辑单元,例如,对于驱动器604为LUN0a-LUN0d。存储控制器600主动耦合到全部LUNna,并且被动耦合到全部LUNnb、LUNnc和LUNnd(其中n={0,1,…N})。其他存储控制器601-603类似地主动耦合到LUN的专用组,并且被动耦合到不在该专用组中的全部LUN。因此,在该配置中,每一个盘上的每一个LUN都具有一个控制该LUN的主动服务器和三(N-1)个监测该LUN的被动服务器。这将提供更高级别的可用性。

注意,如果一个控制器发生故障,则其他控制器中的一个可以接管由该故障控制器先前管理的LUN中的全部。在替代情况下,剩余的控制器可以将由故障控制器先前管理的LUN划分为多个部分(例如,均匀部分或不均匀部分),N-1个控制器中的每一个控制器作为主动服务器接管LUN的相应部分。这可以将对N-1个剩余的控制器中的全部的性能影响最小化。故障控制器的LUN到剩余的控制器的分配可以基于一些预先布置的划分或者可以动态地(例如,基于当前工作负载)或随机地分配。

在图7中,四个存储控制器700-703耦合到驱动器阵列,示出了该驱动器阵列中的两个驱动器704、705。每一个驱动器704、705被划分为4个逻辑单元,例如,对于驱动器704为LUN0a-LUN0d。存储控制器700主动耦合到全部LUNna并且被动耦合到全部LUNnb(其中n={0,1,…N})。存储控制器701主动耦合到全部LUNnb并且被动耦合到全部LUNna。类似布置也可以见控制器702和703。因此,在该配置中,每一个盘上的每一个LUN都具有一个控制该LUN的主动服务器和一个监测该LUN的被动服务器。这为每个LUN提供了与前述示例(其中N=2)相同的冗余量,但是如果一个控制器发生故障,则影响较小。例如,如果控制器700发生故障,那么控制器701将由于故障而经历工作负载的增加,但是控制器702和703不会。在图6和图7的任一个配置中,故障驱动器的重建时间可以高达图3中的布置的重建时间的一半,因为四个控制器可以在每一个盘上的四个不同的独立逻辑单元上并行操作。

注意,图7中所示的配置可以顺应于控制器700-703和盘阵列之间的其他连接。在图示的示例中,存储控制器700在全部盘上充当存储控制器701的备份,并且反之亦然。在一些布置中,可以针对不同的驱动器改变主动-被动连接。例如,考虑阵列具有驱动器1(未示出),其中控制器700主动连接到LUN1a并且存储控制器702被动耦合到LUN1a。这与驱动器0704的耦合布置不同,其中存储控制器701被动耦合到LUN0a。对于驱动器1,存储控制器701可以被动耦合到另一个LUN,例如,LUN1d。这些被动耦合可以是随机的或者遵循一些重复的顺序。

在图8中,流程图示出了根据示例实施例的方法。该方法涉及在800将第一存储控制器作为第一主动服务器耦合到盘驱动器的阵列的第一逻辑单元,并作为第一被动服务器耦合到盘驱动器的阵列的全部第二逻辑单元。阵列的每一个盘驱动器包括包壳以及第一致动器和第二致动器,该包壳容纳驱动至少一个盘的电机,该第一致动器和第二致动器各自具有被配置为独立地从该至少一个盘读取和向该至少一个盘写入的第一头和第二头。第一致动器映射到第一逻辑单元中的一个,并且第二致动器映射到第二逻辑单元中的一个。第二存储控制器在801作为第二主动服务器耦合到第二逻辑单元,并作为第二被动服务器耦合到第一逻辑单元中的全部。

决策框802和803表示在盘阵列的使用寿命中可能发生的事件。在框802处,检测到故障控制器(例如,第二控制器),在该情况下,在804工作控制器(例如,第一控制器)作为主动服务器被附接到由故障控制器(例如,第二控制器)先前管理的条带中的全部。在框803处,检测到故障驱动器,在该情况下,在805经由第一存储控制器和第二存储控制器发生第一条带和第二条带的并行重建。第一条带和第二条带与故障驱动器的相应的第一逻辑单元和第二逻辑单元相关联。

可以使用相互作用以提供特定结果的电路系统、固件和/或软件模块来实现上文所描述的各种实施例。本领域的技术人员可容易地使用本领域公知的知识在模块化的层级或作为整体来实现此类所描述的功能。例如,本文中图示的流程图和控制图可以用于创建计算机可读指令/代码以供处理器执行。此类指令可以被存储在非瞬态计算机可读介质上,并且被传输到处理器以供执行,如本领域中已知的那样。上文所示出的结构和过程仅为可以用于提供上文所描述的功能的实施例的代表性示例。

除非另有说明,否则在说明书和权利要求中使用的表示特征大小、数量和物理特性的所有数字应当理解为在所有情况下均由术语“约”修饰。因此,除非相反地指明,否则在前述说明书和所附权利要求中阐述的数值参数是近似值,这些近似值可以根据利用本文所公开的教导的本领域技术人员所寻求的期望性质而变化。通过端点对数值范围的使用包括该范围内的所有数值(例如,从1到5包括1、1.5、2、2.75、3、3.80、4和5)以及该范围内的任何范围。

示例实施例的前述描述已经被呈现用于说明和描述的目的。其不旨在是详尽的或将实施例限制于所公开的精确形式。根据上述教导,许多修改和变化是可能的。所公开的实施例的任何或全部特征可以单独或以任何组合应用,并且不旨在限制,而仅是说明性的。本发明的范围不旨在受限于本具体实施方式,而是由所附权利要求书来确定。

进一步的示例

示例1.一种系统,包括:

盘驱动器的阵列,每一个盘驱动器包括:

外壳,所述外壳封围电机、至少一个磁盘、以及第一致动器和第二致动器,所述第一致动器和所述第二致动器中的每一个各自包括相应的第一头和第二头,所述第一头和所述第二头被配置为独立地从所述至少一个磁盘读取和向所述至少一个磁盘写入,所述第一致动器映射到第一逻辑单元并且所述第二致动器映射到第二逻辑单元;以及

主机接口,所述主机接口促进访问所述第一逻辑单元和所述第二逻辑单元;

第一存储控制器,所述第一存储控制器作为第一主动服务器被附接到所述第一逻辑单元中的全部,并且作为第一被动服务器被附接到所述第二逻辑单元中的全部;以及

第二存储控制器,所述第二存储控制器与所述第一存储控制器冗余地操作,所述第二存储控制器作为第二主动服务器被附接到所述第二逻辑单元中的全部,并且作为第二被动服务器被附接到所述第一逻辑单元中的全部。

示例2.如示例1所述的系统,其特征在于,所述盘驱动器中的每一个包括第一独立操作控制器和第二独立操作控制器,所述第一独立操作控制器和所述第二独立操作控制器耦合到相应的所述第一致动器和所述第二致动器,并且为相应的所述第一逻辑单元和所述第二逻辑单元的请求提供服务。

示例3.如示例1所述的系统,其特征在于,所述第一致动器和所述第二致动器是围绕同一轴旋转的分离式致动器。

示例4.如示例1所述的系统,其特征在于,数据以具有分簇奇偶校验的RAID条带形式存储在所述盘驱动器的所述阵列上。

示例5.如示例1所述的系统,其特征在于,在所述阵列中检测到故障驱动器时,所述第一存储控制器重建与所述故障驱动器的所述第一逻辑单元相关联的第一条带,并且与所述第一存储控制器重建并行地,所述第二存储控制器重建与所述故障驱动器的所述第二逻辑单元相关联的第二条带。

示例6.如示例1所述的系统,其特征在于,在检测到所述第二存储控制器的故障时,所述第一存储控制器作为所述第二主动服务器被附接到所述第二逻辑单元。

示例7.一种方法,包括:

将第一存储控制器作为第一主动服务器耦合到盘驱动器的阵列的第一逻辑单元,并作为第一被动服务器耦合到所述盘驱动器的所述阵列的第二逻辑单元,其中所述阵列的所述每一个盘驱动器包括外壳,所述外壳封围电机、至少一个磁盘、以及第一致动器和第二致动器,所述第一致动器和所述第二致动器中的每一个各自包括相应的第一头和第二头,所述第一头和所述第二头被配置为独立地从所述至少一个磁盘读取和向所述至少一个磁盘写入,所述第一致动器映射到第一逻辑单元中的一个并且所述第二致动器映射到所述第二逻辑单元中的一个;以及

将第二存储控制器作为第二主动服务器耦合到所述第二逻辑单元,并且作为第二被动服务器耦合到所述第一逻辑单元。

示例8.如示例7所述的方法,其特征在于,所述盘驱动器中的每一个包括第一独立操作系统控制器和第二独立操作系统控制器,所述第一独立操作系统控制器和所述第二独立操作系统控制器耦合到相应的所述第一致动器和所述第二致动器,并且为相应的所述第一逻辑单元和所述第二逻辑单元的请求提供服务。

示例9.如示例7所述的方法,其特征在于,所述第一致动器和所述第二致动器是围绕同一轴旋转的分离式致动器。

示例10.如示例7所述的方法,其特征在于,数据以具有分簇奇偶校验的RAID条带形式存储在所述盘驱动器的所述阵列上。

示例11.如示例7所述的方法,进一步包括:

检测所述阵列中的故障驱动器,并响应于此:

经由所述第一存储控制器重建与所述故障驱动器的所述第一逻辑单元相关联的第一条带;以及

与所述第一存储控制器重建所述第一条带并行地,经由所述第二存储控制器重建与所述故障驱动器的所述第二逻辑单元相关联的第二条带。

示例12.如示例7所述的方法,进一步包括检测所述第二存储控制器的故障,并响应于此,将所述第一存储控制器作为所述第二主动服务器附接到所述第二逻辑单元。

示例13.一种系统,包括:

盘驱动器的阵列,每一个盘驱动器包括:

N个逻辑单元,其中N>1;

外壳,所述外壳封围电机、至少一个盘;以及

N个致动器,每一个致动器与所述N个逻辑单元中的相应的一个相关联并且被配置为独立地从所述至少一个盘读取或向所述至少一个盘写入;以及

主机接口,所述主机接口促进访问所述N个逻辑单元;以及

N个存储控制器,每一个存储控制器作为主动服务器被附接到所述每一个盘驱动器的所述N个逻辑单元中相应的一个逻辑单元,所述N个存储控制器中的每一个存储控制器作为被动服务器被附接到所述每一个盘驱动器的所述逻辑单元中的至少一个其他逻辑单元。

示例14.如示例14所述的系统,其特征在于,N>2,并且其中所述N个存储控制器中的每一个存储控制器作为被动服务器被附接到每一个驱动器的N-1个其他逻辑单元。

示例15.如示例14所述的系统,其特征在于,N>2,并且其中所述N个存储控制器中的每一个存储控制器作为被动服务器被附接到每一个驱动器的一个其他逻辑单元。

示例16.如示例14所述的系统,其特征在于,数据以具有分簇奇偶校验的RAID条带形式存储在所述盘驱动器的所述阵列上。

示例17.如示例14所述的系统,其特征在于,在检测到所述阵列中的故障驱动器时,所述N个存储控制器并行地重建与所述故障驱动器的所述N个逻辑单元相关联的N个条带。

示例18.如示例14所述的系统,其特征在于,在检测到所述N个存储控制器中的一个发生故障时,所述N个存储控制器中的一个其他存储控制器接管故障控制器的主动连接。

示例19.如示例14所述的系统,其特征在于,N>2,并且其中在检测到所述N个存储控制器中的一个发生故障时,所述其他N-1个存储控制器各自接管故障存储控制器的主动连接的相应的部分。

示例20.如示例14所述的系统,其特征在于,N>2,并且其中在检测到所述N个存储控制器中的一个发生故障时,所述N个存储控制器中的一个其他存储控制器接管所述故障存储控制器的主动连接。

- 使用具有耦合到主动和被动服务器的逻辑单元的多个致动器驱动器的盘阵列

- 利用多个阵列的集成的被动和主动地震勘测