接收器电路、存储器装置以及使用其的操作方法

文献发布时间:2023-06-19 19:16:40

技术领域

本公开涉及一种存储器装置的接收器电路,且更具体地说,涉及能够降低功率消耗且扩大参考电压的操作范围的接收器电路、存储器装置以及使用其的操作方法。

背景技术

存储器广泛地用于在多种电子装置中存储数据,所述电子装置包含移动装置、计算机、自动驾驶车辆、电器等。存储器包含用于在存储器与其它电路之间接收和传输信号的输入/输出(input/output;IO)电路。IO电路可包含根据参考电压操作的至少一个接收器。

由于不同电子装置中的接收器是在不同参考电压范围中操作,因此会期望接收器能够操作在较宽参考电压范围中。此外,由于最近对低功率电子装置的需求增长,因此会期望接收器具有低功率消耗量。

发明内容

本公开介绍一种能够扩大参考电压的操作范围且降低功率消耗的接收器电路、存储器装置以及其操作方法。

在一些实施例中,接收器电路包含一对前级放大器电路和后级放大器电路。一对前级放大器电路配置成接收输入信号和参考电压信号,且根据输入信号与参考电压信号之间的差值输出第一前级放大信号和第二前级放大信号。一对前级放大器电路包含第一前级放大器电路和第二前级放大器电路,其中第一前级放大器电路包含一对第一n型晶体管,且一对第一n型晶体管的栅极端子分别接收输入信号和参考电压信号。第二前级放大器电路包含一对第一p型晶体管,其中一对第一p型晶体管的栅极端子分别接收输入信号和参考电压信号。后级放大器电路配置成从一对前级放大器电路接收第一前级放大信号和第二前级放大信号,且根据第一前级放大信号和第二前级放大信号输出后放大信号。

在一些实施例中,存储器装置包含具有多个存储器单元的存储器核心电路和接收器电路。接收器电路包含一对前级放大器电路和后级放大器电路。一对前级放大器电路配置成接收输入信号和参考电压信号,且根据输入信号与参考电压信号之间的差值输出第一前级放大信号和第二前级放大信号。一对前级放大器电路包含第一前级放大器电路和第二前级放大器电路,其中第一前级放大器电路包含一对第一n型晶体管,且一对第一n型晶体管的栅极端子分别接收输入信号和参考电压信号。第二前级放大器电路包含一对第一p型晶体管,其中一对第一p型晶体管的栅极端子分别接收输入信号和参考电压信号。后级放大器电路配置成从一对前级放大器电路接收第一前级放大信号和第二前级放大信号,且根据第一前级放大信号和第二前级放大信号输出后放大信号。

在一些实施例中,操作方法包含以下步骤:由一对前级放大器电路接收输入信号和参考电压信号;根据输入信号与参考电压信号之间的差值,由一对前级放大器电路输出第一前级放大信号和第二前级放大信号;由后级放大器电路从一对前级放大器电路接收第一前级放大信号和第二前级放大信号;以及根据第一前级放大信号和第二前级放大信号,由后级放大器电路输出后放大信号。一对前级放大器电路包含第一前级放大器电路和第二前级放大器电路。第一前级放大器电路包含一对第一n型晶体管,其中一对第一n型晶体管的栅极端子分别接收输入信号和参考电压信号。第二前级放大器电路包含一对第一p型晶体管,其中一对第一p型晶体管的栅极端子分别接收输入信号和参考电压信号。

根据本公开的实施例,包含用于接收输入信号的一对p型晶体管的第一前级放大器电路可称为p型放大器电路;且包含用于接收输入信号的n型晶体管的第二前级放大器电路可称为n型放大器电路。由于p型放大器电路在较低参考电压范围(也称为第一参考电压范围)下有效地操作,且n型放大器电路在较高参考电压范围(也称为第一参考电压范围)下有效地操作,因此本公开中的接收器电路可在较宽参考电压范围(即,较高范围和较低范围两者)下有效地操作。此外,由于在接收器电路的操作期间接收器电路可禁能前级放大器电路中的一个,因此降低了接收器电路的功率消耗。

附图说明

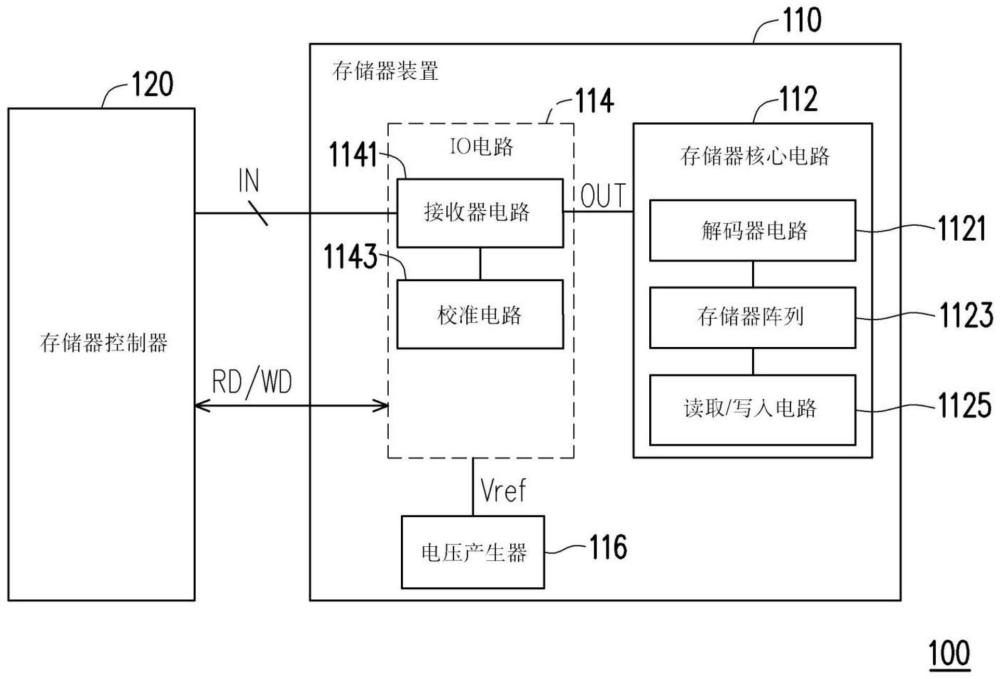

图1是示出根据一些实施例的存储器系统的示意图;

图2是示出根据一些实施例的接收器电路的示意图;

图3示出根据一些实施例的图2中的接收器电路的具体结构;

图4是示出根据一些实施例的接收器电路的操作方法的流程图。

附图标号说明

100:存储器系统;

101、102:前级放大器电路;

103:后级放大器电路;

110:存储器装置;

112:存储器核心电路;

114:输入/输出电路;

116:电压产生器;

120:存储器控制器;

401、402、403、404:框;

1011、1011_1、1011_2、1021、1021_1、1021_2:前级放大信号;

1121:解码器电路;

1123:存储器阵列;

1125:读取/写入电路;

1141:接收器电路;

1143:校准电路;

EN1、EN2:启用信号;

GND:电源电压/接地电压;

IN:输入信号;

N11、N12、N21、N22、N31、N32:n型晶体管;

ND11、ND12、ND21、ND22:连接节点;

OUT:输出信号;

P11、P12、P21、P22、P31、P32:p型晶体管;

RD:读取数据;

T1、T2:启用开关;

VDD:电源电压;

Vref:参考电压信号;

WD:写入数据。

具体实施方式

现在将详细参考本发明的目前优选实施例,其示例在附图中示出。在可能的情况下,在附图和描述中使用相同附图标号来指代相同或类似部件。

图1示出根据一些实施例的包含存储器装置110和存储器控制器120的存储器系统100的示意图。存储器装置110可包含存储器核心电路112和输入/输出(IO)电路114。存储器核心电路112配置成存储数据且进行例如读取操作、编程操作、擦除操作的存储器操作。IO电路114配置成在存储器装置110与存储器控制器120之间接收和传输信号。在实施例中,存储器装置110是动态随机存取存储器(dynamic random-access memory;DRAM),但本公开不限于此。任何其它类型的存储器装置110属于本公开的范围内。

在实施例中,存储器核心电路112包含解码器电路1121、存储器阵列1123以及读取/写入电路1125。存储器阵列1123包含用于存储数据的多个存储器单元(未示出),其中存储器单元中的每一个与存储器地址相关联。解码器电路1121耦合到存储器阵列和IO电路114,配置成对从IO电路114接收的地址信号进行解码以选择用于存储器操作的至少一个存储器单元。读取/写入电路1125耦合到存储器阵列1123和IO电路114,且配置成对存储器阵列1123的存储器单元进行存储器操作。在实例中,读取/写入电路1125可对来自存储器阵列1123的选定存储器单元的读取数据RD进行读取操作数据,且将读取数据RD输出到存储器控制器120。在另一实例中,读取/写入电路1125可对存储器阵列1123中的选定存储器单元的写入数据WD进行编程操作。写入数据WD可通过IO电路114从存储器控制器120获得。

在实施例中,IO电路114包含接收输入信号IN和参考电压信号Vref的接收器电路1141。接收器电路1141配置成放大参考电压信号Vref与输入信号IN之间的差值以产生输出信号OUT。可将输出信号OUT供应到存储器核心电路112以用于解码和进行存储器操作。在实施例中,接收器电路1141是只接收一个输入信号(即,输入信号IN)的单端接收器电路,且根据参考信号Vref操作以输出输出信号OUT。举例来说,接收器电路1141是接收地址/命令(address/command;C/A信号)的命令和地址接收器电路,且配置成放大参考电压信号Vref与C/A信号之间的差值以产生输出信号OUT。C/A信号可包含地址信号和命令信号中的至少一个,其中地址信号定义用于操作的选定存储器单元的存储器地址,且命令信号定义对选定存储器单元进行的操作。

在一些实施例中,IO电路114进一步包含校准电路1143,所述校准电路1143耦合到接收器电路1141且配置成在接收器电路1141的校准模式期间校准参考电压信号Vref。在校准模式期间,参考电压信号Vref的电平以递增方式或以递减方式变化,且分析接收器电路1141的输出信号OUT以判定允许接收器电路1141正确操作的参考电压信号Vref的可操作电压范围。在实例中,将测试模式(未示出)和参考电压信号Vref中的每一电平输入到接收器电路1141,且分析接收器电路1141的输出信号OUT以判断接收器电路1141是否在参考电压信号Vref中的每一电平处正确接收测试模式。通过这种方式,可在接收器电路1141的校准模式下判定参考电压信号Vref的可操作电压范围。

在实施例中,接收器电路1141的校准模式可由激活信号(未示出)触发。在实例中,每当接收器电路1141通电时,触发接收器电路1141的校准模式以校准参考电压信号Vref。应了解,本公开不限于触发接收器电路1141的校准模式的条件。此外,校准电路1143的位置在本公开中不受限制。举例来说,校准电路1143可位于接收器电路1141的内部。接收器电路1141可包含设计成在存储器装置110与存储器控制器120之间接收或传输信号的电路(未示出)。

在进行接收器电路1141的校准模式之后,判定参考电压信号Vref的可操作电压范围。在实施例中,参考电压信号Vref的固定电平(即,固定参考电压信号)选自参考电压信号Vref的可操作电压范围,使得在接收器电路1141的操作模式中使用固定参考电压信号。在实施例中,固定参考电压信号是参考电压信号Vref的可操作电压范围中的中间电压,但本公开不限于为操作模式选择固定参考电压的任何特定方式。

在实施例中,参考电压Vref和固定参考电压信号Vref的可操作电压范围中的至少一个存储在包含在存储器装置110中的寄存器或非易失性存储器中。固定参考电压信号Vref可存储在存储器核心电路112的存储器单元中或存储器装置110的任何其它寄存器、存储器中。在接收器电路1141的操作模式期间使用固定参考电压信号Vref。

在一些实施例中,存储器装置110进一步包含电压产生器116,其配置成产生用于存储器装置110的操作的电压。电压产生器116可产生参考电压信号Vref,且向IO电路114中的接收器电路1141提供所产生参考电压信号Vref。在一些实施例中,电压产生器116在接收器电路1141的校准模式下产生具有变化电平的参考电压信号Vref。参考电压信号Vref的电平可以递增方式或以递减方式变化。在操作模式下,电压产生器116配置成产生固定参考电压信号Vref且将其供应到接收器电路1141。

图2示出根据一些实施例的包含一对前级放大器电路101和前级放大器电路102以及后级放大器电路103的接收器电路1141的示意图。前级放大器电路101接收输入信号IN和参考电压信号Vref,且基于输入信号IN与参考电压信号Vref之间的差值输出前级放大信号1011。类似地,前级放大器电路102接收输入信号IN和参考电压信号Vref,且基于输入信号IN与参考电压信号Vref之间的差值输出前级放大信号1021。在实施例中,前级放大器电路101和前级放大器电路102是不同类型的差分放大器。在实例中,前级放大器电路101是p型差分放大器,且前级放大器电路102是n型差分放大器。前级放大器电路101和前级放大器电路102配置成放大输入信号IN与参考电压信号Vref之间的差值以分别产生前级放大信号1011和前级放大信号1021。

后级放大器电路103耦合到前级放大器电路101和前级放大器电路102以从前级放大器电路101和前级放大器电路102接收前级放大信号1011和前级放大信号1021。后级放大器电路103配置成基于前级放大信号1011和前级放大信号1021产生输出信号OUT(也称为后放大信号)。可将输出信号OUT进一步供应到存储器核心电路112以用于进一步处理。

图3示出根据一些实施例的包含前级放大器电路101和前级放大器电路102以及后级放大器电路103的接收器电路1141的具体结构。前级放大器电路101包含一对p型晶体管P11和p型晶体管P12,其中p型晶体管P11和p型晶体管P12的源极端子耦合到接收电源电压VDD的参考节点,且p型晶体管P11和p型晶体管P12的栅极端子耦合到p型晶体管P11和p型晶体管P12的漏极端子。换句话说,将p型晶体管P11和p型晶体管P12设计成前级放大器电路101中的二极管。前级放大器电路101进一步包含一对n型晶体管N11和n型晶体管N12,其中n型晶体管N11和n型晶体管N12的漏极端子通过连接节点ND11和连接节点ND12耦合到p型晶体管P11和p型晶体管P12的漏极端子。n型晶体管N11和n型晶体管N12的栅极端子分别接收输入信号IN和参考电压信号Vref。

前级放大器电路101通过n型晶体管N11和n型晶体管N12的栅极端子接收输入信号IN和参考电压信号Vref。前级放大器电路101配置成放大输入信号IN与参考电压信号Vref之间的差值以分别通过连接节点ND11和连接节点ND12产生前级放大信号1011_1和前级放大信号1011_2。前级放大信号1011_1和前级放大信号1011_2可被视为前级放大器电路101的差分输出信号。前级放大器电路101通过连接节点ND11和连接节点ND12向后级放大器电路103输出前级放大信号1011_1和前级放大信号1011_2。

前级放大器电路102可包含一对n型晶体管N21和n型晶体管N22,其中n型晶体管N21和n型晶体管N22的源极端子耦合到接收电源电压GND的参考节点,且n型晶体管N21和n型晶体管N22的栅极端子分别耦合到n型晶体管N21和n型晶体管N22的漏极端子。换句话说,将n型晶体管N21和n型晶体管N22设计成前级放大器电路102中的二极管。前级放大器电路102进一步包含一对p型晶体管P21和p型晶体管P22,其中p型晶体管P21和p型晶体管P22的漏极端子通过连接节点ND21和连接节点ND22耦合到n型晶体管N21和n型晶体管N22的漏极端子。p型晶体管P21和p型晶体管P22的栅极端子分别接收输入信号IN和参考电压信号Vref。

前级放大器电路102通过p型晶体管P21和p型晶体管P22的栅极端子接收输入信号IN和参考电压信号Vref。前级放大器电路102配置成放大输入信号IN与参考电压信号Vref之间的差值以分别通过连接节点ND21和连接节点ND22产生前级放大信号1021_1和前级放大信号1021_2。前级放大信号1021_1和前级放大信号1021_2可被视为前级放大器电路102的差分输出信号。前级放大器电路102通过连接节点ND21和连接节点ND22向后级放大器电路103输出前级放大信号1021_1和前级放大信号1021_2。

在以上实施例中,包含用于接收输入信号IN和参考电压信号Vref的一对n型晶体管N11和n型晶体管N12的前级放大器电路101可称为n型放大器电路;且包含用于接收输入信号IN和参考电压信号Vref的一对p型晶体管P21和p型晶体管P22的前级放大器电路102可称为p型放大器电路。当参考电压信号Vref处于第一参考电压范围(即,较高电压范围或高电压范围)中时,n型放大器电路很好地操作,而p型放大器电路可能失去增益。相反地,当参考电压信号Vref处于第二参考电压范围(即,较低电压范围)中时,p型放大器电路很好地操作,而n型放大器电路可能失去增益。在本公开的实施例中,接收器电路1141包含n型放大器电路(即,前级放大器电路101)和p型放大器电路(即,前级放大器电路102)两者,接收器电路1141在较高参考电压信号Vref电压范围和较低参考电压信号Vref范围下都可很好地操作。换句话说,接收器电路1141可在较宽参考电压信号Vref范围中很好地操作而不失去接收器电路1141的增益性能。

在一些实施例中,前级放大器电路101和前级放大器电路102进一步包含启用开关T1和T2,其配置成启用或禁能前级放大器电路101和前级放大器电路102。确切来说,前级放大器电路101包含启用开关T1,其配置成根据启用信号EN1启用或禁能前级放大器电路101。前级放大器电路102包含启用开关T2,其配置成根据启用信号EN2启用或禁能前级放大器电路102。在实施例中,在接收器电路1141的操作模式期间可禁能前级放大器电路101和前级放大器电路102中的一个以节省功率消耗。

在这个实施例中,可禁能n型放大器电路(即,前级放大器电路101)和p型放大器电路(即,前级放大器电路102)中的一个以节省接收器电路1141的功率消耗而不降低接收器电路1141的性能。举例来说,当参考电压信号Vref相对高(即,在较高电压范围中)时,可禁能在高参考电压信号Vref下具有不良性能的p型放大器电路以节省功率消耗。类似地,当参考电压信号Vref相对低(即,在低电压范围中)时,可禁能在低参考电压信号Vref下具有不良性能的n型放大器电路以节省功率消耗。通过这种方式,减少接收器电路1141的功率消耗而不降低接收器电路1141的性能。

在一些实施例中,后级放大器电路103包含p型晶体管P31和p型晶体管P32以及n型晶体管N31和n型晶体管N32,其中p型晶体管P31和p型晶体管P32耦合到前级放大器电路101,且n型晶体管N31和n型晶体管N32耦合到前级放大器电路102。具体来说,p型晶体管P31和p型晶体管P32的栅极端子耦合到前级放大器电路101的连接节点ND11和连接节点ND12以从连接节点ND11和连接节点ND12接收前级放大信号1011_1和前级放大信号1011_2。n型晶体管N31和n型晶体管N32的栅极端子耦合到前级放大器电路102的连接节点ND21和连接节点ND22以从连接节点ND21和连接节点ND22接收前级放大信号1021_1和前级放大信号1021_2。

在这个实施例中,p型晶体管P31和p型晶体管P31的源极端子接收电源电压VDD,p型晶体管P31的漏极端子耦合到n型晶体管N32的栅极端子,且p型晶体管P32的漏极端子耦合到n型晶体管N32的漏极端子。此外,n型晶体管N31和n型晶体管N32的源极端子接收接地电压GND,n型晶体管N31的漏极端子耦合到晶体管P32的栅极端子,且n型晶体管N32的漏极端子耦合到p型晶体管P32的漏极端子。

在实施例中,后级放大器电路103配置成合并前级放大信号1011_1与前级放大信号1011_2以及前级放大信号1021_1与前级放大信号1021_2以产生输出信号OUT。输出信号OUT也可称为后放大信号,其是输入信号IN与参考电压信号Vref之间的差值的放大信号。接收器电路1141可将输入信号IN与参考电压信号Vref之间的差值放大一增益,其中根据包含在前级放大器电路101和前级放大器电路102以及后级放大器电路103中的n型晶体管和p型晶体管判定增益。在实施例中,根据p型晶体管P31、p型晶体管P32、p型晶体管P11、p型晶体管P12的大小和n型晶体管N31、n型晶体管N32、n型晶体管N21、n型晶体管N22的大小判定增益。晶体管的大小可参考晶体管的宽度、晶体管的长度或晶体管的长度和宽度的比。

在实施例中,p型晶体管P31和p型晶体管P32在大小上相同且统称为晶体管pm2,p型晶体管P11和p型晶体管P12在大小上相同且统称为晶体管pm1;n型晶体管N31和n型晶体管N32在大小上相同且统称为晶体管nm2;且n型晶体管N21和n型晶体管N22在大小上相同且统称为晶体管nm1。在这个实施例中,增益取决于晶体管pm2的大小和晶体管pm1的大小的比。增益也取决于晶体管nm2的大小和晶体管nm1的大小的比。

图4是示出根据一些实施例的接收器电路的操作方法的流程图。接收器电路1141包含一对前级放大器电路和后级放大器电路。在框401中,由一对前级放大器电路接收输入信号和参考电压信号。在框402中,由一对前级放大器电路根据输入信号与参考电压信号之间的差值输出第一前级放大信号和第二前级放大信号。在框403中,由后级放大器电路从一对前级放大器电路接收第一前级放大信号和第二前级放大信号。在框404中,由后级放大器电路根据第一前级放大信号和第二前级放大信号输出后放大信号。一对前级放大器电路包括:第一前级放大器电路,包含一对第一n型晶体管,其中一对第一n型晶体管的栅极端子分别接收输入信号和参考电压信号;以及第二前级放大器电路,包含一对第一p型晶体管,其中一对第一p型晶体管的栅极端子分别接收输入信号和参考电压信号。

综合来说,接收器电路1141都包含n型放大器电路和p型放大器电路,其中n型放大器电路在参考电压的较高电压范围下很好地操作,且p型放大器电路在参考电压的较低电压范围下很好地操作。通过这种方式,接收器电路1141可在较宽参考电压信号Vref的范围下很好地操作。此外,接收器电路1141可基于参考电压信号Vref的电平禁能n型放大器电路和p型放大器电路中的一个,由此减少接收器电路1141的功率消耗。

虽然已经详细描述本公开的实施例,但本公开不限于具体实施例,且在权利要求中公开的本公开的范围内可进行各种修改和改变。

- 存储器管理方法、存储器控制电路单元与存储器存储装置

- 选择电路、可配置的存储器存储系统及其操作方法

- 集成电路存储器设备及其操作方法

- 静态随机存取存储器及其写入辅助电路和写入操作方法

- 数据储存装置、存储器操作方法及操作指令执行方法

- 具备信息过滤检测功能的存储器、使用该存储器的信息检测方法、含有该存储器的装置、信息检测方法、存储器使用方法及存储器地址比较电路

- 行锤击防止电路系统、存储器装置和存储器装置操作方法