一种实现SSD主控RAID的SRAM访问装置

文献发布时间:2023-06-19 18:30:43

技术领域

本发明涉及存储领域,具体是一种实现SSD主控RAID的SRAM访问装置。

背景技术

如表1所示,根据一12nm片上SRAM的datasheet统计数据(4KB和8KB)可得以下结论:面积方面,SPSRAM(single port SRAM,单口SRAM)的面积远远小于同样尺寸的DPSRAM(dual port SRAM,双口SRAM),使用DPSRAM时使得所占芯片面积接近翻倍,性价比极低;时序方面,SPSRAM的最小时钟周期小于DPSRAM,即可以支持更高频率的数据访问;功耗方面,SPSRAM的静态电流也远小于同尺寸的DPSRAM。

Tcyc Minimum CLkcycletime

Tcd CLK to valid Q(data out put)

Wake up时间使用了:

tslpwk Wake up time for switching back to normal mode from SLP modeSLP→CEB

tdslpwk Wake up time for switching back to normal mode from DSLP modeDSLP→CEB

tsdwk Wake up time for switching back to normal mode from shut downmode SD→DSLP

表1

实现SSD主控RAID的一种方式就是需要对SRAM进行频繁读写,其时序要求是:对上一拍从sram中读出的数据与外部数据进行异或运算并且当拍写入sram上一拍的读出地址中;当拍从sram中读出的数据与外部数据进行异或运算下一拍写入sram当拍的读出地址中。既每一拍都有对sram的连续两个地址有读写操作。当外部数据连续进入时,sram可以连续写入及读出中间parity,保证流水效率。一种简单的实现方式是使用DPSRAM,因其有两套读写地址及数据接口,可以支持在一个clock cycle内对sram既读又写。

对dpsram的操作可参考表2:

表2

上表中,A0指代总条目为n的dpsram的第0地址,A(n-1)指代dpsram的第n-1地址),D(n-1)

但这种方式耗费sram面积功耗都较大,且最高频率受限,进而影响芯片成本及性能。

发明内容

针对现有双口SRAM实现RAID面积功耗较大且最高频率受限的缺陷,本发明提供一种实现SSD主控RAID的SRAM访问装置,使用两片SPSRAM以及相应的控制逻辑电路,在保证功能的前提下使芯片面积减小、功耗降低、频率提高。

为了解决所述技术问题,本发明采用的技术方案是:一种实现SSD主控中RAID的SRAM访问装置,其特征在于:包括两块单口SRAM以及与单口SRAM相连的逻辑控制电路,逻辑控制电路控制两块单口SRAM在同一时钟周期分别进行读或写操作,并且两块单口SRAM交替作为奇偶地址SRAM,作为奇地址SRAM时,进行奇地址数据的读或写,作为偶地址SRAM时,进行偶地址数据的读或写;逻辑控制电路包括奇偶标志逻辑电路、使能逻辑电路、写使能逻辑电路、地址多选器、读数据多路选择器和读数据缓存电路;

奇偶标志逻辑电路用于标志单口SRAM用作偶地址SRAM还是奇地址SRAM,奇偶标志逻辑电路的输入端连接start信号和init信号,受start信号触发翻转,并根据是否为init数据调整标志,奇偶标志逻辑电路的输出端连接至使能逻辑电路;使能逻辑电路的输入端与奇偶标志逻辑电路的输出信号、系统en信号、start信号相连,使能逻辑电路的输出端与单口SRAM的使能端口相连,用于根据系统en信号、start信号及奇偶标志决定是否使能单口SRAM;

写使能逻辑电路的输入端与奇偶标志逻辑电路的输出信号、写地址最低位信号、写使能信号相连,写使能逻辑电路的输出端与单口SRAM的写使能端口相连,用于根据奇偶标志和是否第一次进数选择是否对单口SRAM写使能;

地址多选器用于根据写使能信号选择系统写地址还是系统读地址作为sram的地址信号;

读数据缓存电路与单口SRAM读数据输出端相连,用于缓存从单口SRAM中读出的数据;

读数据多路选择器与两块单口SRAM读数据输出端、读数据缓存电路的输出端相连,用于从单口SRAM读数据、单口SRAM读数据缓存中选择一路数据输出,该数据即为当前系统地址所对应的上一轮数据校验计算结果(temp parity)。

进一步的,奇偶标志逻辑电路有两路,分别用于标志两块单口SRAM用作偶地址SRAM还是奇地址SRAM;

一路奇偶标志逻辑电路包括两路选择器MUX00、两路选择器MUX01、奇偶标志寄存器SRAM0_FLAG、两路选择器MUX02,两路选择器MUX00的输入端X0接上拉电源,两路选择器MUX00的输入端X1接地,两路选择器MUX00的选择信号端Sel接init信号,两路选择器MUX00的输出端连接至两路选择器MUX01的输入端X1,两路选择器MUX01的输入端X0连接两路选择器MUX02的输出端,两路选择器MUX01的选择信号端Sel接起始信号start,两路选择器MUX01的输出端连接至奇偶标志寄存器SRAM0_FLAG的输入端,奇偶标志寄存器SRAM0_FLAG的输出端Q连接至两路选择器MUX02的输入端X0和写使能逻辑电路,奇偶标志寄存器SRAM0_FLAG的输出端

另一路奇偶标志逻辑电路包括两路选择器MUX10、两路选择器MUX11、奇偶标志寄存器SRAM1_FLAG、两路选择器MUX12,两路选择器MUX10的输入端X0接上拉电源,两路选择器MUX10的输入端X1接地,两路选择器MUX10的选择信号端Sel接init信号,两路选择器MUX10的输出端连接至两路选择器MUX11的输入端X1,两路选择器MUX11的输入端X0连接两路选择器MUX12的输出端,两路选择器MUX11的选择信号端Sel接起始信号start,两路选择器MUX11的输出端连接至奇偶标志寄存器SRAM1_FLAG的输入端,奇偶标志寄存器SRAM1_FLAG的输出端Q连接至使能逻辑电路、写使能逻辑电路和两路选择器MUX12的输入端X0,奇偶标志寄存器SRAM1_FLAG的输出端

进一步的,使能逻辑电路有两路,分别用于使能两块单口SRAM,两路使能逻辑电路由与门AND00和或门OR00、与门AND10和或门OR10实现,与门AND00的一个输入端与奇偶标志寄存器SRAM0_FLAG的输出端

进一步的,写使能逻辑电路有两路,分别用于写使能两块单口SRAM,一路写使能逻辑电路包括异或门XOR0和与门AND01,异或门XOR0的一个输入端连接写地址信号的最低位,异或门XOR0的另一个输入端连接奇偶标志寄存器SRAM0_FLAG的输出端Q,异或门XOR0的输出端连接至与门AND01的一个输入端,与门AND01的另一个输入端连接系统写使能信号,与门AND01的输出端连接至单口SRAM0的写使能端口;

另一路写使能逻辑电路包括同或门XNOR1和与门AND11,同或门XNOR1的一个输入端连接写地址信号的最低位,同或门XNOR1的另一个输入端连接奇偶标志寄存器SRAM1_FLAG的输出端Q,同或门XNOR1的输出端连接至与门AND11的一个输入端,与门AND11的另一个输入端连接系统写使能信号,与门AND11的输出端连接单口SRAM1的写使能端口。

进一步的,地址多选器有两个,用于决定两块单口SRAM的地址信号,两个地址多选器为两路选择器MUX03和两路选择器MUX13,两路选择器MUX03的两个输入端分别连接写地址和读地址,两路选择器MUX03的选择信号端Sel连接一路写使能电路的输出,两路选择器MUX03的输出端连接SRAM0的地址输入端口;两路选择器MUX13的两个输入端分别连接写地址和读地址,两路选择器MUX13的选择信号端Sel连接另一路写使能电路的输出,两路选择器MUX13的输出端连接SRAM1的地址输入端口。

进一步的,读数据缓存电路有两路,分别用于缓存两块单口SRAM的读数据,两路读数据缓存电路由读数据寄存器SRAM0_RDATA_R、读数据寄存器SRAM1_RDATA_R组成,读数据寄存器SRAM0_RDATA_R与单口SRAM0的读数据输出端口相连,用于缓存单口SRAM0的读数据,读数据寄存器SRAM1_RDATA_R与单口SRAM1的读数据输出端口相连,用于缓存单口SRAM1的读数据。

进一步的,读数据多路选择器包括两路选择器MUX04及其选择逻辑电路、两路选择器MUX05及其逻辑选择电路、两路选择器MUX14及其选择逻辑电路、两路选择器MUX15及其选择逻辑电路;

两路选择器MUX04的选择逻辑电路包括与门AND02、首笔偶地址标识寄存器EVEN_1st和或门OR01,与门AND02的输入端分别连接SRAM0的写使能信号、SRAM1的写使能信号取反,与门AND02的输出端连接至首笔偶地址标识寄存器EVEN_1st的输入端,首笔偶地址地址标识寄存器EVEN_1st的输出端Q连接至或门OR01的一个输入端,或门OR01的另一个输入端连接系统写使能信号;

两路选择器MUX05的选择逻辑电路包括读地址最低位寄存器RDADDR_LSB_R0和同或门XNOR0,读地址最低位寄存器RDADDR_LSB_R0的输入端连接读地址中的最低位,读地址最低位寄存器RDADDR_LSB_R0的输出端Q连接至同或门XNOR0的一个输入端,同或门XNOR0的另一个输入端连接奇偶标志信号SRAM0_FLAG/Q;

两路选择器MUX14的选择逻辑电路包括与门AND12、首笔奇地址标识寄存器ODD_1st、或门OR11,与门AND12的输入端分别连接SRAM0的写使能信号取反、SRAM1的写使能信号,与门AND12的输出端连接至首笔奇地址标识寄存器ODD_1st的输入端,首笔奇地址标识寄存器ODD_1st的输出端Q连接至或门OR11的一个输入端,或门OR11的另一个输入端连接系统写使能信号;

两路选择器器MUX14的选择逻辑电路包括读地址最低位寄存器RDADDR_LSB_R1和异或门XOR1,读地址最低位寄存器RDADDR_LSB_R1的输入端连接读地址中的最低位,读地址最低位寄存器RDADDR_LSB_R1的输出端Q连接至异或门XOR1的一个输入端,异或门XOR1的另一个输入端连接奇偶标志信号SRAM1_FLAG/Q;两路选择器MUX04的输入端X1连接SRAM0的数据输出端口sram0_rdata,两路选择器MUX04的输入端X0连接读数据寄存器SRAM0_RDATA_R的输出端,两路选择器MUX04的信号选择端Sel连接或门OR01的输出端;两路选择器MUX04的输出端连接两路选择器MUX05的输入端X1,两路选择器MUX05的输入端X0接地,两路选择器MUX05的信号选择端Sel连接同或门XNOR0的输出端;

两路选择器MUX14的输入端X1连接SRAM1的数据输出端口sram1_rdata,两路选择器MUX14的输入端X0连接读数据寄存器SRAM1_RDATA_R的输出端Q,两路选择器MUX14的信号选择端Sel连接或门OR11的输出端;两路选择器MUX14的输出端连接两路选择器MUX15的输入端X1,两路选择器MUX15的输入端X0接地,两路选择器MUX15的信号选择端Sel连接异或门XOR1的输出端;

两路选择器MUX05、两路选择器MUX15的输出端分别连接至或门RDDATA_OR的输入端,或门RDDATA_OR的输出既对应当前系统读地址的读出数据(上一笔数据校验计算结果temp parity)。本发明的有益效果:本发明使用两片单口SRAM替换掉原来的双口SRAM,并增加硬件控制逻辑电路实现RAID功能中对SRAM的访问使用,控制逻辑电路由少量寄存器和多选器组成,面积远小于相同尺寸DPSRAM与SPSRAM的面积差值。由此可知,本发明在保证功能的前提下在整体上有使芯片面积减小,功耗降低,频率提高的突出效果。

附图说明

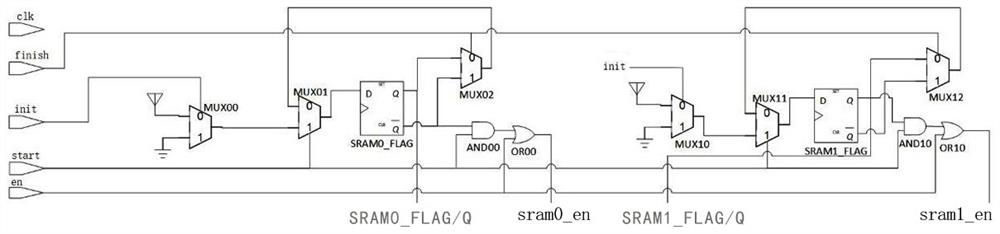

图1为本SRAM访问装置的电路图1;

图2为本SRAM访问装置的电路图2;

图3为本SRAM访问装置的电路图3。

具体实施方式

下面结合附图和具体实施例对本发明作进一步的说明。

实施例1

本实施例公开一种实现SSD主控RAID的SRAM访问装置,本装置由图1、2、3所示电路组成,包括两块单口SRAM以及与单口SRAM相连的逻辑控制电路,下面称两块单口SRAM为SRAM0和SRAM1,逻辑控制电路控制两块单口SRAM在同一时钟周期分别进行读或写操作,并且两块单口SRAM交替作为奇偶地址SRAM,作为奇地址SRAM时,进行奇地址数据的读或写,作为偶地址SRAM时,进行偶地址数据的读或写,从而实现RAID功能中对SRAM的访问使用。

逻辑控制电路包括奇偶标志逻辑电路、使能逻辑电路、写使能逻辑电路、地址多选器、读数据多路选择器和读数据缓存电路。

奇偶标志逻辑电路用于标志单口SRAM用作偶地址SRAM还是奇地址SRAM,奇偶标志逻辑电路的输入端连接start信号和init信号,受start信号触发翻转,并根据是否为init数据调整标志,init信号表示是否为第一轮,第一轮只是铺数,即对SRAM的操作只有写没有读,奇偶标志逻辑电路的输出端连接至使能逻辑电路。

使能逻辑电路的输入端与奇偶标志逻辑电路的输出信号、系统使能信号en、起始信号start相连,使能逻辑电路的输出端与单口SRAM的使能端口相连,用于根据系统使能信号en、起始信号start及奇偶标志决定是否使能单口SRAM。

写使能逻辑电路的输入端与奇偶标志逻辑电路的输出信号、写地址最低位信号、写使能信号相连,写使能逻辑电路的输出端与单口SRAM的写使能端口相连,用于根据奇偶标志和是否第一次进数选择是否对单口SRAM写使能。

地址多选器用于根据写使能信号选择系统写地址还是系统读地址作为sram的地址信号。

读数据缓存电路与单口SRAM读数据输出端相连,用于缓存从单口SRAM中读出的数据。

读数据多路选择器与两块单口SRAM读数据输出端、读数据缓存电路的输出端相连,用于从单口SRAM读数据、单口SRAM读数据缓存中选择一路数据输出,该数据即为当前系统地址所对应的上一轮数据校验计算结果(temp parity)。

如图1所示,奇偶标志逻辑电路有两路,分别用于标志SRAM0、SRAM1用作偶地址SRAM还是奇地址SRAM。

一路奇偶标志逻辑电路包括两路选择器MUX00、两路选择器MUX01、奇偶标志寄存器SRAM0_FLAG、两路选择器MUX02,两路选择器MUX00的输入端X0接上拉电源,两路选择器MUX00的输入端X1接地,两路选择器MUX00的选择信号端Sel接init信号,两路选择器MUX00的输出端连接至两路选择器MUX01的输入端X1,两路选择器MUX01的输入端X0连接两路选择器MUX02的输出端,两路选择器MUX01的选择信号端Sel接起始信号start,两路选择器MUX01的输出端连接至奇偶标志寄存器SRAM0_FLAG的输入端,奇偶标志寄存器SRAM0_FLAG的输出端Q连接至两路选择器MUX02的输入端X0和SRAM0的写使能逻辑电路,奇偶标志寄存器SRAM0_FLAG的输出端

另一路奇偶标志逻辑电路包括两路选择器MUX10、两路选择器MUX11、奇偶标志寄存器SRAM1_FLAG、两路选择器MUX12,两路选择器MUX10的输入端X0接上拉电源,两路选择器MUX10的输入端X1接地,两路选择器MUX10的选择信号端Sel接init信号,两路选择器MUX10的输出端连接至两路选择器MUX11的输入端X1,两路选择器MUX11的输入端X0连接两路选择器MUX12的输出端,两路选择器MUX11的选择信号端Sel接起始信号start,两路选择器MUX11的输出端连接至奇偶标志寄存器SRAM1_FLAG的输入端,奇偶标志寄存器SRAM1_FLAG的输出端Q连接至两路选择器MUX12的输入端X0、SRAM1的写使能逻辑电路以及SRAM1的使能逻辑电路,奇偶标志寄存器SRAM1_FLAG的输出端

如图1所示,使能逻辑电路有两路,分别用于使能SRAM0、SRAM1,两路使能逻辑电路由与门AND00和或门OR00、与门AND10和或门OR10实现,与门AND00的一个输入端与奇偶标志寄存器SRAM0_FLAG的输出端

如图1、2所示,写使能逻辑电路有两路,分别用于写使能SRAM0、SRAM1,一路写使能逻辑电路包括异或门XOR0和与门AND01,异或门XOR0的一个输入端连接写地址信号的最低位,异或门XOR0的另一个输入端连接奇偶标志寄存器SRAM0_FLAG的输出端Q,即信号SRAM0_FLAG/Q,异或门XOR0的输出端连接至与门AND01的一个输入端,与门AND01的另一个输入端连接系统写使能信号wr_en,与门AND01的输出端连接至单口SRAM0的写使能端口sram0_wr_en;另一路写使能逻辑电路包括同或门XNOR1和与门AND11,同或门XNOR1的一个输入端连接写地址信号的最低位,同或门XNOR1的另一个输入端连接奇偶标志寄存器SRAM1_FLAG的输出端Q,即信号SRAM1_FLAG/Q,,同或门XNOR1的输出端连接至与门AND11的一个输入端,与门AND11的另一个输入端连接系统写使能信号wr_en,与门AND11的输出端连接单口SRAM1的写使能端口sram1_wr_en。

如图2所示,地址多选器有两个,用于决定SRAM0、SRAM1的地址信号,两个地址多选器为两路选择器MUX03和两路选择器MUX13,两路选择器MUX03的两个输入端分别连接写地址和读地址,两路选择器MUX03的选择信号端Sel连接一路写使能电路即与门AND01的输出,两路选择器MUX03的输出端连接SRAM0的地址输入端口sram0_addr;两路选择器MUX13的两个输入端分别连接写地址和读地址,两路选择器MUX13的选择信号端Sel连接另一路写使能电路即与门AND11的输出,两路选择器MUX13的输出端连接SRAM1的地址输入端口sram1_addr。

如图2、3所示,读数据缓存电路有两路,分别用于缓存SRAM0、SRAM1的读数据,两路读数据缓存电路由读数据寄存器SRAM0_RDATA_R、读数据寄存器SRAM1_RDATA_R组成,读数据寄存器SRAM0_RDATA_R与单口SRAM0的读数据输出端口sram0_rdata相连,用于缓存单口SRAM0的读数据,读数据寄存器SRAM1_RDATA_R与单口SRAM1的读数据输出端口sram1_rdata相连,用于缓存单口SRAM1的读数据。

如图2、3所示,读数据多路选择器包括两路选择器MUX04及其选择逻辑电路、两路选择器MUX05及其逻辑选择电路、两路选择器MUX14及其选择逻辑电路、两路选择器MUX15及其选择逻辑电路。

两路选择器MUX04的选择逻辑电路包括与门AND02、首笔偶地址标识寄存器EVEN_1st和或门OR01,与门AND02的输入端分别连接SRAM0的写使能信号、SRAM1的写使能信号取反,与门AND02的输出端连接至首笔偶地址标识寄存器EVEN_1st的输入端,首笔偶地址地址标识寄存器EVEN_1st的输出端Q连接至或门OR01的一个输入端,或门OR01的另一个输入端连接系统写使能信号。

两路选择器MUX05的选择逻辑电路包括读地址最低位寄存器RDADDR_LSB_R0和同或门XNOR0,读地址最低位寄存器RDADDR_LSB_R0的输入端连接读地址中的最低位,读地址最低位寄存器RDADDR_LSB_R0的输出端Q连接至同或门XNOR0的一个输入端,同或门XNOR0的另一个输入端连接奇偶标志信号SRAM0_FLAG/Q。

两路选择器MUX14的选择逻辑电路包括与门AND12、首笔奇地址标识寄存器ODD_1st、或门OR11,与门AND12的输入端分别连接SRAM0的写使能信号取反、SRAM1的写使能信号,与门AND12的输出端连接至首笔奇地址标识寄存器ODD_1st的输入端,首笔奇地址标识寄存器ODD_1st的输出端Q连接至或门OR11的一个输入端,或门OR11的另一个输入端连接系统写使能信号。

两路选择器器MUX15的选择逻辑电路包括读地址最低位寄存器RDADDR_LSB_R1和异或门XOR1,读地址最低位寄存器RDADDR_LSB_R1的输入端连接读地址中的最低位,读地址最低位寄存器RDADDR_LSB_R1的输出端Q连接至异或门XOR1的一个输入端,异或门XOR1的另一个输入端连接奇偶标志信号SRAM1_FLAG/Q。

两路选择器MUX04的输入端X1连接SRAM0的数据输出端口sram0_rdata,两路选择器MUX04的输入端X0连接读数据寄存器SRAM0_RDATA_R的输出端,两路选择器MUX04的信号选择端Sel连接或门OR01的输出端;两路选择器MUX04的输出端连接两路选择器MUX05的输入端X1,两路选择器MUX05的输入端X0接地,两路选择器MUX05的信号选择端Sel连接同或门XNOR0的输出端。

两路选择器MUX14的输入端X1连接SRAM1的数据输出端口sram1_rdata,两路选择器MUX14的输入端X0连接读数据寄存器SRAM1_RDATA_R的输出端Q,两路选择器MUX14的信号选择端Sel连接或门OR11的输出端;两路选择器MUX14的输出端连接两路选择器MUX15的输入端X1,两路选择器MUX15的输入端X0接地,两路选择器MUX15的信号选择端Sel连接异或门XOR1的输出端;两路选择器MUX05、两路选择器MUX15的输出端分别连接至或门RDDATA_OR的输入端,或门RDDATA_OR的输出既对应当前系统读地址的读出数据(上一笔数据校验计算结果temp parity)。

读数据多路选择器用于从sram0读数据/sram0读数据缓存/sram1读数据/sram1读数据缓存四路中选择一路数据给系统作为当前系统地址读出的临时parity(数据校验计算结果)。因为sram0和sram1交替作为奇偶地址SRAM,也可以描述为:从奇地址sram读数据/奇地址sram读数据缓存/偶地址sram读数据/偶地址sram读数据缓存四路中选择一路数据给系统作为当前系统地址读出的临时parity(数据校验计算结果)。

基于本访问装置实现SSD存储中RAID访问spsram的方案如下:

首先在系统中对两块spsram进行混合交叉编址,即将系统地址的最低位LSB用来区分奇地址sram和偶地址sram,以下所述A0、A1等均是将系统地址去掉LSB之后某个spsram的实际地址。

其次,对于相同的系统地址,先发送读命令读出old temp parity(上一拍数据校验计算结果),再发送写命令写入将读出数据与外部数据异或后的new temp parity(新数据校验计算结果),相同地址的读写命令中间间隔一个时钟周期clock cycle(因为sram是写命令和写数据在同一拍,而读数据是在发出读命令的下一拍才有效)。对于奇数地址或者偶数地址sram中的任意地址,也要先读出才能再写入,否则上一笔的临时parity就被覆盖掉,出现功能错误。系统同时访问两个SRAM的时候,操作是1R1W(一读一写),这样才能做到数据连续读入写出。偶数地址sram和奇数地址sram各自的读写顺序有如下差别:偶数地址sram在第一个时钟周期发送读0地址命令,第二个时钟周期clock cycle读出0地址数据暂存在读数据缓存中,第三个时钟周期开始读写命令交叉进行;奇数地址sram第一个时钟周期空闲,从第二个时钟周期开始读写命令交叉进行。最终实现,相同地址(不看LSB)的数据从奇数地址sram读出经异或计算后写入到偶数地址sram中,反之从偶数地址sram中读出经运算写入到奇数地址sram中,读写之间间隔一个时钟周期。

再次,在将两块sram中的数据依序更新一遍之后,将两块sram在系统当中的编址彼此互换,再进行下一轮数据的raid运算(这样相当于new temp parity放在了与old tempparity完全相同的系统地址上)。互换方式即finish信号拉高使得各自的奇偶标志寄存器翻转。原来的奇数地址sram变为偶数地址sram,原来的偶数地址sram变为奇数地址sram。系统根据奇偶标志寄存器控制每块sram进行新一轮的读写操作。

当init为1时,代表是第一轮数据进入sram,此时只需要写sram,不读sram。

具体时序信息如表3所示,即奇数地址sram之某地址的数据被读出后,其与外部数据的异或结果写入到偶数地址sram的相同地址(曲线箭头所示),反之亦然。

表3

e0、o0分别指偶数地址sram的0地址、奇数地址sram的0地址;

D(0)

D(0)

与dpsram的时序图表(表2)相对比,n=2m,dpsram size为n,两块spsram size均为m。前者完成一轮emp parity刷新所用的clock cycle数为n+3,后者完成一轮tempparity刷新所用的时钟周期数为2m+3,二者完全相同。即本装置完全不影响ssd raid工作的效率。

本发明使用sp sram替换掉dp sram,增加一小部分硬件控制逻辑,在保证功能的前提下在整体上有使芯片面积减小,功耗降低,频率提高的突出效果。是ssd主控中raid实现上一项有意义的突破。

以上描述的仅是本发明的基本原理和优选实施例,本领域技术人员根据本发明做出的改进和替换,属于本发明的保护范围。