用于处理存储器访问请求的装置和方法

文献发布时间:2023-06-19 18:32:25

背景技术

本技术涉及一种用于处理存储器访问请求的装置和方法,尤其涉及一种用于在由该装置提供的互连器内处理此类存储器访问请求的技术。

互连器可用于将多个请求器元件与多个从属元件耦接。请求器元件可以被布置为发出存储器访问请求,并且存储器访问请求可以使该存储器访问请求所针对的从属元件被访问(例如,将数据写入从属元件或与该从属元件相关联的存储器设备,或者从该从属元件或从与该从属元件相关联的存储器设备读取数据)。

可以在互连器内设置中间元件,用于协调对由请求器元件发出的各种存储器访问请求的处理。中间元件可以被布置为跟踪它正在协调其处理的未决存储器访问请求,但是通常对于中间元件可以在任何时间点跟踪的未决存储器访问请求的数量存在有限的限制。一旦达到该限制,中间元件可能不得不拒绝接受由多个请求器元件发出的任何另外的存储器访问请求,直到已经跟踪的那些未决存储器访问请求中的一些已经完成。

已经发现,这种方法可能限制系统性能,例如在一个从属元件能够比另一个从属元件更快地处理存储器访问请求的情况下,例如由于它们的关联存储器设备具有不同的带宽能力。希望提供一种能够在此类情况下提高系统性能的技术。

发明内容

在一个示例性布置中,提供了一种装置,该装置包括:互连器,用于将多个请求器元件与多个从属元件耦接,该多个请求器元件被布置为发出存储器访问请求以供该多个从属元件处理;以及中间元件,其设置在该互连器内以充当对由该多个请求器元件经由该中间元件发出的这些存储器访问请求进行排序的串行化点;该中间元件包括跟踪电路以跟踪被该中间元件接受的这些存储器访问请求的处理;该中间元件还包括请求接受管理电路,该请求接受管理电路响应于该中间元件接收到给定存储器访问请求而被布置为识别该多个从属元件中用于该给定存储器访问请求的目标从属元件,并且根据该目标从属元件的带宽能力指示来确定该给定存储器访问请求是否将被该中间元件接受。

在另一示例性配置中,提供了一种处理存储器访问请求的方法,该方法包括:提供互连器以将多个请求器元件与多个从属元件耦接,该多个请求器元件被布置为发出这些存储器访问请求以供该多个从属元件处理;采用设置在该互连器内的中间元件以充当对由该多个请求器元件经由该中间元件发出的这些存储器访问请求进行排序的串行化点;在该中间元件的跟踪电路内跟踪被该中间元件接受的这些存储器访问请求的处理;以及响应于该中间元件接收到给定存储器访问请求,识别该多个从属元件中用于该给定存储器访问请求的目标从属元件,并且根据该目标从属元件的带宽能力指示来确定该给定存储器访问请求是否将被该中间元件接受。

在又一个示例性布置中,提供了一种装置,该装置包括:互连器构件,用于将多个请求器元件与多个从属元件耦接,该多个请求器元件被布置为发出存储器访问请求以供该多个从属元件处理;以及中间元件构件,其设置在该互连器构件内用于充当对由该多个请求器元件经由该中间元件构件发出的这些存储器访问请求进行排序的串行化点;该中间元件构件包括跟踪构件,该跟踪构件用于跟踪被该中间元件构件接受的这些存储器访问请求的处理;该中间元件构件还包括请求接受管理构件,该请求接受管理构件用于响应于该中间元件构件接收到给定存储器访问请求而识别该多个从属元件中用于该给定存储器访问请求的目标从属元件,并且用于根据该目标从属元件的带宽能力指示来确定该给定存储器访问请求是否将被该中间元件构件接受。

附图说明

将参考如附图所示的本技术的示例,仅以例示的方式进一步描述本技术,其中:

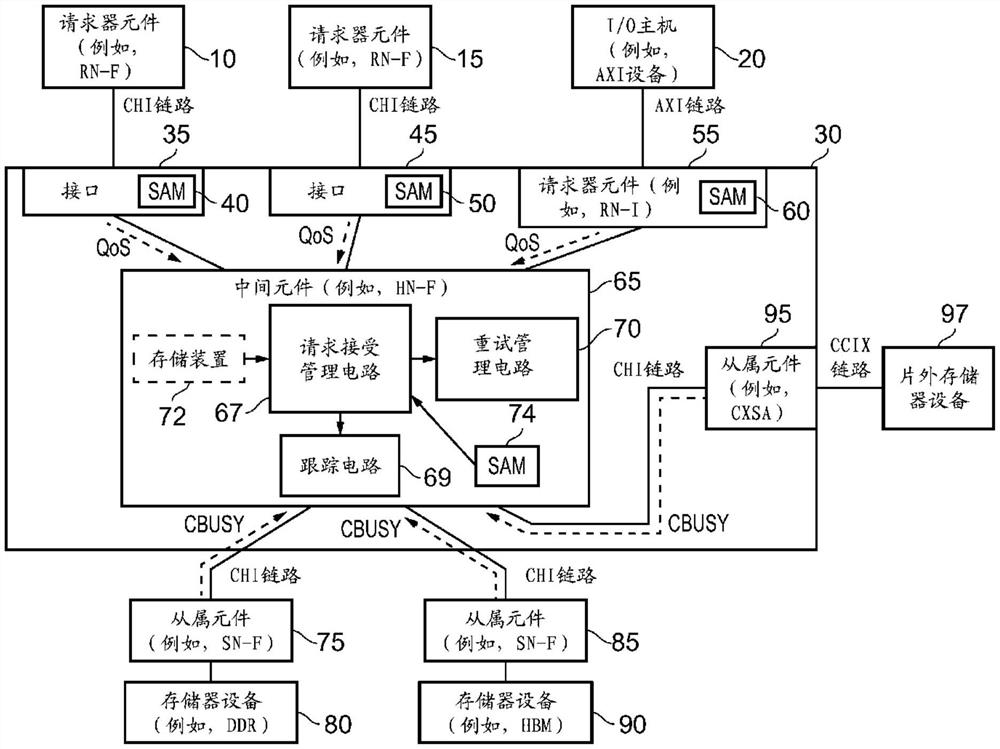

图1是根据一个示例性布置的系统的框图;

图2示意性地示出了根据一个示例性布置,如何将存储器地址空间划分为与不同类型的存储器相关联的不同区域;

图3是示出根据一个示例性布置的图1的中间元件的操作的流程图;

图4A和图4B是示出根据一个示例性配置,当决定是否接受新接收的存储器访问请求时,中间元件如何使用从各个从属元件提供给中间元件的忙碌信号的流程图;

图5A示出了在一个示例性布置中可以与每个请求器元件相关联地提供的系统地址映射的形式;

图5B是示出根据一个示例性布置,中间元件如何使用与存储器访问请求相关联地提供的服务质量信息来确定是否接受该存储器访问请求的流程图;

图6A示出了在一个示例性布置中可以与中间元件相关联地提供的系统地址映射的形式;

图6B是示出根据一个示例性布置,当决定是否接受存储器访问请求时,中间元件如何使用从诸如图6A所示的系统地址映射获得的静态带宽信息的流程图;

图7示意性地展示了根据一个示例性布置的中间元件的操作;

图8A通过具体示例示出了当不使用本文所述的技术时,中间元件内的共享跟踪结构可以如何限制整个系统带宽;并且

图8B通过具体示例示出了本文所述的技术的使用可以如何允许改进整体系统带宽管理。

具体实施方式

根据一个示例性具体实施,提供了一种具有用于将多个请求器元件与多个从属元件耦接的互连器的装置。该多个请求器元件被布置为发出存储器访问请求以供该多个从属元件处理。中间元件设置在该互连器内用于充当对由该多个请求器元件经由该中间元件发出的这些存储器访问请求进行排序的串行化点。因此,该中间元件可以充当该互连器内的点,在该点确定来自不同请求器元件的存储器访问请求之间的排序。在一些实例中,这些存储器访问请求(本文中也简称为访问请求)可指定存储器的可高速缓存区域内的地址,并且请求器元件中的一个或多个请求器元件可具有本地高速缓存。在这种情况下,该中间元件还可以充当一致性点,应用高速缓存一致性协议以确保每个请求器元件看到响应于其访问请求而被访问的数据的最新版本。

该中间元件包括跟踪电路以跟踪被该中间元件接受的这些存储器访问请求的处理。因此,该中间元件可以跟踪每个被接受的存储器访问请求,而该存储器访问请求在系统内处于等待状态。一旦从属元件已经执行了由该存储器访问请求指定的读操作或写操作(或至少确认将执行该写操作),或该中间元件已经直接处理了该访问请求而不需要联系该从属元件,则该中间元件可以被布置为停止跟踪关联的存储器访问请求,释放空间以跟踪另一存储器访问请求。在一些具体实施中,在该中间元件停止跟踪存储器访问请求之前,可能需要将任何所需的确认返回给该请求器元件(与读存储器访问请求的读数据一起)。

该中间元件内的该跟踪电路将具有有限的尺寸,因此对该中间元件在任何时间点可以跟踪的未决存储器访问请求的总数将存在限制。因此,有可能在该中间元件接收到新的存储器访问请求时,它可能不具有可用于跟踪该新的存储器访问请求的资源,并且在这种情况下,可能需要向发出该存储器访问请求的请求器元件发信号通知该存储器访问请求在当前时间不能被接受。例如,这可以使该请求器元件在适当的时候执行该存储器访问请求的重试。

然而,这种方法在某些情况下可能导致某些可用系统带宽的利用不足。例如,各种从属元件可能具有不同的能力,特别是某些从属元件可能能够比其他从属元件更快地处理存储器访问请求,例如由于关联存储器设备的带宽能力。因此,在这种情况下,可能以较快从属元件之一为目标的存储器访问请求可能被该中间元件拒绝,即使该较快从属元件具有接收该新的存储器访问请求并处理该新的存储器访问请求的能力。根据本文所述的技术,采用一种机制来寻求减少这种情况出现的机会。

具体地,根据本文所述的技术,该中间元件还包括请求接受管理电路,该请求接受管理电路响应于该中间元件接收到给定存储器访问请求而被布置为识别该多个从属元件中用于该给定存储器访问请求的目标从属元件。此外,该请求接受管理电路然后根据该目标从属元件的带宽能力指示来确定该给定存储器访问请求是否将被该中间元件接受。

通过这种方法,可以根据用于新接收的存储器访问请求的目标从属元件并且特别地考虑可以用于指示该目标从属元件的带宽能力的信息来改变用于决定是否接受该存储器访问请求的标准。例如,可以使用这种方法来抑制跟踪电路资源可用于跟踪以较慢从属元件为目标的存储器访问请求的程度,以便寻求在该跟踪电路内为以较快从属元件为目标的存储器访问请求保留可用空间。通过这种方法,可能出现这样的情况:如果新接收的存储器访问请求以一个从属元件为目标,则该存储器访问请求可以被中间元件接受,而如果该存储器访问请求以不同的从属元件为目标,则该存储器访问请求可能已经被拒绝。已经发现,这种方法可以使整个系统的带宽得到更有效的利用。

在确定给定存储器访问请求不被该中间元件接受的情况下,有多种方式可以处理该情况。在一个示例性具体实施中,该装置还包括重试管理电路,该重试管理电路被布置为当该请求接受管理电路指示给定存储器访问请求将不被接受时,与发出该给定存储器访问请求的请求器元件进行通信,以便为该给定存储器访问请求实施重试机制。重试机制可以采取多种形式。例如,在由该重试管理电路通知该给定存储器访问请求不被接受时,相关请求器元件可以被布置为周期性地重试该存储器访问请求,或者执行某种轮询操作,以便寻求确定该中间元件在其跟踪电路中何时将具有接收该存储器访问请求的能力。作为另一示例性方法,该请求器元件可以等待,直到该中间元件在适当的时候提供静态许可信号,该静态许可信号有效地保证该请求器元件将在该中间元件的跟踪电路资源中为该给定存储器访问请求提供空间,此时该请求器元件随后将重新发出该存储器访问请求。

在一个示例性具体实施中,也可以在该中间元件和各种从属元件之间采用类似的重试机制,并且因此如果从属元件不能接受由该中间元件传播给它的存储器访问请求,则重试信号可以从该从属元件发出给该中间元件,以使该中间元件在适当的时候重试将该存储器访问请求传播到该从属元件。

每个目标从属元件的带宽能力可以通过各种方式识别。在一个示例性具体实施中,每个从属元件具有关联存储器设备,并且该目标从属元件的带宽能力可取决于该关联存储器设备。例如,该目标从属元件的带宽能力可取决于该关联存储器设备的存储器类型。具体地,不同类型的存储器可具有不同的存取速度,并且这将影响关联目标从属元件可处理存储器访问请求的速度。

存在多种方式,其中该请求接受管理电路可以被布置为确定该目标从属元件的带宽能力指示。然而,在一个示例性具体实施中,该请求接受管理电路参考至少一个信息源导出该目标从属元件的该带宽能力指示。

信息源可采取多种形式,并且实际上当寻求导出该目标从属元件的该带宽能力指示时,该请求接受管理电路可参考多个不同的信息源。

在一个示例性具体实施中,该至少一个信息源包括由该中间元件从该多个从属元件接收的信息信号,并且该请求接受管理电路被布置为使用该信息信号来导出从属元件中的每个从属元件的该带宽能力指示。因此,根据这种方法,由从属元件持续提供的信息可以用于维护每个从属元件的带宽能力指示,因此使得能够基于在使用期间由从属元件接收的信息来进行带宽能力指示的动态调整。

信息信号可以采取各种形式,但是在一个示例性具体实施中包括由每个从属元件发出的忙碌信号,以识别该从属元件的忙碌程度。因此,根据这种具体实施,从属元件的实际忙碌程度可以用于影响以该从属元件为目标的另外的存储器访问请求是否将被该中间元件接受。例如,这允许当该从属元件不太忙时接受以该从属元件为目标的新的存储器访问请求,但是当知道该从属元件的忙碌程度高于某个阈值程度时,阻止接受以该从属元件为目标的新的存储器访问请求。

在一个示例性具体实施中,该跟踪电路可以具有用于跟踪存储器访问请求的多个条目,并且该请求接受管理电路可以被布置为当在该多个条目中存在空闲条目时,确定该给定存储器访问请求将被该中间元件接受,并且该目标从属元件的该带宽能力指示指示该目标从属元件在低于给定忙碌阈值程度下操作。

虽然可以为每个目标从属元件使用单个阈值程度,但是在另选的具体实施中,如果需要,可以使用多个阈值,以便允许在接受对特定目标从属元件的所有存储器访问请求的点和临时拒绝对该目标从属元件的所有存储器访问请求的点之间使用更分等级的方法。

存在多种方式,其中该请求接受管理电路可以跟踪由从属元件接收的信息信号。在一个示例性具体实施中,该装置具有存储装置,用于维护从属元件中的每个从属元件的带宽能力指示,并且该请求接受管理电路被布置为根据所接收的信息信号在该存储装置内维护从属元件中的每个从属元件的带宽能力指示。因此,该请求接受管理电路可以在从每个从属元件接收信息信号时基于信息信号更新该存储装置的内容。

虽然在一个示例性具体实施中,该请求接受管理电路可以被布置为仅利用从每个从属元件接收的最近的信息信号,但是在另选的具体实施中,该请求接受管理电路可以被布置为根据在先前所选时间段内从每个从属元件接收的信息信号来维护该从属元件的带宽能力指示。通过这种方法,可以基于在一段时间内接收到的信息信号,对每个从属元件的忙碌程度进行平均化。

作为使用从从属元件接收的信息信号的替代或补充,该至少一个信息源可包括由该中间元件与给定存储器访问请求相关联地接收的服务质量指示。根据这种方法,各个请求器元件可以将服务质量指示信息附加到每个发出的存储器访问请求,该服务质量指示用于影响该请求接受管理电路关于是否应该接受任何特定的存储器访问请求所做的决定。

如前所述,该跟踪电路可以具有用于跟踪存储器访问请求的多个条目。对于每个服务质量指示,可以定义关联阈值,该关联阈值识别该跟踪电路内能够同时用于跟踪具有该服务质量指示的存储器访问请求的条目数量。该请求接受管理电路然后被布置为当考虑到给定存储器访问请求的该服务质量指示的该关联阈值,在该跟踪电路内没有可用条目时,确定该给定存储器访问请求将被拒绝。因此,纯粹作为说明性示例,如果对于特定的接收到的存储器访问请求,该存储器访问请求具有关联服务质量指示,对于该服务质量指示,确定最多50%的条目可用于跟踪具有该服务质量指示的存储器访问请求,则如果50%的条目已用于跟踪具有该服务质量指示的存储器访问请求,则可拒绝该存储器访问请求,即使在该跟踪电路中仍然存在可用的空闲条目。这种方法可以例如用于确保在该跟踪电路内保留空间,以跟踪随后接收到的可能具有较高服务质量要求的存储器访问请求。

存在可以确定服务质量指示的多种方式。例如,可以与每个请求器元件相关联地提供地址映射电路,以将由该请求器元件发出的存储器访问请求指定的存储器地址转换为用于通过互连器路由该存储器访问请求的目标标识符。例如,当该存储器访问请求指定分配给前述从属元件之一的存储器地址空间内的存储器地址时,该目标标识符可以识别该存储器访问请求将被路由到的中间元件。该地址映射电路可以被布置为提供用于不同存储器地址范围的存储器类型信息,例如以识别用于这些不同存储器地址范围的存储器设备的类型,这又可以提供访问速度指示。然后可以基于用于存储器地址范围(包括由存储器访问请求指定的存储器地址)的存储器类型信息来确定服务质量指示。服务质量指示信息可以直接在该地址映射电路内编码,或者可另选地,可以基于从该地址映射电路提取的存储器类型信息来导出服务质量指示信息。

作为前述信息信号和服务质量指示的替代或补充,该至少一个信息源可包括由该中间元件确定的至少一个从属元件属性。这种从属元件属性可以以多种方式确定。例如,该地址映射电路可与该中间元件相关联,该中间元件用于为每个所接收的存储器访问请求确定目标从属元件。该地址映射电路还可以提供每个从属元件的至少一个从属元件属性,因此当为接收到的存储器访问请求确定目标从属元件时,该中间元件可以从该地址映射电路中检索这种从属元件属性。

该至少一个从属元件属性可以采取多种形式,但是在一个示例性具体实施中包括从属元件的带宽指示值。在一个特定的示例性具体实施中,该带宽指示值可以是静态值,因此可以预先确定并且然后在该装置的使用期间引用该静态值。带宽指示值可以采取多种形式,但在一个示例中取决于与从属元件相关联的存储器设备的存储器类型。因此,带宽指示值可以例如考虑诸如该存储器设备的访问速度的信息,这可以取决于所使用的特定类型的存储器。

当使用此类带宽指示值时,则对于每个此类带宽指示值,可以定义关联阈值,该关联阈值识别该跟踪电路内能够同时用于跟踪目标从属元件具有该带宽指示值的存储器访问请求的条目数量。该请求接受管理电路然后可以被布置为当考虑到给定存储器访问请求的目标从属元件的带宽指示值的关联阈值,在该跟踪电路内没有可用条目时,确定该给定存储器访问请求将被拒绝。因此,以举例的方式,对于以相对快的从属元件为目标的存储器访问请求,可以将关联阈值设定得较高,并且对于以相对慢的从属元件为目标的存储器访问请求,可以将关联阈值设定得较低。这使得该中间元件的跟踪电路资源可以被用来跟踪相对慢的存储器访问请求的程度得到控制,以便寻求保留可用空间来接收以较快存储器为目标的新的内存访问请求。这种方法可提高整体系统带宽利用率。

现在将参考附图描述特定示例。

图1是根据一个示例性具体实施的系统的框图。该装置包括经由互连器30耦接到多个从属元件75、85、95的多个请求器元件10、15、55。虽然从属元件可采取多种形式,但出于本文讨论的目的,考虑用于访问不同存储器设备的从属元件。因此,从属元件75可连接到存储器设备80,在此示例中,该存储器设备可采取双倍数据速率(DDR)存储器的形式,而从属元件85连接到另一存储器设备90,该存储器设备可例如采取高带宽存储器(HBM)的形式。作为另一示例,从属元件95可被布置为提供到片外存储器97的链路(例如,使用CCIX链路,其是高性能低延时的芯片到芯片接口),并且片外存储器可由又一类型的存储器设备来实现。当使用CCIX链路时,从属元件95可以被称为CXSA元件。

在互连器30内,可以提供多个中间元件,这些中间元件可以用作对请求器元件发出的访问请求进行排序的串行化点。在图30所示的示例中,中间元件65被提供作为从以从属元件75、85、95为目标的任何请求器元件10、15、55发出的访问请求的串行化点。本文中,诸如中间元件65的中间元件也可以被称为归属节点。

互连器30提供通信信道,用于支持每个请求器元件和各个归属节点之间的通信,以及用于支持归属节点和关联从属元件之间的通信。

在图1所示的示例中,示出了两种类型的请求器元件,本文中称为全一致性请求器10、15和输入/输出(I/O)一致性请求器55。诸如图1所示的元件10或元件15的全一致性请求器可以具有关联的本地硬件一致性高速缓存,并且可以被布置为经由关联接口35、45连接到互连器。

由涉及可高速缓存存储器地址的任何请求器元件10、15、55发出的访问请求将经由全一致性归属节点来路由,并且在图1的示例中,假设中间元件65实际上是全一致性归属节点。全一致性归属节点将不仅充当访问请求的串行化点,而且还将充当一致性点,并且因此可以实现高速缓存一致性协议,以便确保发出与可高速缓存存储器地址相关的访问请求的请求器将看到数据的最新版本。典型地,这种一致性归属节点将包括监听控制电路,用于寻求跟踪哪些本地高速缓存具有在特定地址区域内的高速缓存数据,从而找出哪些本地高速缓存需要受到监听操作以便实现高速缓存一致性协议。

与全一致性请求器元件10、15相反,诸如元件55的I/O一致性请求器元件不包括硬件一致性高速缓存,并且不需要关联监听功能来响应监听请求。

虽然未在图1中示出,但是互连器30可包括不提供一致性点并且不能处理可监听请求的非一致性归属节点。这些可以例如在访问存储器或外围设备或设备存储器的不可高速缓存区域时使用。

该系统还可以包括两种不同类型的从属元件,即可以耦接到全一致性归属节点的从属元件和可以耦接到非一致性归属节点的从属元件。在本文所示的示例中,归属节点65是全一致性归属节点,因此从属元件75、85、95是用于连接到全一致性归属节点的类型。然而,本文所述的技术也可以相对于非一致性归属节点来应用,在这种情况下,从属元件将是用于连接到非一致性归属节点的类型。不管归属节点是否完全一致,当用于访问不同类型的存储器的多个从属元件连接到同一归属节点时,本文描述的技术可提高整体系统带宽利用率。

虽然本文所述的技术可以用于各种类型的互连器,但是出于以下讨论的目的,将假设互连器30使用由Arm Limited(Cambridge,United Kingdom)开发的高级微控制器总线架构(AMBA),并且特别地使用AMBA 5CHI(一致性集线器接口)体系结构规范。根据该规范,全一致性请求器元件被称为RN-F(全一致性请求节点),并且全一致性归属节点被称为HN-F(全一致性归属节点)。根据上述规范,I/O一致性请求器元件被称为RN-I(I/O一致性请求节点),并且此类请求节点被布置为仅生成由互连协议定义的事务的子集,并且不需要监听功能。类似地,非一致性归属节点在AMBA 5CHI体系结构规范中被称为HN-I。此类归属节点可以被布置为处理由协议定义的事务的有限子集,并且在充当串行化点时,不提供一致性点并且不能处理可监听请求。类似地,连接到一致性归属节点的从属元件(也称为从属节点)被称为SN-F,而连接到非一致性归属节点的从属元件被称为SN-I。

在图1所示的示例中,I/O一致性请求器55可以被示为互连器的一部分,并且经由外部链路连接到上游主设备,例如I/O主设备20。虽然互连器30可以根据上述CHI体系结构规范来操作,并且任何已连接的全一致性请求器10、15可以使用图1所示的CHI链路来连接,但是诸如I/O主设备20的主设备通常可以使用不同的通信协议,并且将经由使用该其他协议的链路来连接到I/O一致性请求器55。在图1所示的示例中,假设I/O主元件20使用由ArmLimited(Cambridge,United Kingdom)开发的AMBA AXI协议规范,并经由AXI链路连接到互连器30。

通过互连器的访问请求的路由是在系统地址映射(SAM)部件的控制下进行的,并且可以与每个请求器元件相关联地提供SAM。如图1所示,对于诸如请求器10、15的全一致性请求器,关联SAM 40、50可以设置在由互连器30为该请求器元件提供的接口35、45内,而对于诸如请求器元件55的I/O一致性请求器,关联SAM 60在一个示例性具体实施中可以作为该请求器元件的一部分提供。

对于每个请求器元件,关联SAM用于将由该请求器元件发出的访问请求指定的存储器地址转换为目标标识符,该目标标识符指示访问请求将经由通信信道路由到的完成器元件。在图1所示的示例中,去往从属元件75、85、95之一的访问请求将经由中间元件65被路由,并且因此对于此类地址,与请求器元件相关联的SAM将把中间元件65标识为完成器元件。该中间元件(归属节点)然后将处理所接收的访问请求,并且如果必要,将该访问请求传播到所需的从属元件。对于该辅助通信,归属节点可以被视为请求器,而从属元件可以被视为完成器,并且如图1所示,归属节点65可包括其自己的SAM 74,用于确定访问请求应当被传播到的适当的从属元件。

当使用诸如图1所示的方法时,应当理解,以任何从属元件75、85、95为目标的访问请求将通过归属节点65传播。归属节点65具有跟踪电路69,该跟踪电路用于跟踪由归属节点接受的所有未决存储器访问请求的处理。跟踪电路可能需要跟踪这些存储器访问请求直到它们已经完成,例如直到确认已经返回给请求器元件以确认存储器访问已经执行,这也可能涉及将读数据返回到请求器元件用于读访问请求。

跟踪电路69将仅能够跟踪有限数量的存储器访问请求。因此,在从请求器元件10、15、55之一接收到新的存储器访问请求,但是跟踪电路资源已经被充分利用来跟踪现有的未决存储器访问请求的情况下,可能需要拒绝新的存储器访问请求。然后,重试管理电路70可用于对新接收的存储器访问请求调用重试机制。具体地,新接收的存储器访问请求将被有效地拒绝,并相应地通知请求器元件。然而,重试机制将用于使得能够在稍后的时间点重试存储器访问请求。重试机制可以采取多种形式,但是例如可以涉及请求器元件周期性地重试存储器访问请求,或者执行一些轮询操作以便确定归属节点65何时可用于接收存储器访问请求。另选地,请求器元件可被布置为仅仅等待,直到它随后从归属节点65接收到静态许可信号,该静态许可信号识别跟踪电路资源69中有可用空间来接收重试的存储器访问请求。

然而,可能出现的情况是:这种方法可能导致系统内的可用带宽得不到被利用。例如,各种存储器设备80、90、97可以不同速度操作,并且因此可具有用于处理存储器访问请求的不同带宽能力。这又将影响与这些存储器设备相关联的从属元件75、85、95可处理从归属节点65接收的存储器访问请求的带宽。本文中,连接到关联存储器设备的此类从属元件将被称为存储器控制器,并且应当理解,当这些存储器控制器与不同的存储器设备相关联时,各个存储器控制器可以处理存储器访问请求的速度可以变化。具体地,与连接到较慢存储器设备的存储器控制器相比,连接到相对高速的存储器设备的存储器控制器通常能够在特定的时间段内处理更多的访问请求。

在不使用本文所述的技术的情况下,可容易地出现跟踪电路69得到完全利用并且因此在一段时间内不能接受新的存储器访问请求而不管这些存储器访问请求以哪个存储器设备为目标的情况。因此,可能的情况是:例如,新接收的存储器访问请求以相对高速的存储器设备为目标,该相对高速的存储器设备的关联存储器控制器可能具有处理该存储器访问请求的能力,但是,由于跟踪电路69被充分利用来处理现有的存储器访问请求,所以该存储器访问请求可能经受重试机制。因此,存在的可能性是:以相对慢的存储器为目标的存储器访问请求可以使用不成比例地大量的跟踪电路资源,并且实际上阻止以较快存储器设备为目标的其他存储器访问请求的有效处理。这会导致对整体可用带宽的低效利用,降低系统性能和存储器效率。

根据本文所述的技术,如图1所示,通过使用作为归属节点65的一部分而提供的请求接受管理电路67来缓解该问题。具体地,请求接受管理电路67的布置使得响应于归属节点65接收到新的存储器访问请求,请求接受管理电路识别多个从属元件75、85、95中用于该存储器访问请求的目标从属元件,并且然后根据该目标从属元件的带宽能力指示来确定是否接受该存储器访问请求。通过这种方法,能够确保一定比例的跟踪电路资源维护可用于处理以较快存储器设备为目标的访问请求,以便寻求更有效地使用整体存储器带宽。

存在各种方式可以将请求接受管理电路67布置为获得各种从属元件的带宽能力指示,这些将在后面详细讨论。然而,总之,从属元件本身能够持续提供信息信号,指示它们用于处理存储器访问请求的可用带宽。此类信息信号可以例如采取忙碌信号(在图1中称为CBUSY信号)的形式,其提供每个从属元件的忙碌程度的指示。存储装置72可由请求接受管理电路67用来跟踪在一段时间内从每个从属元件接收到的忙碌信号,例如通过在选定的先前时间段内维护每个从属元件的平均忙碌程度。这使得能够在不同的从元件之间动态划分跟踪电路69中的可用资源,同时考虑到从属元件的相对忙碌程度。因此,以举例的方式,如果特定从属元件的忙碌水平超过给定阈值,则请求接受管理电路可被布置为拒绝以该从属元件为目标的后续访问请求,直到该从属元件的忙碌程度下降到该阈值以下为止。

作为可由请求接受管理电路67用来获得带宽能力指示的信息的另一示例,服务质量(QoS)信号可由归属节点65与每个新的存储器访问请求相关联地接收。对于每个可能的QoS等级,请求接受管理电路可以具有定义的关联阈值,该关联阈值识别跟踪电路69内可同时用于跟踪具有该QoS等级的存储器访问请求的条目数量。因此,以举例的方式,与具有较低QoS等级的存储器访问请求可使用的跟踪电路资源的比例相比,具有相对较高QoS等级的存储器访问请求可使用较大比例的跟踪电路资源。此外,可考虑与各种从属元件相关联的存储器设备的存储器类型来选择QoS等级,使得例如较高的QoS等级与较快存储器设备相关联。

作为可用于向请求接受管理电路67提供目标从属元件的带宽能力指示的另一示例性方法,可以补充归属节点65内的SAM 74,以提供每个从属元件的一个或多个从属元件属性。因此,当参考SAM 74以便为新接收的存储器访问请求确定目标从属元件时,还可检索此类从属元件属性并且然后用来决定是否接受存储器访问请求。作为可在SAM内维护的从属元件属性的示例,可为每个从属元件提供静态带宽指示值,指示该从属元件的带宽能力。然后可以为每个静态带宽指示值定义不同的阈值,以识别跟踪电路69内可同时用于跟踪目标从属元件具有该静态带宽指示值的存储器访问请求的条目数量。如同前述基于QoS的机制一样,这可以使可用于以相对快的存储器为目标的存储器访问请求的条目的比例高于跟踪电路内可用于以较慢存储器为目标的存储器访问请求的条目的比例,因此通过延迟以较快存储器设备为目标的存储器访问请求的处理,降低了跟踪电路资源在处理对慢存储器设备的访问请求中被充分利用的可能性,从而降低了对性能的影响。

图2示意性地示出了如何将存储器地址空间100视为包括多个区域105、110、115。这些区域可以被分配给系统内的不同存储器设备,并且因此例如区域105可以与DDR存储器80相关联,区域110可以与HBM存储器90相关联,区域115可以与片外存储器97相关联,等等。

应当理解,可将多个区域分配给特定存储器设备,并且这鞋区域不一定需要占据存储器地址空间内的相邻地址。因此,纯粹以举例的方式,存储器的第一区域和与该第一区域不相邻的存储器的一个或多个其他区域可以被共同分配为DDR存储器80的存储器地址空间。使用前述SAM机制,当存储器地址由与存储器访问请求相关联的请求器元件指定时,可以确定该地址落入存储器地址空间的哪个区域,并因此确定该地址映射到哪个存储器设备。这可以用于确定哪个归属节点65将接收该请求,并且在适当的时候,如果归属节点不能直接处理该存储器访问请求,则将联系哪个从属元件来处理该存储器访问请求(例如参考数据的高速缓存副本)。

图3是示出根据一个示例性具体实施的在接收到新的存储器访问请求时图1的归属节点65(特别是其中设置的请求接受管理电路67)的操作的流程图。在步骤120,确定是否已从请求器元件10、15、55中的一者接收到新的存储器访问请求,并且如果是,则该过程进行到步骤125,在该步骤识别用于该存储器访问请求的目标从属元件。如上所述,该过程通常涉及对归属节点65内的SAM 74的参考。

另外,随后在步骤130确定目标从属元件的带宽能力指示,并且如上所述,可存在许多用于进行此确定的机制,例如参考从从属元件接收的CBUSY信号、参考与存储器访问请求相关联地提供的QoS信号或参考当在步骤125识别目标从属元件时从SAM 74获得的静态带宽指示值。

然后在步骤135,在给定目标从属元件的带宽能力指示的情况下,确定是否接受存储器访问请求。如果否,则在步骤145,重试管理电路70用于激活重试机制,此时请求被有效地拒绝,并且需要在稍后由请求器元件重试。然而,如果在步骤135确定要接受存储器访问请求,则在步骤140将该存储器访问请求添加到跟踪器电路69的可用条目,并且此后以正常方式进行处理。在一个示例性具体实施中,图3的上述步骤可以由归属节点65的请求接受管理电路67来执行,其中请求接受管理电路或者在步骤140与跟踪电路69通信以使跟踪器电路内的条目被分配用于存储器访问请求,或者在步骤145与重试管理电路70通信以使重试机制被激活。

图4A示出了在一个示例性具体实施中由从属元件75、85、95提供的CBUSY信号可以如何由归属节点65使用。在步骤150,从不同的从属元件中监控CBUSY信号,并且在步骤155,根据所接收的CBUSY信号计算每个从属元件的带宽能力指示,并且在考虑新的存储器访问请求时由请求接受管理电路将其维护在存储器72中以供以后参考。虽然在一个示例性布置中存储装置可以仅用于维护来自每个从属元件的最新CBUSY指示,但是在一个示例性具体实施中,对在一段时间上接收的CBUSY信号进行平均,以便提供在选定宽度的先前时间窗口内每个存储器设备的忙碌程度指示。

图4B是示出当使用利用图4A的方法维护的CBUSY信息时,如何实施在图3的步骤135做出的决定的流程图。在步骤160,确定跟踪器电路69中是否有任何空闲条目,如果没有,则在步骤165通过激活重试机制来拒绝该请求。然而,假设在跟踪器电路中存在至少一个空闲条目,则过程进行到步骤170,在该步骤,确定从存储装置72获得的目标从属元件的带宽能力指示是否指示目标从属元件正在低于忙碌阈值程度下操作。如果不是,则在步骤165再次拒绝该请求,否则在步骤175接受该请求,然后分配跟踪电路内的条目用于保存存储器访问请求的细节。当使用本文所述的技术时,已发现这可显著减少跟踪器电路中不存在任何空闲条目的机会,并且因此可通过更好地利用各种存储器设备的带宽能力来增加整体系统性能。

通过使用上述CBUSY指示,这使得能够动态划分跟踪电路的可用资源,同时考虑到各种从属元件的相对忙碌程度。一旦从属元件开始表现出高于某一阈值的忙碌程度,则请求接受管理电路可以临时拒绝以该从属元件为目标的后续存储器访问请求,从而一旦该从属元件的忙碌程度已经降低,则可以重试这些存储器访问请求。因此,这在跟踪电路内为存储器访问请求保持可用空间,识别可能不太忙碌的其他从属元件,并且因此可处于更好的位置来处理另外的访问请求。

作为使用CBUSY信号来提供带宽能力指示的替代或补充,可以向归属节点65提供与每个新的存储器访问请求相关联的QoS信号。具体地,基于从与发出每个新的存储器访问请求的请求器元件10、15、55相关联的SAM40、50、60检索的信息,可以与该存储器访问请求相关联地添加此类QoS信息。

图5A是示意性地示出了可以在系统地址映射40、50、60中为每个请求器元件10、15、55提供的信息的图。SAM 200包括多个条目205,并且每个条目提供多个字段210、215、220。字段210用于识别地址范围,并且各种条目205的字段210中的信息可用于识别存储器地址空间内的各种不同可编程区域。在一个示例性具体实施中,地址空间的划分不一定是静态的,因此在不同的时间点可以在条目205内定义不同的地址范围。

对于在特定条目205的字段210内识别的地址范围,对应字段215可用于指定目标标识符(目标ID),该目标标识符用于指示要用于该地址范围内的访问的完成器元件。对于以图1中所示的存储器设备80、90、97内的地址为目标的访问,假定这些访问经由归属节点65路由,并且因此由目标ID识别的完成器元件将为归属节点65。因此,这确保了所有此类访问请求从接口35、45或请求器元件55通过互连器的通信信道传播到归属节点65供后续处理。

如图5A所示,第三字段220可用于指定与字段210中的地址区域相关联的存储器设备的存储器类型。然后,例如通过将较高的QoS值与涉及较快存储器的存储器类型相关联,可以使用该存储器类型信息来确定存储器访问请求的合适的QoS值。虽然可以基于从字段220获得的存储器类型信息来执行QoS等级的确定,但是如果需要,可以在存储器类型字段220中填充实际的QoS值,以便直接从SAM 40、50、60内的查找获得QoS值。

图5B示出了可由请求接受管理电路67执行以基于新接收的存储器访问请求的指定QoS值来确定是否接受该存储器访问请求的过程。在步骤250,确定跟踪器电路69中是否有任何空闲条目,如果没有,则在步骤255拒绝该请求。如前所述,这通常涉及使用重试管理电路70来激活重试机制。

假设在跟踪器电路中存在至少一个空闲条目,则过程进行到步骤260,在该步骤,识别与存储器访问请求相关联的QoS指示(本文中也称为QoS值)。此外,归属节点65可以被布置为例如通过在存储装置72中存储每个可能的QoS值的条目阈值来维护此类信息。因此,在步骤260,除了识别与存储器访问请求相关联的QoS值之外,还获得该QoS值的条目阈值。这识别了在任何时间点跟踪电路内可用于处理该所选QoS值的访问请求的条目的最大数量。

因此,在步骤265,确定当前正跟踪具有所识别的QoS值的存储器访问请求的条目的数量是否达到条目阈值。如果是,则在步骤255拒绝该请求,否则在步骤270接受该请求,然后将关于该存储器访问请求的信息添加到跟踪电路69内的空闲条目中。应当理解,这种方法通过将不同的QoS等级与不同类型的存储器设备相关联并且对具有不同QoS等级的存储器访问请求控制跟踪电路内所允许的占用水平来提供可用跟踪电路资源的静态划分。通过这种方法,有可能限制跟踪电路内可用于访问特定类型的存储器设备的条目数量,因此,例如,避免跟踪电路的可用资源不成比例地用于对相对慢的存储器的存储器访问,这可能抑制对可用于处理对较快存储器设备的访问的带宽的有效利用。

作为上述方法的替代或补充,当决定是接受还是拒绝新接收的存储器访问请求时,请求接受管理电路67还可以使用另一个信息源。具体地,如图6A所示,可以修改与归属节点65相关联的SAM 74,以提供指示不同从属元件的带宽能力的额外信息。具体地,SAM300可以包括多个条目305,其中每个条目提供多个字段310、315、320。字段310可用于指定可编程地址范围,并且对于字段310中的任何指定地址范围,对应字段315可提供目标标识符,该目标标识符用于指示对该地址范围的任何访问要使用的从属元件。这使得归属节点65能够在存储器访问请求需要被传播到从属元件75、85、95用于处理的情况下确定需要与这些从属元件中的哪些进行通信。应当注意,并不总是需要将存储器访问请求传播到从属元件的情况,因为可能是归属节点可以直接服务存储器访问请求的情况。例如,如前所述,各个请求器元件可以包括本地高速缓存结构,并且可以是由特定存储器访问请求所请求的数据可从这些高速缓存结构之一获得,在这种情况下,归属节点能够直接获得数据并将其返回到请求元件而不需要访问从属元件。然而,在需要访问从属元件的情况下,字段315中的信息将识别要联系哪个从属元件。

此外,字段320可以提供与由字段315中的目标标识符识别的从属元件相关联的一个或多个从属元件属性。从属元件属性可以采取多种形式,但是在一个示例性具体实施中可以提供静态带宽指示值,其本身可以基于与从属元件相关联的存储器设备的类型的知识并且因此例如可在该存储器设备内执行访问的速度来确定。根据此方法,带宽指示值在其由与从属元件相关联的存储器设备的类型指示的意义上是静态的,并且因此和与相对低速存储器设备相关联的从属元件相比,可为与相对高速存储器设备相关联的从属元件提供较高带宽指示值。

图6B示出了当基于这种静态带宽指示值信息确定是否接受存储器访问请求时可以执行的步骤。在步骤350,确定跟踪器电路69中是否有任何空闲条目,如果没有,则在步骤355拒绝该请求。然而,假设存在至少一个空闲条目,则在步骤360参考SAM 74、300以便确定目标从属元件以及该目标从属元件的静态带宽指示值。此外,获得该静态带宽指示值的条目阈值信息。以与前述QoS值基本相同的方式,请求接受管理电路可以例如通过在存储器72内维护各种不同的可能的静态带宽指示值的单独条目阈值来维护该信息,并且因此一旦已经从SAM获得所述访问请求的静态带宽指示值,则也可以检索相应的条目阈值。

然后在步骤365确定当前正跟踪目标从属设备具有该静态带宽指示值的存储器访问请求的条目的数量是否已经处于条目阈值水平。如果是,则在步骤355拒绝该请求,否则在步骤370接受该请求,并且因此在此时,跟踪器电路内的空闲条目之一被分配用于存储关于新接收的存储器访问请求的信息。以与前述QoS机制几乎相同的方式,应当理解,这种机制允许根据正在被访问的存储器设备的类型对跟踪电路的资源进行静态划分,以便寻求确保对较慢存储器设备的访问不会不成比例地利用跟踪电路的资源,并且因此寻求确保跟踪电路资源对于对较高速度存储器设备的访问保持可用。

图7示意性地示出了可以在归属节点65内使用的上述过程。当通过路径400从请求器元件接收请求时,带宽管理单元(BMU)405(其可采取前述请求接受管理电路67的形式)可用于基于可用于导出与该请求相关联的目标从属元件的带宽能力指示的某些信息来确定是接受还是拒绝该请求。如上所述,可使用从各种从属元件接收的CBUSY信号,同时另选地或另外,也可出于此目的而使用随存储器访问请求提供的QoS信息。此外,从SAM 74获得的从属元件属性(在图7中称为MC(存储器控制器)能力信息)可另选地或另外地用于提供目标从属元件的带宽能力指示。

基于带宽管理单元405的分析,确定在请求跟踪器内是否应当为当前存储器访问请求分配条目。如果是,则在跟踪器415内分配空闲条目以存储最新的存储器访问请求。如图7中示意性所示,在任何时间点,请求跟踪器电路可以跟踪以各种不同类型的存储器为目标的请求,并且当使用本文所述的技术时,可以管理跟踪电路资源,以便确保适当比例的资源可用于访问高速存储器,例如前述HBM存储器。

如果确定不应该接受新接收的请求,则调用重试管理过程420,导致通过路径425向请求器元件发出重试响应。

图8A示出了由多个请求器元件505、510、515组成的示例性系统500,这些请求器元件发出寻求经由互连器520内的归属节点525访问各种不同从属元件530、535、540的访问请求。在该示例中,假设从属元件530与DDR存储器相关联,从属元件535与HBM存储器相关联,并且从属元件540是与经由CCIX链路通信的片外存储器545相关联的CXSA从属元件。从属元件530、535、540中的每一者可维持其自身的本地队列532、537、542以跟踪当前正由这些从属元件处理的存储器访问请求。此外,在归属节点525内,跟踪电路可以包括共享队列526,该共享队列跟踪其已经接受处理的所有未决访问请求。这不仅可以包括它已经接受但还没有向从属元件发出的未决访问请求,还可以包括它已经向从属元件发出但还没有被那些从属元件完全处理的未决访问请求。

在该示例中,假设片外存储器545的访问速度最慢,从属元件530访问的DDR存储器具有中等访问速度,并且从属元件535访问的HBM存储器具有最快的访问速度。虽然图8A(并且实际上是稍后讨论的图8B)示出了由不同的请求器元件发出的对每个从属元件的访问请求,但这只是为了便于说明,并且应当注意,在一个示例性具体实施中,每个请求器元件505、510、515能够以任何存储器设备为目标,并且因此可以发出用于路由到从属元件530、535、540中的任何一者的访问请求。

图8A示出了在不采用本文中所述的技术的情况下在忙碌时间段间可能出现的潜在问题,尤其是在大量访问以相对慢的存储器设备为目标的情况下。具体地,归属节点525内的跟踪电路的共享队列526内的大部分可用空间可由以较慢存储器设备为目标的存储器访问请求占用,从而留下很少的空间来接受属于较快存储器设备的访问请求。这样,虽然可以相对充分利用与较慢存储器设备相关联的从属元件530、540,但是可以仅稍微利用从属元件535,并且该从属元件在其自己的本地队列537中具有大量的备用容量。因此,在这种情况下,用于访问HBM存储器的可用带宽没有被充分利用,结果会降低整体系统性能。

图8B示出了相同的示例性系统,但是其中归属节点525包括前述带宽管理单元527,并且因此能够主动地决定接受哪个存储器访问请求,同时考虑到这些存储器访问请求所针对的从属元件的带宽能力。因此,本文所述的技术可避免共享队列526被对较慢存储器设备的访问不成比例地占用,而可以允许更有效地利用系统的整体存储器访问资源。具体地,如图所示,从属元件530、540内的本地队列532、542可能不再被充分利用,但是通过采用本文所述的自适应划分方案,可以实现与快速存储器设备相关联的队列537的更好利用。这种方法允许在归属节点与和不同类型的存储器设备相关联的存储器控制器通信的情况下更有效地使用系统内可用的存储器带宽,从而提高整体系统性能。

从上面的描述中可以理解,本文所述的技术减轻了到较慢存储区控制器的流量压倒互连器中的共享资源的机会,从而减少了较快存储器吞吐量没有被充分利用的可能性。根据本文所述的技术,可基于目标端点的性能能力来动态地划分归属节点处的共享资源,以便提高整体系统性能和存储器效率。

通过使用本文所述的技术,则在存在具有变化的带宽能力的存储器控制器的情况下,可以使用这些技术来寻求最大化整体系统带宽。如参考图8B以举例的方式示出,带宽管理单元可以控制对归属节点处的共享跟踪器队列的访问请求的分配,使得共享跟踪器大部分被以较快存储器控制器(例如HBM控制器)为目标的事务占用,而以较慢存储器控制器为目标的事务得到的占用减少。这可以使HBM存储器控制器内的资源得到更优化的利用,继而可以提高整体系统性能。

在本申请中,字词“被配置为…”用于意指装置的元件具有能够执行所限定的操作的配置。在该上下文中,“配置”意指硬件或软件的互连的布置或方式。例如,该装置可具有提供所限定的操作的专用硬件,或者可对处理器或其他处理设备进行编程以执行该功能。“被配置为”并不意味着装置元件需要以任何方式改变以便提供所限定的操作。

虽然本文已结合附图详细描述了本发明的示例性实施方案,但应当理解,本发明并不限于那些精确的实施方案,并且在不脱离所附权利要求书所限定的本发明的范围和实质的前提下,本领域的技术人员可在其中实现各种变化、增加和修改。例如,在不脱离本发明的范围的情况下,从属权利要求的特征可与独立权利要求的特征一起进行各种组合。