多路ASI信号处理系统

文献发布时间:2023-06-19 18:34:06

技术领域

本发明涉及通信技术领域,尤其涉及一种多路ASI信号处理系统。

背景技术

现有的很多信号处理设备基于特定的芯片来实现的,使得信号处理过程灵活性差、成本高,无法实现自主可控。

例如卫星接收机,卫星接收机是一种接收卫星信号进行解扰解密后,进行线路转发的设备。卫星接收机中通常设置有用于对卫星信号进行解扰解密的模块,现有的卫星接收机结构通常需要采用CIMAX的接口芯片以及TI-DM642等特定芯片的EMIF接口机制实现,CIMAX芯片和TI-DM642芯片通过I2C接口连接,基于I2C接口进行初始化,初始化效率比较低,且只能从PCMCIA接口获取的卫星信号,加扰解密后再输出,不能选择信号输入源,灵活性差,通信效率低。卫星接收机的输出部分通常基于特定的FPGA结合对应的ASI_IP核来实现异步串行输出。此外,CIMAX的接口芯片、TI-DM642芯片、基于特定的FPGA结合对应的ASI_IP核等特定芯片导致现有的卫星接收机具有限制性,成本高、且无法实现自主可控。

卫星接收机可以输出ASI信号,现有的其他信号处理设备也可以直接处理未加密未加扰的视频生成ASI信号,但也是基于特定的FPGA结合对应的ASI_IP核来实现的,具有限制性,成本高、且无法实现自主可控,卫星接收机或者其他信号处理设备可以输出多路ASI信号。

多路ASI信号输出之后,通过对ASI的调制,生成无线电射频(RF)信号进行输出。随着现代通信技术的发展,特别是移动通信技术高速发展,新的需求层出不穷,促使新的业务不断产生,导致频率资源越来越紧张,在有限的带宽里要传输大量的多媒体数据,提高频谱利用率至关重要。由于具有高频谱利用率、高功率谱密度等优势,正交振幅调制(Quadrature Amplitude Modulation,简称QAM)被广泛应用于高速数据传输系统。现有的对于多路ASI信号的调制也是采用QAM调制技术,但是现有的是通过特定的芯片,且只能对每一路ASI信号单独调制后再合并,调制效率低,且采用特定芯片成本高,具有限制性,无法实现自主可控。

发明内容

本发明目的在于,提供一种多路ASI信号处理系统,提高了多路ASI信号的QAM的调制效率,降低了多路ASI信号的调制成本。

本发明提供一种多路ASI信号处理系统,包括QAM调制模块、存储有计算机程序的存储器和处理器,当所述处理器执行所述计算机程序,QAM调制模块包括Q个信号通道,每一信号通道配置对应的频段和QAM调制方式,当所述处理器执行所述计算机程序来运行所述QAM调制模块时,实现以下步骤:

步骤E1、获取P个ASI信号置于所述Q个信号通道中,2≤P≤Q/2,每一ASI信号占用一个信号通道,任意两个ASI信号所在的信号通道之间存在至少一个隔离信号通道;

步骤E2、对第q信号通道中的ASI信号进行数据编码、串并转换和差分处理,得到每一通道的差分处理结果,q的取值范围为1到Q;

步骤E3、根据第q信号通道对应的频段和QAM调制方式将Q个信号通道中的P个ASI信号进行傅里叶反变换,获取每一ASI信号在每一频域的映射值,得到Q维数组,每一维度的数组对应一个信号通道;

步骤E4、基于所述Q维数组计算每一存在ASI信号通道的补偿值,并通过预设的滤波器将所述Q维数组中不存ASI信号通道对应的值设置为0;

步骤E5、基于每一存在ASI信号通道的补偿值将Q维数组中对应通道的信号值进行补偿,得到补偿后的Q维数组;

步骤E6、将补偿后的Q维数组进行滤波插值和DA转换处理,生成RF信号进行输出。

本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种多路ASI信号处理系统可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有下列优点:

本发明能够基于多信号通道实现对多路ASI信号在频域内进行QAM并行调制,不依赖与特定的芯片,提高了多路ASI信号的QAM的调制效率,降低了多路ASI信号的调制成本。

上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

图1为本发明实施例提供的卫星信号处理系统架构示意图;

图2为本发明实施例提供的基于SPI的通信系统架构示意图;

图3为本发明实施例提供的卫星信号接收机架构意图;

图4为本发明实施例提供的视频信号处理系统意图;

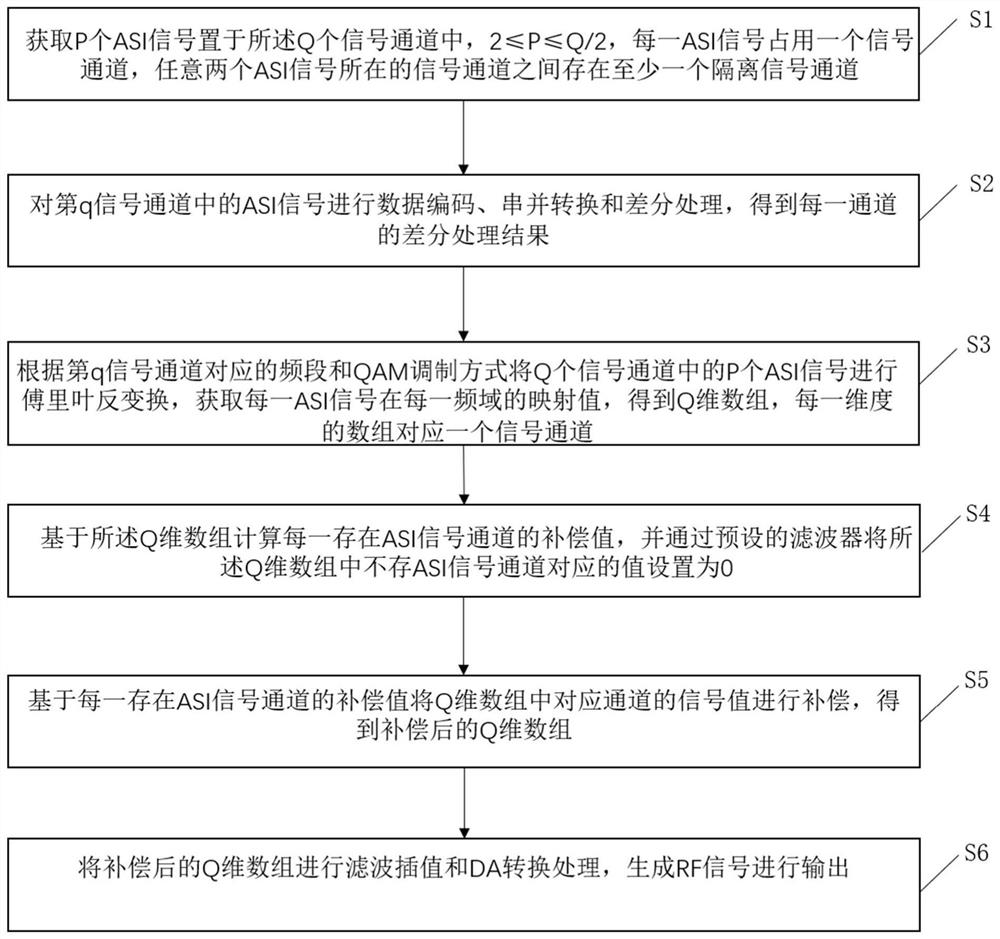

图5为本发明实施例提供的多路ASI信号处理流程图。

具体实施方式

为更进一步阐述本发明为达成预定发明目的所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本发明进行详细说明。

为了避免信号处理系统中的核心芯片受限于特定芯片,本申请提出了多种基于通用的FPGA(Field-Programmable Gate Array)和ARM处理器搭建的信号处理系统,来提高信号处理效率,降低信号处理成本,以下对本申请提出的每一信号处理系统进行详细说明。

实施例一、

实施例一提供了一种卫星信号处理系统,如图1所示,包括信号预处理模块、M个解密解扰模块{C

当所述计算机程序被所述处理器执行时,实现以下步骤:

步骤S1、通过所述信号预处理模块获取待处理的卫星信号,并进行预处理生成第一TS(Transport Stream)流,所述待处理的卫星信号为加密加扰的卫星信号。

其中,TS流指的是TS流文件,是一种DVD的文件格式。

步骤S2、所述第一ARM模块基于获取的第一路由配置信息生成第一目标路由控制命令,并将所述第一目标路由控制命令发送给所述第一FPGA模块。

需要说明的是,所述系统可以包括显示界面,通过显示界面接收用户输入的第一路由配置信息,第一路由配置信息可以根据具体应用需求灵活配置。

步骤S3、所述第一FPGA模块基于所述第一目标路由控制命令将所述第一TS流发送给至少一个第一目标C

需要说明的是,基于第一目标路由控制命令将第一TS流发送给至少一个第一目标C

步骤S4、所述第一ARM模块从所述第一TS流提取第一目标节目信息,并生成第一CI协议栈,发送给所述第一FPGA模块。

需要说明的是,第一TS流中是包括多套节目的,但系统当前需要关注的可能仅是其中的一部分,并非全部,如果全部进行解密解扰,将耗费大量系统资源,降低系统的信号处理效率,因此,本申请基于CI协议栈来提取第一目标节目信息,提高信号处理效率。

步骤S5、所述第一FPGA模块将所述第一CI协议栈转发给至少一个第二目标C

需要说明的是,基于步骤S2和步骤S3灵活配置的路由信息,使得第一TS流可以灵活发送至多个第一目标C

步骤S6、所述第二目标C

可以理解的是,第二目标C

步骤S7、所述第一FPGA模块将所述目标清流发送给所述第一ARM模块的上第一信号输出模块进行输出。

作为一种实施例,所述第一FPGA模块与第一ARM模块之间通过TSI(TS Impoart)接口以及串行外设接口(Serial Peripheral Interface,简称SPI)接口相连接,所述TSI接口用于在所述第一FPGA模块与第一ARM模块之间传输数据,所述SPI接口用于在所述第一FPGA模块与第一ARM模块之间传输命令。基于此,所述步骤S2中,所述第一ARM模块通过所述SPI接口将所述第一目标路由控制命令送给所述第一FPGA模块。所述步骤S3中,所述第一FPGA模块通过所述TSI接口将第一TS流发送给所述第一ARM模块。所述步骤S5中,所述第一FPGA模块通过所述SPI接口将所述第一CI协议栈转发给至少一个第二目标C

作为一种实施例,所述步骤S2中,所述第一ARM模块基于获取的第一路由配置信息生成第一目标路由控制命令包括:

步骤S21、所述第一ARM模块获取第一路由配置信息,所述第一路由配置信息中包括至少一个第一数据流向路径信息,所述第一数据流向路径信息包括第一数据发送模块和第一数据接收模块,所述第一数据发送模块为所述预处理模块或C

其中,第一数据流向路径信息可直接基于显示界面通过显示界面由用户输入。

步骤S22、基于所述第一数据流向路径信息生成所述第一目标路由控制命令。

作为一种实施例,所述第一TS流中包括N个节目信息、PAT(Program AssociationTable)表和N个PMT(Program Map Table)表,所述PAT表为节目关联表,所述PMT表为节目信息表,每一节目信息对应一个PMT表,所述节目信息中包括每一节目信息对应的节目ID、视频数据、音频数据,每一视频数据对应一个视频PID,每一音频数据对应一个音频PID,ID、PID均为标识信息,所述步骤S4包括:

步骤S41、获取第一目标节目信息提取指令,所述第一目标节目信息提取指令中包括第一目标节目ID。

其中,第一目标节目ID也可以直接基于显示界面通过显示界面由用户输入,也可以由系统设置。

步骤S42、基于所述第一目标节目ID,从所述PAT表中获取所有第一目标关联节目ID以及对应的第一目标PMT表ID。

步骤S43、基于第一目标PMT表ID从对应的PMT表中获取第一目标关联节目ID对应的视频PID和音频PID。

步骤S44、基于所述第一目标PMT表ID、第一目标关联节目ID以及对应的视频PID和音频PID生成所述第一CI协议栈。

需要说明的是,CI协议栈中包括目标PMT表ID数据段、目标关联节目ID数据段、视频PID数据段和音频PID数据段,将所述第一目标PMT表ID、第一目标关联节目ID以及对应的视频PID和音频PID填入CI协议栈对应的数据段,即可生成所述第一CI协议栈。

作为一种实施例,所述预处理模块包括依次连接的高频头、调谐芯片和解调芯片,所述解调芯片和所述第一FPGA模块相连接,所述步骤S1包括:

步骤S11、所述高频头获取待处理的卫星信号并发送给调谐芯片。

步骤S12、所述调谐芯片将所述待处理的卫星信号进行调谐后发送给所述解调芯片。

步骤S13、所述解调芯片将调谐后的待处理的卫星信号进行解调后生成所述第一TS流,所述第一TS流为所述第一FPGA模块能够识别的流。

需要说明的是,步骤S11-步骤S12中所涉及的调谐和解调技术直接采用现有的调谐和解调技术即可实现,在此不再赘述。

现有技术中,是通过初始化I2C总线来初始化预处理模块和解密解扰模块,但是受限于I2C总线本身的传输速度为100K到400K,传输速度较慢,导致预处理模块和解密解扰模块的初始化过程慢,解密解扰模块的初始化甚至可达到1分钟,本申请中,所述第一FPGA模块和所述第一ARM模块之间还连接有I2C总线,当所述计算机程序被所述处理器执行时,还实现以下步骤:

步骤S0、通过控制GPIO并设置对应延时的方式模拟I2C总线的行为来初始化所述预处理模块和解密解扰模块。

所述步骤S0通过GPIO并设置对应延时的方式模拟I2C总线的行为初始化预处理模块和解密解扰模块,不用占据芯片资源,提高了初始化效率,与步骤S0能够使得解密解扰模块的初始化过程仅用20S,相较于原来的1分钟有很大的提升。

作为一种实施例,Ci包括CAM卡和CA卡,CAM卡和CA卡用于配合完成第一TS流的解密解扰,所述FPGA上设置有对应的CAM卡槽,Ci的CAM卡插接在所述CAM卡槽上,所述CAM卡和CA卡之间通过ISO7816协议通信,所述CAM卡与第一FPGA模块之间通过EN50221协议通信。其中,CAM卡,它是一种数字视频条件接收模块,是一个连接电视机与外部信号源的设备,用于将压缩的数字信号转成电视内容。CAM卡和智能卡(即CA卡)配合使用,ISO7816协议和EN50221协议为现有的通信协议,在此不再赘述。

作为一种实施例,所述第一信号输出模块包括解复用模块和解码模块,所述解复用模块用于从所述清流中提取第一目标节目信息,将第一目标节目信息的视频数据和音频数据解复用;所述解码模块用于将第一目标节目信息的视频数据和音频数据分别进行解码后发送给对应的目标接收系统。所述解码模块具体可采用MPEG2解码方式进行解码,目标接收系统可以直接播放解码后的视频数据和音频数据

实施例一基于FPGA和ARM相配合的架构,灵活配置路由信息,并结合CI协议栈,从TS流中提取目标清流信息,提高了卫星信号处理效率和灵活性,降低了卫星信号的处理成本。

实施例一中,第一FPGA模块和第一ARM模块之间可以采用现有的SPI通信协议进行通信,为了进一步提高第一FPGA模块、第一ARM模块之间通信的灵活性和效率,本申请进一步提出了实施例二。

实施例二、

实施例二提供了一种基于SPI的通信系统,如图2所示,包括第一FPGA模块、第一ARM模块、安装在FPGA上的处理模块、存储有计算机程序的存储器(图2中示出)和处理器(图2中示出),所述第一FPGA模块包括FPGA寄存器。FPGA寄存器为设置在FPGA模块中的寄存器,能够用于转存命令、转存数据等。

所述第一FPGA模块与第一ARM模块之间通过TSI接口以及SPI接口相连接,所述TSI接口用于在所述第一FPGA模块与第一ARM模块之间传输数据,所述SPI接口用于在所述第一FPGA模块与第一ARM模块之间传输控制命令,所述控制命令基于所述预设的SPI数据结构生成。

所述预设的SPI数据结构包括读写标识数据段、读写目标数据段、读写类型数据段、目标地址数据段、目标信息数据段,所述读写标识数据段用于存储读或写的标识,所述读写目标数据段用于存储读写目标标识,读写目标包括FPGA寄存器或安装在FPGA上的处理模块;所述读写类型包括处理模块通用存储读写标识、处理模块属性存储读写标识、处理模块IO读写标识、空标识;所述目标地址数据段用于存储目标地址信,所述目标信息数据段用于存储目标信息。所述预设的SPI数据结构还可以设置保留数据段,用于扩展所述预设的SPI数据结构。作为一种实施例,SPI接口可以设置为CPOL=0,CPHA=0的总线标准模式,数据在SPI_CS低电平时发送,可以设置32位的SPI数据结构,第31位设置为读写标识数据段,第[30,29]位设置为读写目标数据段,第[28,27]位设置为读写类型数据段,第[26,12]位设置为目标地址数据段,[11,8]设置保留数据段,[7,0]设置为目标信息数据段。需要说明的是,预设的SPI数据结构并不限制于32位,可以根据应用需求设置其他数值。

当所述处理器执行所述计算机程序时,实现以下步骤:

步骤D1、所述第一ARM模块基于所述预设的SPI数据结构生成目标控制命令。

其中,目标控制指令基于具体处理需求设定,以实施例一为例,当需要处理路由信息时(对应于实施例一中的步骤S2),生成第一目标路由控制命令,即目标控制命令为第一目标路由控制命令。需要生成CI协议栈时(对应与实施例一中的步骤S4),目标控制命令为第一CI协议栈。

步骤D2、所述第一ARM模块将所述目标控制命令通过所述SPI接口传输给FPGA寄存器。

需要说明的是,所有的控制命令先发送给FPGA寄存器,FPGA通过读取解析FPGA寄存器中的控制命令再执行对应的操作。

步骤D3、所述第一FPGA模块从所述FPGA寄存器解析所述目标控制命令,获取读写标识、读写目标、读写类型、目标地址信息和目标信息,若读写标识为读,则执行步骤D4,若读写标识为写,则执行步骤D5。

步骤D4、所述第一FPGA模块按照读写类型从所述读写目标对应的目标地址信息中获取对应的目标读取数据,并将目标读取数据通过TSI接口返回给第一ARM模块。

步骤D5、所述第一FPGA模块按照读写类型从将所述目标信息写入读写目标对应的目标地址信息中。

作为一种实施例,所述系统包括M个安装在FPGA上的处理模块{C

作为一种实施例,当所述读写目标为FPGA寄存器时,所述目标地址数据段设置为X种地址标识中的其中一个,X=2*M+6;所述目标信息数据段设置为Y种目标信息标识中的其中一个,Y=2*M+2。所述X种地址标识为{F

以实施例一中的结构为例,所述输入模块为信号预处理模块,设置在第一FPGA模块上,用于获取待处理的卫星信号,转换为第一TS流,所述待处理的卫星信号为加密加扰的卫星信号;所述处理模块为解密解扰模块,用于从所述第一TS流中解析出目标清流,发送给所述输出模块。当需要实现实施例一中的步骤S2时,所述步骤D1具体实现为:步骤D11、所述第一ARM模块基于获取的第一路由配置信息,基于所述第一路由配置信息将预设的SPI数据结构中的读写标识数据段设置为写标识,将读写目标数据段设置为FPGA寄存器标识,读写类型数据段设置为空,目标地址数据段设置为F

所述步骤D2具体实现为:步骤D21、所述第一ARM模块将所述第一目标路由控制命令通过所述SPI接口传输给所述第一FPGA模块;

所述步骤D3具体实现为:步骤D31、所述第一FPGA模块从所述FPGA寄存器解析所述第一目标路由控制命令,确定写标识、FPGA寄存器标识、数据流发送端的标识和数据流接收端的标识,然后执行步骤D5。

所述步骤D5具体实现为:步骤D51、基于所述第一目标路由控制命令将所述第一TS流分别发送给对应的C

当需要实现实施例一中的步骤S4时,所述步骤D1具体实现为:步骤D12、所述第一ARM模块从所述第一TS流提取第一目标节目信息,并生成第一CI协议栈,将预设的SPI数据结构中的读写标识数据段设置为写标识,将读写目标数据段设置为目标C

所述步骤D2具体实现为:步骤D22、所述第一ARM模块将所述目标第一CI协议栈控制命令通过所述SPI接口传输给所述第一FPGA模块。

所述步骤D3具体实现为:步骤D32、所述第一FPGA模块从所述FPGA寄存器解析所述目标第一CI协议栈控制命令,确定写标识、目标C

所述步骤D5具体实现为:步骤D52、基于所述目标第一CI协议栈控制命令,通过目标C

作为一种实施例,若需要读取C

步骤D10、所述第一ARM模块将所述预设的SPI数据结构中的读写标识数据段设置为读标识,读写目标数据段设置为C

其中“VALUE”为“值”的意思,用于获取和传输目标信息。

步骤D20、所述第一ARM模块将所述第一读取C

步骤D30、所述第一FPGA模块从所述FPGA寄存器解析第一读取C

步骤D40、所述第一ARM模块将所述预设的SPI数据结构中的读写标识数据段设置为读标识,读写目标数据段设置为FPGA寄存器标识,将读写类型数据段设置为空,将目标地址数据段设置为B

步骤D50、所述第一ARM模块将所述第二读取C

步骤D60、所述第一FPGA模块从所述FPGA寄存器解析第二读取C

作为一种实施例,所述输入模块还可i可以设置在第一ARM模块上,用于获取待处理的视频信号转换为第二TS流,所述待处理的视频信号为未加密未加扰的信号,通过第一FPGA模块将所述第二TS流转发给所述输出模块。所述输出模块可以设置在第一FPGA模块上,用于将获取的第二TS流或目标清流进行K倍编码,K为预设的编码倍数,并添加同步字,然后进行并串转换,得到码率维持在预设码率值的ASI信号进行输出,K的值和同步字的字节数基于预设码率值和第二TS流的码率值确定。

需要说明的是,还可以设置读取FPGA属性信息、任何一个处理模块属性信息等命令,使得FPGA执行对应的操作,在此不再一一列举。

需要说明的是,实施例二所述的SPI通信系统并不仅仅适用于实施例一,其他包括FPGA模块和ARM模块架构,设置FPGA模块和ARM模块之间的SPI通信的场景同样也适用。

实施例二通过预设的SPI数据结构生成目标控制命令,发送给FPGA寄存器,第一FPGA模块通过读取解析FPGA寄存器收到的目标控制命令执行相应的读写操作,可以根据具体控制需求灵活生成对应的目标控制命令,提高了第一FPGA模块和第一ARM模块之间的通信效率。

实施例三、

实施例三提供了一种卫星信号接收机,如图3所示,包括信号预处理模块、M个解密解扰模块{C

当所述计算机程序被所述处理器执行时,实现以下步骤:

步骤F1、通过所述信号预处理模块获取待处理的卫星信号,并进行预处理生成第一TS流,所述待处理的卫星信号为加密加扰的卫星信号。

其中,TS流指的是TS流文件,是一种DVD的文件格式。

步骤F2、所述第一ARM模块基于获取的第三路由配置信息生成第三目标路由控制命令,并将所述第三目标路由控制命令发送给所述第一FPGA模块。

需要说明的是,所述系统可以包括显示界面,通过显示界面接收用户输入的第三路由配置信息,第三路由配置信息可以根据具体应用需求灵活配置。

步骤F3、所述第一FPGA模块基于所述第三目标路由控制命令将所述第一TS流发送给至少一个第一目标C

需要说明的是,基于第三目标路由控制命令将所述第一TS流发送给至少一个第一目标C

步骤F4、所述第一ARM模块从所述第一TS流提取第一目标节目信息,并生成第一CI协议栈,发送给所述第一FPGA模块。

需要说明的是,第一TS流中是包括多套节目的,但系统当前需要关注的可能仅是其中的一部分,并非全部,如果全部进行解密解扰,将耗费大量系统资源,降低系统的信号处理效率,因此,本申请基于CI协议栈来提取第一目标节目信息,提高信号处理效率。

步骤F5、所述第一FPGA模块将所述第一CI协议栈转发给至少一个第二目标C

需要说明的是,基于步骤F2和步骤F3灵活配置的路由信息,使得第一TS流可以灵活发送至多个第一目标C

步骤F6、所述第二目标C

可以理解的是,第二目标C

步骤F7、所述ASI输出模块将所述目标清流进行K倍编码,K为预设的编码倍数,并添加同步字,然后进行并串转换,得到码率维持在预设码率值的ASI信号,K的值和同步字的字节数基于预设码率值和第一TS流的码率值确定。

其中,同步字为一个字节、两个字节,也可能是多个字节的数字,用于在数据传输、处理过程中对齐数据,判断数据是否有效数据。步骤F7中无需采用特定的芯片,基于第一FPGA模块和第一ARM模块组成的架构,通过步骤F7的逻辑即可将目标清流转换为ASI信号,提高了ASI信号的生成效率。

步骤F8、将所述ASI信号通过所述ASI输出模块输出。

作为一种实施例,所述步骤F2中,所述第一ARM模块基于获取的第三路由配置信息生成第三目标路由控制命令包括:

步骤F21、所述第一ARM模块获取第三路由配置信息,所述第三路由配置信息中包括至少一个第三数据流向路径信息,所述第三数据流向路径信息包括第三数据发送模块和第三数据接收模块,所述第三数据发送模块为所述预处理模块或C

作为一种实施例,所述第一TS流中包括PAT表、N个节目信息和N个PMT表,所述PAT表为节目关联表,所述PMT表为节目信息表,每一节目信息对应一个PMT表,所述节目信息中包括每一节目信息对应的节目ID、视频数据、音频数据,每一视频数据对应一个视频PID,每一音频数据对应一个音频PID,ID、PID均为标识信息,所述步骤F4包括:

步骤F41、获取第一目标节目信息提取指令,所述第一目标节目信息提取指令中包括第一目标节目ID。

其中,第一目标节目ID也可以直接基于显示界面通过显示界面由用户输入,也可以由系统设置。

步骤F42、基于所述第一目标节目ID,从所述PAT表中获取所有第一目标关联节目ID以及对应的第一目标PMT表ID。

步骤F43、基于第一目标PMT表ID从对应的PMT表中获取第一目标关联节目ID对应的视频PID和音频PID。

步骤F44、基于所述第一目标PMT表ID、第一目标关联节目ID以及对应的视频PID和音频PID生成所述第一CI协议栈。

需要说明的是,CI协议栈中包括目标PMT表ID数据段、目标关联节目ID数据段、视频PID数据段和音频PID数据段,将所述第一目标PMT表ID、第一目标关联节目ID以及对应的视频PID和音频PID填入CI协议栈对应的数据段,即可生成所述第一CI协议栈。

第一FPGA模块和第一ARM模块之间的通信可以基于实施例二中的SPI通信系统实现,具体的,作为一种实施例,所述第一FPGA模块包括FPGA寄存器,所述第一FPGA模块与第一ARM模块之间通过TSI接口以及SPI接口相连接,所述TSI接口用于在所述第一FPGA模块与第一ARM模块之间传输数据,所述SPI接口用于在所述第一FPGA模块与第一ARM模块之间传输控制命令,所述控制命令基于所述预设的SPI数据结构生成。所述预设的SPI数据结构具体实现细节实施例二中已描述,在此不再赘述。

当所述读写目标为FPGA寄存器时,所述目标地址数据段设置为X种地址标识中的其中一个,X=2*M+6;所述目标信息数据段设置为Y种目标信息标识中的其中一个,Y=2*M+2;X种地址标识、Y种目标信息标识的具体细节已在实施例二中描述,在此不再赘述。

基于实施例二中所定义的SPI数据结构以及SPI通信方式,所述步骤F21包括:

步骤F211、所述第一ARM模块基于获取的第三路由配置信息生成第三目标路由控制命令,基于所述第三目标路由控制命令将预设的SPI数据结构中的读写标识数据段设置为写标识,将读写目标数据段设置为FPGA寄存器标识,读写类型数据段设置为空,目标地址数据段设置为F

步骤F212、所述第一ARM模块将所述第三目标路由控制命令通过所述SPI接口传输给所述第一FPGA模块。

作为一种实施例,所述步骤F3进一步包括:

步骤F31、所述第一FPGA模块从所述FPGA寄存器解析所述第三目标路由控制命令,确定写标识、FPGA寄存器标识、数据流发送端的标识和数据流接收端的标识。

步骤F32、基于所述第三目标路由控制命令将所述第一TS流分别发送给至少一个第一目标C

基于实施例二中所定义的SPI数据结构以及SPI通信方式,所述步骤F4包括:

步骤F41、所述第一ARM模块从所述第一TS流提取第一目标节目信息,并生成第一CI协议栈,将预设的SPI数据结构中的读写标识数据段设置为写标识,将读写目标数据段设置为目标C

步骤F42、所述第一ARM模块将所述目标第一CI协议栈控制命令通过所述SPI接口传输给所述第一FPGA模块。

作为一种实施例,所述步骤F5进一步包括:

步骤F51、所述第一FPGA模块从所述FPGA寄存器解析所述目标第一CI协议栈控制命令,确定写标识、目标C

步骤F52、基于所述目标第一CI协议栈控制命令,通过目标C

需要说明的是,实施例一、实施例二中的其他相关技术细节也可适用于本实施例,或者与本实施例相结合,例如实施例一种的第一输出模块也可设置在实施例三所述系统中,在此不再一一赘述。

实施例三基于FPGA和ARM相配合的架构,无需使用特定芯片,通过灵活配置路由信息,并结合CI协议栈,从TS流中提取目标清流信息,提高了卫星信号处理效率和灵活性,降低了卫星信号的处理成本,此外,基于FPGA和ARM相配合的架构,通过在FPGA中设置ASI信号的生成逻辑,无需特定芯片,即可生成ASI信号,将目标清流转换为ASI信号,提高了ASI信号的生成效率,降低了ASI信号的生成成本。

ASI信号不仅可以基于实施例三所述的系统生成,还可以基于未加密未加扰的视频信号生成,基于此,本申请进一步提出了实施例四。

实施例四、

实施例四提出了一种视频信号处理系统,如图4所示,包括第一ARM模块、第一FPGA模块、设置在所述第一ARM模块上的视频信号输入模块、设置在所述第一FPGA模块上的ASI输出模块、存储有计算机程序的存储器(图4中未示出)和处理器(图4中未示出),所述第一ARM模块和所述第一FPGA模块相连接,当所述计算机程序被所述处理器执行时,实现以下步骤:

步骤C1、通过所述视频输入模块获取待处理的视频信号,并转换为第二TS流,所述待处理的视频信号为未加密未加扰的信号。

需要说明的是,待处理的视频信号可以为能够通过网络直接获取的视频信号等,具体可以通过网页、网口获取。现有的将待处理的视频信号转换为第二TS流的方式均落入本发明保护范围之内,在此不再赘述。

步骤C2、将所述第二TS流发送给所述第一FPGA模块。

步骤C3、将所述第二TS流进行K倍编码,K为预设的编码倍数,并添加同步字,然后进行并串转换,得到码率维持在预设码率值的ASI信号,K的值和同步字的字节数基于预设码率值和第二TS流的码率值确定。

其中,同步字为一个字节、两个字节,也可能是多个字节的数字,用于在数据传输、处理过程中对齐数据,判断数据是否有效数据。步骤C3中无需采用特定的芯片,基于第一FPGA模块和第一ARM模块组成的架构,通过步骤C3的逻辑即可将第二TS流转换为ASI信号,提高了ASI信号的生成效率。

步骤C4、将所述ASI信号通过所述ASI输出模块输出。

作为一种实施例,所述第一FPGA模块与第一ARM模块之间通过TSI接口相连接,所述TSI接口用于在所述第一FPGA模块与第一ARM模块之间传输数据,所述步骤C2中,将所述第二TS流通过所述TSI接口发送给所述第一FPGA模块。

实施例四基于FPGA和ARM相配合的架构,通过在FPGA中设置ASI信号的生成逻辑,无需特定芯片,即可生成ASI信号,将第二TS流转换为ASI信号,提高了ASI信号的生成效率,降低了ASI信号的生成成本。

基于实施例三和/或实施例四所述的系统可以输出多路ASI信号,具体可以为设置多组实施例三和/或实施例四种对应的结构,或者是设置多个对应的ASI输出模块,实施例五进一步提出了一种对多路ASI信号的处理技术。

实施例五、

实施例五提供了一种多路ASI信号处理系统,包括QAM调制模块、存储有计算机程序的存储器和处理器,当所述处理器执行所述计算机程序,QAM调制模块包括Q个信号通道,每一信号通道配置对应的频段和QAM调制方式。

当所述处理器执行所述计算机程序来运行所述QAM调制模块时,如图5所示,实现以下步骤:

步骤E1、获取P个ASI信号置于所述Q个信号通道中,2≤P≤Q/2,每一ASI信号占用一个信号通道,任意两个ASI信号所在的信号通道之间存在至少一个隔离信号通道。

其中,P个ASI信号可以基于多个实施例三和/或实施例四中的系统输出。每一信号通道配置的频段在45M至960M的范围内,每一信号通道配置QAM调制方式为16QAM、32QAM、128QAM或256QAM等,可以覆盖45M-960M全频段,从而实现在全频段、任意带宽的任意调制,相比于现有的单一频段调制的方式更加灵活。具体可以采用通道隔离技术实现任意两个ASI信号所在的信号通道之间存在至少一个隔离信号通道,在此不再赘述。

步骤E2、对第q信号通道中的ASI信号进行数据编码、串并转换和差分处理,得到每一通道的差分处理结果,q的取值范围为1到Q。

其中,步骤E2中是对每一第q信号通道中的ASI信号独立并行进行数据编码、串并转换和差分处理,得到每一通道的差分处理结果。

步骤E3、根据第q信号通道对应的频段和QAM调制方式将Q个信号通道中的P个ASI信号进行傅里叶反变换,获取每一ASI信号在每一频域的映射值,得到Q维数组,每一维度的数组对应一个信号通道。

需要说明的是,步骤E3具体可以通过星座映射的方式实现,现有技术中的星座映射是在时域内实现的,而步骤E3中是在频域内实现,此外,现有技术中只能对单个通道的ASI信号进行星座映射,后续再为每一通道设置滤波器进行成形滤波,进而再通过设置乘法器进行合并,处理效率低,消耗资源多。而本申请通过设置Q个信号通道,每一信号通道配置对应的频段和QAM调制方式,在步骤E3中,在频域内对Q个信号通道统一进行处理,得到Q维数组。

步骤E4、基于所述Q维数组计算每一存在ASI信号通道的补偿值,并通过预设的滤波器将所述Q维数组中不存ASI信号通道对应的值设置为0。

需要说明的是,现有技术中所有相关计算补偿值的算法全部落入本发明保护范围之内,在此不再赘述。此外,理论上,Q个信号通道中没有设置ASI信号的通道对应的数组内的值应该为0,但是由于处理过程中其他通道的参与干扰,会对这些本应设置为0的通道产生附加值,使得这些值可能不为0,因此需要通过预设的滤波器将所述Q维数组中不存ASI信号通道对应的值设置为0,现有技术中,需要设置多个滤波器才能实现,而本申请只需要设置一个滤波器,对Q维数组进行滤波即可,快速且准确。

步骤E5、基于每一存在ASI信号通道的补偿值将Q维数组中对应通道的信号值进行补偿,得到补偿后的Q维数组。

需要说明的是,现有的所有基于补偿值进行补偿的处理方式全部落入本发明保护范围之内,在此不再赘述。

步骤E6、将补偿后的Q维数组进行滤波插值和DA转换处理,生成RF信号进行输出。

需要说明的是,DA转换指的是将数字信号转换为模拟信号,现有的所有滤波插值和DA转换处理的处理方式全部落入本发明保护范围之内,在此不再赘述。通过滤波插值能够使得DA输出更加平滑。

作为一种实施例,所述步骤E2中,采用RS编码的方式对第q信号通道中的ASI信号进行数据编码。RS编码是一种前向纠错的信道编码,对由校正过采样数据所产生的多项式有效。

作为一种实施例,所述系统还包括第二FPGA模块和第二ARM模块,所述第二FPGA模块上设置有T个ASI输入通道,可以与基于实施例三和/或实施例四所述的系统输出的多路ASI信号对接,T≥P,所述QAM调制模块设置在所述第二FPGA模块上,所述T个ASI输入通道用于获取P个ASI信号;所述第二FPGA模块和第二ARM模块之间通过TSI接口以及SPI接口相连接,所述TSI接口用于在所述第二FPGA模块与第二ARM模块之间传输数据,所述SPI接口用于在所述第二FPGA模块与第二ARM模块之间传输命令。

多个ASI信号中是可能存在冲突信息的,即不同的ASI信号中存在一些相同标识的信息,因此需要更新调整,避免信息冲突,作为一种实施例,所述步骤E1包括:

步骤E11、所述第二ARM模块基于获取的第四路由配置信息生成第四目标路由控制命令,并将所述第四目标路由控制命令发送给所述第二FPGA模块。

步骤E12、所述第二FPGA模块基于所述第四目标路由控制命令将T个ASI输入通道中的U个ASI信号发送给所述第二ARM模块,P≤U≤T。

步骤E13、所述第二ARM模块解析并更新U个ASI信号中的节目描述信息,并回传给第一FPGA模块,FPGA更新对应的U个ASI信号中的节目描述信息。

步骤E14、所述第二ARM模块从更新后的U个ASI信号中提取第二目标节目信息,生成第三CI协议栈,发送给所述第一FPGA模块。

步骤E15、所述第二FPGA模块基于所述第三CI协议栈从U个ASI信号中提取P个ASI信号置于预设的Q个信号通道中。

作为一种实施例,每一所述ASI信号中包括F(x)个节目信息、PAT表和F(x)个PMT表,所述PAT表为节目关联表,F(x)为节目信息数量,不同的ASI信号对应的F(x)值可能不同,所述PMT表为节目信息表,每一节目信息对应一个PMT表,所述节目信息中包括每一节目信息对应的节目ID、视频数据、音频数据,每一视频数据对应一个视频PID,每一音频数据对应一个音频PID,ID、PID均为标识信息,所述节目描述信息包括节目ID、PMT表和PAT表。所述步骤E11中,所述第二ARM模块基于获取的第四路由配置信息生成第四目标路由控制命令包括:

步骤E111、所述第二ARM模块获取第四路由配置信息,所述第四路由配置信息中包括至少一个第四数据流向路径信息,所述第四数据流向路径信息包括第二数据发送模块和第二数据接收模块,所述第二数据发送模块至少两个ASI输入通道,所述第二数据接收模块为第二ARM模块。

步骤E112、基于所述第四数据流向路径信息生成所述目标路由控制命令。

结合实施例二中所述的预设的SPI数据结构,本实施例中,对应的预设的SPI数据结构具体可包括读写标识数据段、读写目标数据段、读写类型数据段、目标地址数据段、目标信息数据段,所述读写标识数据段用于存储读或写的标识,所述读写目标数据段用于存储读写目标标识,读写目标包括FPGA寄存器或ASI输入通道;所述读写类型包括ASI输入通道通用存储读写标识、ASI输入通道属性存储读写标识、ASI输入通道IO读写标识、空标识;所述目标地址数据段用于存储目标地址信,所述目标信息数据段用于存储目标信息。

在进行SPI通信的过程中,本实施例中,第二FPGA模块对应于实施例二中的第一FPGA模块,第二ARM模块对应于实施例二中的第一ARM模块,T个ASI输入通道{ASI

在本实施例中,基于实施例二中的预设的SPI数据结构,当所述读写目标为FPGA寄存器时,所述目标地址数据段设置为K种地址标识中的其中一个,K=2*T+6;所述目标信息数据段设置为L种目标信息标识中的其中一个,L=2*T+1。所述K种地址标识为{FS

基于上述结构,所述步骤E112包括:

步骤E1121、基于所述第四数据流向路径信息将预设的SPI数据结构中的读写标识数据段设置为写标识,将读写目标数据段设置为FPGA寄存器标识,读写类型数据段设置为空,目标地址数据段设置为HS

步骤E131、所述第二ARM模块解析U个ASI信号中每一ASI信号对应的节目信息、PAT表和PMT表,属于不同ASI信号但具有相同节目ID、视频PID、音频PID、PAT表ID和/或PMT表ID进行更新,使得不同ASI信号的节目ID、视频PID、音频PID、PAT表ID、PMT表ID均不相同。需要说明的是,更新过程进更新了标识信息,即ID或PID,避免冲突,但原始的视频数据和音频数据保持不变。

作为一种实施例,步骤E14包括:

步骤E141、获取第二目标节目信息提取指令,所述第二目标节目信息提取指令中包括第二目标节目ID。

步骤E142、基于所述第二目标节目ID,从所述PAT表中获取所有第二目标关联节目ID以及对应的第二目标PMT表ID。

步骤E143、基于第二目标PMT表ID从对应的PMT表中获取第二目标关联节目ID对应的视频PID和音频PID。

步骤E144、基于所述第二目标PMT表ID、第二目标关联节目ID以及对应的视频PID和音频PID生成所述第三CI协议栈。

所述步骤E14还包括:

步骤E145、将预设的SPI数据结构中的读写标识数据段设置为写标识,将读写目标数据段设置为目标ASI

所述步骤E15包括:

步骤E151、所述第二FPGA模块从所述FPGA寄存器解析目标第三CI协议栈控制命令,确定写标识、目标ASI

步骤E152、基于所述目标第三CI协议栈控制命令,通过目标ASI

步骤E153、目标ASI

需要说明的是,实施例一、实施例二、实施例三、实施例四中的相关技术细节同样可可以应用于本实施例中,不再赘述。

实施例五能够基于多信号通道实现对多路ASI信号在频域内进行QAM并行调制,不依赖与特定的芯片,提高了多路ASI信号的QAM的调制效率,降低了多路ASI信号的调制成本。

实施例六、

基于实施例三所述系统向所述T个ASI输入通道输入ASI信号,采用实施例五中的系统对多路ASI信号进行处理,具体实施细节在实施例三和实施例五中已描述,在此不再赘述。

实施例七、

基于实施例四所述系统向所述T个ASI输入通道输入ASI信号,采用实施例五中的系统对多路ASI信号进行处理,具体实施细节在实施例四和实施例五中已描述,在此不再赘述。

需要说明的是,一些示例性实施例被描述成作为流程图描绘的处理或方法。虽然流程图将各步骤描述成顺序的处理,但是其中的许多步骤可以被并行地、并发地或者同时实施。此外,各步骤的顺序可以被重新安排。当其操作完成时处理可以被终止,但是还可以具有未包括在附图中的附加步骤。处理可以对应于方法、函数、规程、子例程、子程序等等。

以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。