半导体装置与其制造方法

文献发布时间:2023-06-19 19:37:02

技术领域

本发明的一些实施方式是关于半导体装置与其制造方法。

背景技术

随机存取存储器(random access memory,RAM)为挥发性存储器,通常可分为静态随机存取存储器(static random access memory,SRAM)与动态随机存取存储器(dynamicrandom access memory,DRAM)。静态随机存取存储器借由存储器中的晶体管的导通状态来存储信息,而动态随机存取存储器的数字信号借由存储器单元中的电容的充电量状态来决定。在随机存取存储器中,信息存取是由连接栅极与位元线的字元线来控制,而栅极与位元线连接至源极/漏极。

发明内容

本发明的一些实施方式提供一种半导体装置,包含基板、位元线、位元线触点、字元线与焊垫。位元线在基板上。位元线触点接触位元线的底部并在基板中,其中位元线触点包含第一部分与在第一部分下的第二部分,在横截面视角中,第一部分比第二部分宽。字元线相邻位元线触点。焊垫在基板上,其中焊垫相邻字元线,使得字元线位于位元线触点与焊垫之间。

在一些实施方式中,位元线触点的第一部分的横截面轮廓与位元线触点的第二部分的横截面轮廓不连续。

在一些实施方式中,位元线触点的第一部分具有侧壁,位元线触点的第一部分的侧壁的顶部连接至位元线,位元线触点的第一部分的侧壁的底部连接至位元线触点的第二部分,且位元线触点的第一部分的侧壁的顶部比位元线触点的第一部分的侧壁的底部还直。

在一些实施方式中,位元线触点的第二部分具有侧壁,位元线触点的第二部分的侧壁连接至位元线触点的第一部分的侧壁的底部,且位元线触点的第二部分的侧壁比位元线触点的第一部分的侧壁的底部还直。

在一些实施方式中,位元线触点的第一部分的侧壁实质对齐位元线的侧壁。

在一些实施方式中,位元线触点包含硅与掺杂剂,掺杂剂的原子半径小于硅。

在一些实施方式中,半导体装置还包含介电结构,在基板中且相邻焊垫。

在一些实施方式中,半导体装置还包含电容,连接至焊垫。

在一些实施方式中,位元线触点的第一部分的宽度在470埃至530埃之间,且位元线触点的第二部分的宽度在380埃至420埃之间。

在一些实施方式中,位元线触点的第一部分的深度在160埃至200埃之间,且位元线触点的第二部分的深度在400埃至440埃之间。

本发明的一些实施方式提供一种制造半导体装置的方法,包含形成第一光阻层于基板上,其中第一光阻层具有暴露基板的一部分的开口。借由植入第一掺杂剂至基板中并使用第一光阻层为遮罩,形成植入区域于基板的部分中。移除基板上的第一光阻层。形成第二光阻层于基板上,其中第二光阻层部分覆盖植入区域。执行第一蚀刻工艺以移除植入区域,使得凹槽形成在基板中。执行第二蚀刻工艺以移除基板的一部分以形成沟槽于基板中,其中沟槽比基板中的凹槽还窄。沉积半导体材料于凹槽与沟槽中,以形成位元线触点于基板中。

在一些实施方式中,方法还包含在沉积半导体材料于凹槽与沟槽中后,掺杂第二掺杂剂至半导体材料中。

在一些实施方式中,第二掺杂剂原子半径小于半导体材料。

在一些实施方式中,第一掺杂剂为n型掺杂剂。

在一些实施方式中,方法还包含在沉积半导体材料于凹槽与沟槽中后,平坦化凹槽中的半导体材料。

在一些实施方式中,方法还包含在形成植入区域于基板的部分中时,调整植入剂量以控制凹槽的深度。

在一些实施方式中,方法还包含在形成植入区域于基板的部分中时,调整植入能量以控制凹槽的深度。

在一些实施方式中,执行该第一蚀刻工艺使得第二光阻层的一部分悬浮在基板的凹槽上。

位元线触点的形状可增加位元线触点中的拉伸应变。更详细而言,位元线触点被小于半导体材料的原子半径的掺杂剂掺杂,且增加掺杂剂可导致n型金属氧化物半导体中的拉伸应变。位元线触点的较宽的上部可提升由拉伸应变所造成的效应。因此,n型金属氧化物半导体中的拉伸应变可提升n型金属氧化物半导体的电子迁移率与电流。

附图说明

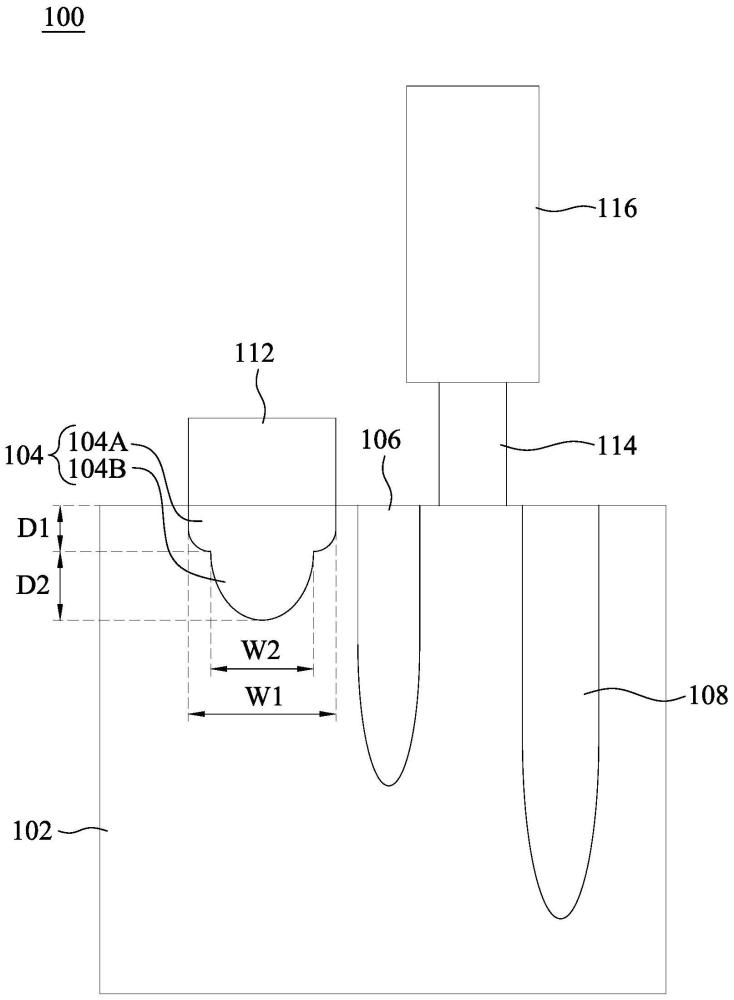

图1绘示根据本发明的一些实施方式的半导体装置的横截面视图。

图2A至图2B绘示根据本发明的一些实施方式的形成半导体装置的工艺的流程图。

图3至图11绘示形成包含位元线触点的半导体装置的工艺的中间阶段的横截面视图。

具体实施方式

以下将以图式公开本发明的复数个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本发明。也就是说,在本发明部分实施方式中,这些实务上的细节是非必要的。此外,为简化图式起见,一些现有惯用的结构与元件在图式中将以简单示意的方式绘示。

本发明的一些实施方式是关于连接至存储器装置的位元线的位元线触点的形状。位元线触点具有较宽的第一部分与较窄的第二部分,第二部分在第一部分下。当具有此种形状时,位元线触点可在n型金属氧化物半导体(n-type metal–oxide–semiconductor,NMOS)中提供拉伸应变。因此,从n型金属氧化物半导体的位元线的电子迁移率是增加的,从而增加从n型金属氧化物半导体的位元线的电流。

图1绘示根据本发明的一些实施方式的半导体装置100的横截面视图。半导体装置100为简化的存储器装置,例如动态随机存取存储器(DRAM)的示意图。在一些实施方式中,半导体装置100包含n型金属氧化物半导体。特别而言,半导体装置100包含基板102、位元线触点104、位元线112与焊垫114。位元线112在基板102上。位元线触点104接触位元线112的底部并在基板102中。位元线触点104包含第一部分104A与在第一部分104A下的第二部分104B,且在横截面视角中,第一部分104A比第二部分104B宽。字元线106相邻位元线触点104。焊垫114在基板102上,且焊垫114相邻字元线106,使得字元线106在位元线触点104与焊垫114之间。

位元线触点104的形状经设计以提升半导体装置100的效能。位元线触点104的第一部分104A的横截面轮廓与位元线触点104的第二部分104B的横截面轮廓不连续。更详细地说明,位元线触点104的第一部分104A具有侧壁。位元线触点104的第一部分104A的侧壁的顶部连接至位元线112且实质对齐位元线112的侧壁,且位元线触点104的第一部分104A的侧壁的底部连接至位元线触点104的第二部分104B。位元线触点104的第一部分104A的侧壁的顶部比位元线触点104的第一部分104A的侧壁的底部还直。举例而言,第一部分104A的侧壁的顶部为实质直线状,而第一部分104A的侧壁的底部为弯曲的(例如凸出的)。位元线触点104的第二部分104B具有侧壁,位元线触点104的第二部分104B的侧壁连接至位元线触点104的第一部分104A的侧壁的底部,且位元线触点104的第二部分104B的侧壁比位元线触点104的第一部分104A的侧壁的底部还直。举例而言,第二部分104B的侧壁为实质直线状。换句话说,位元线112直接覆盖位元线触点104,且位元线触点104的第二部分104B的侧壁从位元线触点104的第一部分104A的侧壁往内缩。

在一些实施方式中,位元线触点104包含硅与掺杂剂,且此掺杂剂的原子半径小于硅。在此提到的“原子半径”指的是原子的尺寸且通常指的是从原子核的中心至原子中的电子的环绕壳层边界之间的平均距离。换句话说,掺杂剂的尺寸比硅小。在一些实施方式中,掺杂剂包含碳、磷、其组合或类似者。包含具有较小原子半径的掺杂剂的位元线触点104在n型金属氧化物半导体中提供位元线触点104中的拉伸应变。位元线触点104的第一部分104A形成的尺寸比位元线触点104的第二部分104B还大。因此,在硅中的掺杂剂所造成的效果更加显著,即当具有本发明所揭示的形状时,位元线触点104承受更多应变。拉伸应变可增加位元线112的电子迁移率并因此提升从位元线112流经位元线触点104至焊垫114的电流。此外,较宽的第一部分104A可减少位元线触点104的电阻。

位元线触点104具有在本发明的范围中任何适合的尺寸。在一些实施方式中,位元线触点104的第一部分104A的宽度W1在470埃至530埃之间,且位元线触点104的第二部分104B宽度W2在380埃至420埃之间。位元线触点104的第一部分104A的深度D1在160埃至200埃之间,且位元线触点104的第二部分104B深度D2在400埃至440埃之间。若位元线触点104的尺寸小于所公开的范围,位元线触点104可能太小使得在硅中的掺杂剂所造成的效果不显著。若位元线触点104的尺寸大于所公开的范围,位元线触点104可能不必要地太大且超过位元线112所覆盖的范围。

字元线106在基板102中且在位元线触点104与焊垫114之间。在一些实施方式中,字元线106在横截面视图上不接触位元线触点104与焊垫114,如图1所示。在一些实施方式中,另一个字元线106在位元线触点104的相对侧,使得位元线触点104在两个字元线106之间。字元线106的底部可低于位元线触点104的第二部分104B。因此,从位元线112流出的电流流经在字元线106下的基板102并流至焊垫114。

在一些实施方式中,半导体装置100还包含在基板102中并相邻焊垫114的介电结构108。介电结构108可电性隔绝不同字元线且可往下延伸至低于字元线106的底部。此外,介电结构108与字元线106在焊垫114的相对侧,也就是说,焊垫114在介电结构108与字元线106之间。在一些实施方式中,半导体装置100还包含连接至焊垫114的电容116。如此一来,从位元线112流出的电流可流经位元线触点104、基板102与焊垫114并流至电容116。

图2A至图2B绘示根据本发明的一些实施方式的形成半导体装置的工艺10的流程图。图3至图11绘示形成包含位元线触点(可以是图1中的位元线触点104)的半导体装置的工艺的中间阶段的横截面视图。参考图2A中的操作11,可在基板(例如图1中的基板102)中形成介电结构(例如图1中的介电结构108)。参考图2A中的操作12,字元线(例如图1中的字元线106)可接着形成在基板中并相邻介电结构。接着,参考图2A中的操作13与图3,在基板202上形成第一光阻层204。第一光阻层204具有暴露基板202的一部分的开口O1。基板202类似或相同于图1中的基板102。基板202可包含任何合适的材料。在一些实施方式中,基板202为硅基板。或者,基板202可包含其他元素半导体,例如锗;化合物半导体,包含碳化硅、砷化镓、磷化镓、磷化铟、砷化铟与/或锑化铟;合金半导体,包含SiGe、GaAsP、AlInAs、AlGaAs、GaInAs、GaInP与或GaInAsP;或其组合。

在一些实施方式中,借由光刻工艺来形成第一光阻层204。更具体而言,先在基板202上共形地形成光阻材料。在一些实施方式中,光阻材料可借由例如旋转涂布而形成。接着将光阻材料曝光在图案化光源下,并显影经图案化的光阻材料以形成其中具有开口O1的第一光阻层204,其中开口O1的图案与图案化光源相同。第一光阻层204中的开口O1具有宽度,在一些实施方式中,宽度在470埃至530埃之间。在基板202上形成第一光阻层204之后,植入掺杂物至基板202以形成基板202中的主动区,且位元线触点(例如图10中的位元线触点214)将后续形成于主动区中。

参考图2A中的操作14与图4,借由植入第一掺杂剂至基板202中并使用第一光阻层204为遮罩,在基板202的一部分中形成植入区域206。更具体而言,执行第一植入工艺IMP1以植入第一掺杂剂至基板202中。植入区域206形成在由第一光阻层204的开口O1暴露的基板202的部分。植入第一掺杂剂至基板202以形成植入区域206可造成植入区域206与基板202之间的蚀刻选择性。在一些实施方式中,第一掺杂剂为n型掺杂剂,例如砷、磷、其组合或类似者。其他可形成与基板202之间的相异蚀刻选择性的掺杂剂也包含在本发明的范围内。

在一些实施方式中,在基板202的一部分中形成植入区域206时,调整植入剂量与/或植入能量以控制植入区域206与后续形成的凹槽(例如图7中的凹槽)的深度D3。举例而言,在高植入剂量与/或强植入能量下执行第一植入工艺IMP1可形成深的深度D3。另一方面,在低植入剂量与弱植入能量下执行第一植入工艺可形成浅的深度D3。在一些实施方式中,植入剂量在约1x10

参考图2A中的操作15与图5,移除在基板202上的第一光阻层204。借由任何适合的方式来移除第一光阻层204,例如脱除、灰化或类似者。

参考图2A中的操作16与图6,在基板202上形成第二光阻层208。第二光阻层208部分地覆盖植入区域206。更具体而言,第二光阻层208具有在其中的开口O2。开口O2比第一光阻层204中的开口O1(图2)还窄。因此,第二光阻层208覆盖植入区域206的周边部分并暴露植入区域206的中间部分。在一些实施方式中,第二光阻层208中的开口O2的宽度在380埃至420埃之间。形成第二光阻层208的工艺类似或相同于形成第一光阻层204的工艺。在一些实施方式中,第二光阻层208的组成与材料也类似或相同于第一光阻层204的组成与材料。

参考图2A中的操作17与图7,执行第一蚀刻工艺以移除植入区域206,使得凹槽R形成在基板202中。更具体而言,因为植入区域206与基板202具有不同的蚀刻选择性,第一蚀刻工艺可移除植入区域206而不移除基板202的剩余部分。第一蚀刻工艺可为使用任何适合的蚀刻剂的干式蚀刻。在一些实施方式中,蚀刻剂可以是氯气与氦气的组合。此外,选择适合的蚀刻历时以全面地移除植入区域206。举例而言,蚀刻历时在约100秒至约150秒之间。在第一蚀刻工艺之后,第二光阻层208的一部分悬浮在基板202的凹槽R上,且凹槽R具有与植入区域206的宽度W3与深度D3相同的宽度W3与深度D3。

参考图2A中的操作18与图8,执行第二蚀刻工艺以移除基板202的一部分以形成沟槽T于基板202中,且沟槽T比基板202中的凹槽R还窄。更详细地说明,垂直地蚀刻由第二光阻层208的开口O2所暴露的基板202。因为沟槽T是借由使用第二光阻层208为遮罩而形成,沟槽T的宽度W4与第二光阻层208中的开口O2的宽度相同。沟槽T在凹槽R中且从凹槽R往下延伸。在一些实施方式中,沟槽T具有深度D4,且沟槽T的深度D4在400埃至440埃之间。第二蚀刻工艺可为使用任何适合的蚀刻剂的干式蚀刻。在一些实施方式中,蚀刻剂为溴化氢气体。

参考图2B中的操作19与图9,在基板202中形成沟槽T之后,移除第二光阻层208。借由任何适合的方式来移除第二光阻层208,例如脱除、灰化或类似者。接着,参考图2B中的操作20与图10,在凹槽R与沟槽T中沉积半导体材料212。半导体材料212可为任何适合的半导体材料。在一些实施方式中,半导体材料可为硅。可使用任何适合的方法来沉积半导体材料212。在一些实施方式中,可借由化学气相沉积(chemical vapor deposition,CVD)、物理气相沉积(physical vapor deposition,PVD)、原子层沉积(atomic layer deposition,ALD)或类似者来形成半导体材料212。

参考图2B中的操作21与图10,在沉积半导体材料212至凹槽R与沟槽T中之后,在第二植入工艺IMP2中掺杂第二掺杂剂至半导体材料212中。第二掺杂剂的原子半径小于半导体材料212。在一些实施方式中,第二掺杂剂包含碳、磷、其组合或类似者。参考图2B中的操作22与图11,在第二植入工艺IMP2之后,借由例如化学机械研磨来平坦化在凹槽R中的半导体材料212。如此一来,位元线触点214形成在基板202中。

位元线触点214包含凹槽R中的第一部分214A与沟槽T中的第二部分214B。第一部分214A与第二部分214B可分别对应至图1中的位元线触点104的第一部分104A与第二部分104B。具有较小的原子半径的掺杂剂提供在位元线触点214中的拉伸应变。拉伸应变可增加从位元线112的电子迁移率并因此增加从图1的位元线112流出的电流,且位元线触点214的较宽的第一部分214A提升由拉伸应变所造成的效应。此外,较宽的第一部分214A也可减少位元线触点214的电阻。

在形成位元线触点214之后,参考图2B中的操作23至25,在位元线触点214上形成位元线(例如图1中的位元线112),在字元线(例如图1中的字元线106)旁形成焊垫(例如图1中的焊垫114),并在焊垫上形成电容(例如图1中的电容116)。应注意,虽然图2A至图2B与图3至图11绘示形成半导体装置的不同组件的顺序,形成不同组件的顺序为可调换的。举例而言,字元线106与介电结构108可在形成位元线触点214之后形成。

本发明的一些实施方式的位元线触点提供一些优势。位元线触点的形状可提升位元线触点中的拉伸应变。更详细而言,位元线触点被小于半导体材料的原子半径的掺杂剂掺杂,且增加掺杂剂可导致n型金属氧化物半导体中的拉伸应变。位元线触点的较宽的上部可提升由拉伸应变所造成的效应。因此,n型金属氧化物半导体中的拉伸应变可提升n型金属氧化物半导体的电子迁移率与电流。

虽然本发明已以实施方式公开如上,然其并非用以限定本发明,本领域技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视权利要求书所界定者为准。

【符号说明】

10:工艺

11:操作

12:操作

13:操作

14:操作

15:操作

16:操作

17:操作

18:操作

19:操作

20:操作

21:操作

22:操作

23:操作

24:操作

25:操作

100:半导体装置

102:基板

104:位元线触点

104A:第一部分

104B:第二部分

106:字元线

108:介电结构

112:位元线

114:焊垫

116:电容

202:基板

204:第一光阻层

206:植入区域

208:第二光阻层

212:半导体材料

214:位元线触点

214A:第一部分

214B:第二部分

D1:深度

D2:深度

D3:深度

D4:深度

IMP1:第一植入工艺

IMP2:第二植入工艺

O1:开口

O2:开口

R:凹槽

T:沟槽

W1:宽度

W2:宽度

W3:宽度

W4:宽度。