一种适用于电能表的抗浪涌高压钳位保护电路

文献发布时间:2023-06-19 19:33:46

技术领域

本发明涉及电路保护技术领域,尤其涉及一种适用于电能表的抗浪涌高压钳位保护电路。

背景技术

高压钳位保护电路常用于中小功率工业仪表高压电源供电解决方案,一般用在开关电源电路的高压电解电容、高频变压器、开关电源控制芯片前端,起到输入过压钳位保护作用。现有的高压钳位保护电路通常是采用高压MOS管、TVS管、稳压二极管等元器件组合而成的保护电路,元件多、体积大,占用较多的电路板空间,并且当输入电压在钳位阈值电压以下时,高压MOS管也会存在一定的损耗,自身会发热,可靠性较差。

发明内容

基于现有技术的上述情况,本发明的目的在于提供一种适用于电能表的抗浪涌高压钳位保护电路,解决了在不带电情况下,采用专用高压钳位保护芯片设计的保护电路无法满足产品要求的雷击浪涌试验的问题,弥补现有技术的不足,有效提高电路可靠性。

为达到上述目的,根据本发明的一个方面,提供了一种适用于电能表的抗浪涌高压钳位保护电路,所述高压钳位保护电路用于电能表的输入过压钳位保护,包括第一电阻网络、第二电阻网络和高压钳位保护芯片;

所述第一电阻网络连接于该保护电路的输入电压正极和输出电压正极之间;

所述第二电阻网络连接于该保护电路的输入电压负极和输出电压负极之间;

所述第一电阻网络、第二电阻网络和高压钳位保护芯片依次相互连接;

所述高压钳位保护芯片包括内置MOS管,在所述内置MOS管的源极和漏极之间设置浪涌保护单元。

进一步的,所述浪涌保护单元包括半导体放电管或压敏电阻。

进一步的,所述半导体放电管的转折电压大于电路正常工作范围上限时高压钳位保护芯片内置MOS管漏源极间的电压值;并且小于高压钳位保护芯片内置MOS管漏源极间耐压值;

所述半导体放电管的重复峰值脉冲电流大于所述电能表在浪涌测试条件下的最大电流。

进一步的,所述压敏电阻的最大连续直流工作电压大于电路正常工作范围上限时高压钳位保护芯片内置MOS管漏源极间的电压值;

所述压敏电阻的压敏电压小于高压钳位保护芯片内置MOS管漏源极间耐压值;

所述压敏电阻的通流容量大于电能表在浪涌测试条件下的最大电流。

进一步的,所述第一电阻网络包括线绕电阻和第一串联电阻串;

所述线绕电阻的两端分别连接输入电压正极和输出电压正极。

进一步的,所述第一串联电阻串包括多个串联连接的电阻,所述第一串联电阻串的一端连接输出电压正极,另一端连接第二电阻网络。

进一步的,所述第二电阻网络包括第二串联电阻串、稳压保护单元和浪涌保护单元。

进一步的,所述第二串联电阻串包括多个串联连接的电阻,所述第二串联电阻串的一端连接第一串联电阻串,另一端连接输出电压负极。

进一步的,所述稳压保护单元的一端连接第一电阻网络,另一端连接输入电压负极。

进一步的,所述稳压保护单元包括稳压电阻、稳压管和电容;

所述稳压管的阳极连接于所述输入电压负极和高压钳位保护芯片的接地端,阴极通过所述稳压电阻连接至第一串联电阻串和第二串联电阻串的连接点。

综上所述,本发明提供了一种适用于电能表的抗浪涌高压钳位保护电路,该高压钳位保护电路用于电能表的输入过压钳位保护,包括第一电阻网络、第二电阻网络和高压钳位保护芯片;所述第一电阻网络连接于该保护电路的输入电压正极和输出电压正极之间;所述第二电阻网络连接于该保护电路的输入电压负极和输出电压负极之间;所述第一电阻网络、第二电阻网络和高压钳位保护芯片依次相互连接;所述高压钳位保护芯片包括内置MOS管,在所述内置MOS管的源极和漏极之间设置浪涌保护单元。通过在电路中设置浪涌保护单元,解决了在不带电情况下,采用专用高压钳位保护芯片设计的保护电路无法满足产品要求的雷击浪涌试验的问题,弥补现有技术的不足,有效提高电路可靠性。

附图说明

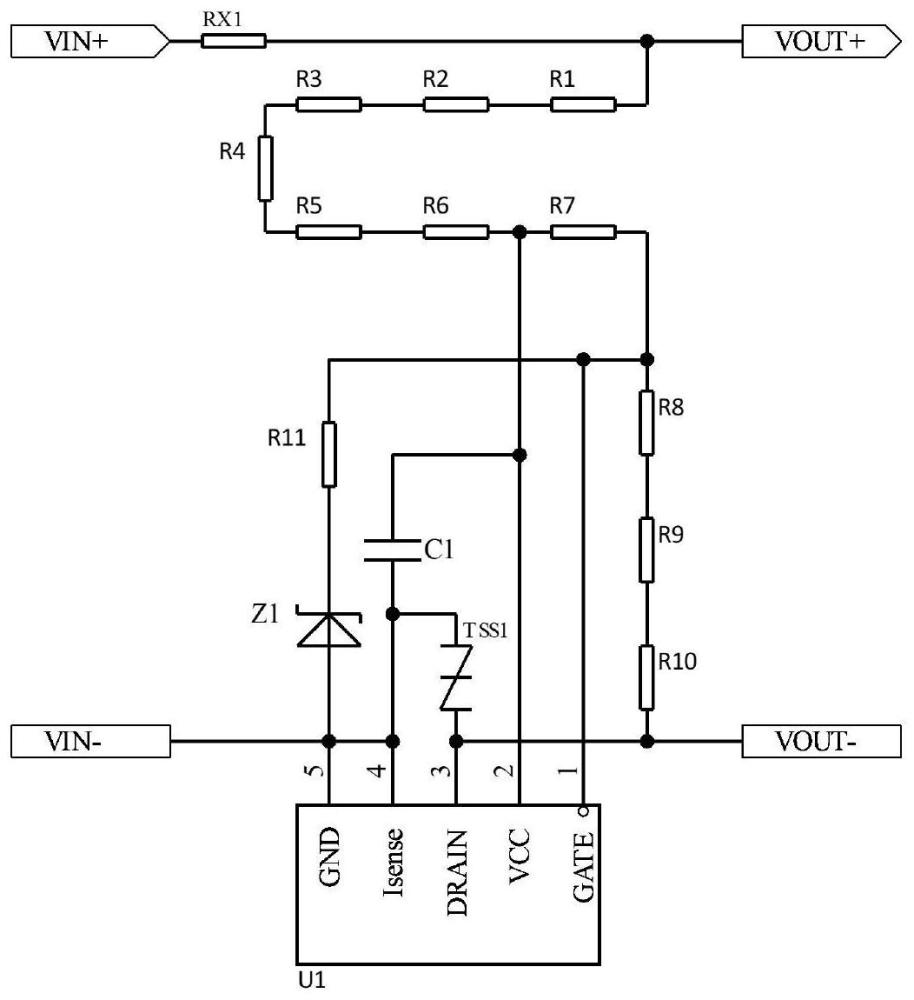

图1是采用高压钳位保护芯片的保护电路结构示意图;

图2是本发明实施例高压钳位保护电路的电路结构示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明了,下面结合具体实施方式并参照附图,对本发明进一步详细说明。应该理解,这些描述只是示例性的,而并非要限制本发明的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本发明的概念。

下面对结合附图对本发明的技术方案进行详细说明。根据本发明的一个实施例,提供了一种适用于电能表的抗浪涌高压钳位保护电路。高压钳位保护电路常用于中小功率工业仪表高压电源供电解决方案,一般用在开关电源电路的高压电解电容、高频变压器、开关电源控制芯片前端,起到输入过压钳位保护作用。本发明实施例的高压钳位保护电路采用高压钳位保护芯片加上外围器件组成的保护电路,元件少、体积小,占用较少的电路板空间,当输入电压在钳位阈值电压以下时高压钳位保护芯片内置MOS管一直处于导通状态,无开关损耗,具有较明显的优势。在产品不带电情况下,高压钳位保护芯片(未启动工作)内置MOS管处于关断状态,电路不可承受产品要求的雷击浪涌试验,高压钳位保护芯片存在损坏风险。图1中示出了采用高压钳位保护芯片的保护电路结构示意图,图1中,U1为高压钳位保护芯片,在高压钳位保护芯片U1允许的输入电压范围内:当输入电压VIN(VIN+与VIN-之间)低于设定的钳位阈值时,保持输出电压VOUT(VOUT+与VOUT-之间)几乎等于输入电压;当输入电压高于设定的钳位阈值时,输出电压钳位在设定阈值。雷击瞬间由于电压上升快(μs级),高压钳位保护芯片U1(ms级)响应不了,其内置的MOS管漏源极间(DRAIN脚和Isense脚间)电压会瞬间升高,为了保证内置MOS管不被过压损坏,引入线绕电阻RX1。在产品带电测试浪涌时,高压钳位保护芯片U1内置MOS管漏源极间为导通状态,合适阻值的线绕电阻RX1能起到较好的限流保护作用,产品带电浪涌试验一般无问题。如果产品需要不带电测试浪涌(模拟电网断电时遭遇雷击的情况),由于高压钳位保护芯片U1未启动工作,其内置MOS管漏源极间为截止状态,浪涌电压施加瞬间会产生超过芯片内置MOS管漏源极耐压极限值的脉冲电压,从而将高压钳位保护芯片U1击穿损坏。考虑到此种情况,本发明实施例的高压钳位保护电路在上述电路的基础上增设了浪涌保护单元,通过在该高压钳位保护芯片U1内置的MOS管漏源极间(DRAIN脚和Isense脚间)增加浪涌保护单元来保护芯片,以保证产品能够承受在不带电条件下的浪涌测试。图2中示出了本发明实施例高压钳位保护电路的电路结构示意图,该高压钳位保护电路包括第一电阻网络、第二电阻网络和高压钳位保护芯片;所述第一电阻网络连接于该保护电路的输入电压正极和输出电压正极之间;所述第二电阻网络连接于该保护电路的输入电压负极和输出电压负极之间;所述第一电阻网络、第二电阻网络和高压钳位保护芯片依次相互连接;所述高压钳位保护芯片包括内置MOS管,在所述内置MOS管的源极和漏极之间设置浪涌保护单元。

第一电阻网络可以包括线绕电阻RX1和第一串联电阻串;所述线绕电阻RX1的两端分别连接输入电压正极VIN+和输出电压正极VOUT+。该第一串联电阻串包括多个串联连接的电阻,例如包括第一电阻R1、第二电阻R2、第三电阻R3、第四电阻R4、第五电阻R5、第六电阻R6和第七电阻R7,所述第一串联电阻串的一端连接输出电压正极VOUT+,另一端连接第二电阻网络。

第二电阻网络包括第二串联电阻串、稳压保护单元和浪涌保护单元。该第二串联电阻串包括多个串联连接的电阻,例如包括第八电阻R8、第九电阻R9和第十电阻R10,所述第二串联电阻串的一端连接第一串联电阻串,另一端连接输出电压负极VOUT-。

稳压保护单元的一端连接第一电阻网络,另一端连接输入电压负极。该稳压保护单元包括稳压电阻R11、稳压管Z1和电容C1;其中,稳压管Z1的阳极连接于所述输入电压负极VIN-和高压钳位保护芯片U1的接地端GND,阴极通过所述稳压电阻R11连接至第一串联电阻串和第二串联电阻串的连接点,电容C1的一端连接第六电阻R6和第七电阻R7的连接点,另一端连接至高压钳位保护芯片U1的Isense端。

该浪涌保护单元例如可以为半导体放电管或压敏电阻。当设计空间较小时,宜选用半导体放电管,半导体放电管的选择应满足如下要求:

(1)半导体放电管的转折电压(VS)应大于电路正常工作范围上限时高压钳位芯片内置MOS管漏源极间的电压值、小于高压钳位芯片内置MOS管漏源极间耐压值的规格,并注意保留一定余量。

(2)半导体放电管的重复峰值脉冲电流(IPP)应大于应用产品在浪涌测试条件下的最大电流,并留有一定余量。

当设计空间充裕时,可以选用压敏电阻,该压敏电阻的选择应满足如下要求:

(1)压敏电阻的最大连续直流工作电压应大于电路正常工作范围上限时高压钳位芯片内置MOS管漏源极间的电压值。

(2)压敏电阻的压敏电压应小于高压钳位芯片内置的MOS管漏源极间耐压值的规格,并注意保留一定余量。

(3)压敏电阻的通流容量应大于应用产品在浪涌测试条件下的最大电流,并留有一定余量。

通过在电路中设置所述浪涌保护单元,既不影响产品正常工作和带电浪涌试验,又可保证产品能够承受在不带电条件下的浪涌试验,弥补了现有技术的不足,提升了产品可靠性。

综上所述,本发明涉及一种适用于电能表的抗浪涌高压钳位保护电路,该高压钳位保护电路用于电能表的输入过压钳位保护,包括第一电阻网络、第二电阻网络和高压钳位保护芯片;所述第一电阻网络连接于该保护电路的输入电压正极和输出电压正极之间;所述第二电阻网络连接于该保护电路的输入电压负极和输出电压负极之间;所述第一电阻网络、第二电阻网络和高压钳位保护芯片依次相互连接;所述高压钳位保护芯片包括内置MOS管,在所述内置MOS管的源极和漏极之间设置浪涌保护单元。通过在电路中设置浪涌保护单元,解决了在不带电情况下,采用专用高压钳位保护芯片设计的保护电路无法满足产品要求的雷击浪涌试验的问题,弥补现有技术的不足,有效提高电路可靠性。

应当理解的是,本发明的上述具体实施方式仅仅用于示例性说明或解释本发明的原理,而不构成对本发明的限制。因此,在不偏离本发明的精神和范围的情况下所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。此外,本发明所附权利要求旨在涵盖落入所附权利要求范围和边界、或者这种范围和边界的等同形式内的全部变化和修改例。