一种有源谐振负载电路及时钟树驱动电路

文献发布时间:2023-06-19 11:39:06

技术领域

本申请涉及集成电路技术领域,尤其涉及一种有源谐振负载电路及时钟树驱动电路。

背景技术

现有的时钟信号输传电路(也称时钟树网络电路),通常由驻波电路单元或行波电路单元组成。驻波电路单元通常由CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)构成,在由驻波单元电路组成的时钟树网络电路中,可以通过发送一个时钟信号波形,在传输线末端反射形成一个和原波形相同频率、相位差为180°的反射波形,原波形和反射波形经过叠加形成驻波;驻波在传输线的各个节点具有相同的相位,但是,随着时钟信号的传输,时钟信号的幅值会发生损失,造成形成驻波的原波形和反射波形的幅值不一致,引起额外的时钟扰动(skew),还会导致时钟信号的幅值发生衰减。行波电路单元通常是由两个首尾相接的反相器构成的闭合回路,闭合回路中各个点的时钟信号波形幅值相等,但是随着时钟信号的传输,传输线上各个点的相位随位置的变化而变化,引起额外的时钟时序异步性问题,从而产生不同程度的噪声(jitter)。另外,无论是由驻波电路单元还是由行波电路单元组成的时钟树网络电路,随着电路工作频率越来越高,传输的时钟信号会对电路中的扰动和噪声越来越敏感。

发明内容

本发明提供了一种有源谐振负载电路及时钟树驱动电路,可以改善时钟信号沿着现有时钟树网络电路传输,时钟信号受电路扰动而产生噪声或者幅值衰减的问题。

第一方面,一种有源谐振负载电路,包括:至少一个差分环形振荡回路;

每个所述差分环形振荡回路包括三个或三个以上的奇数个首尾电连接的延迟单元,其中,所述延迟单元用于调整所述差分环形振荡回路的振荡频率至输入所述差分环形振荡回路的时钟信号的频率,以及,对所述时钟信号的幅值进行放大,前一个所述延迟单元的负相位输出端与后一个所述延迟单元的正相位输入端电连接,前一个所述延迟单元的正相位输出端与后一个所述延迟单元的负相位输入端电连接,所述正相位输入端和所述负相位输入端用于接收所述时钟信号;

所述差分环形振荡回路包括第二负载调节单元,所述第二负载调节单元设置在前一个所述延迟单元的所述负相位输出端与后一个所述延迟单元的所述正相位输入端之间。

根据一种可行的实施方式,所述延迟单元包括:对称设置的第一放大调频单元和第二放大调频单元,所述第一放大调频单元和所述第二放大调频单元分别设置有第一负载调节单元,其中,所述第一负载调节单元用于调节所述第一放大调频单元和所述第二放大调频单元的电路负载,以调整所述差分环形振荡回路的所述振荡频率;

所述时钟信号包括正相位时钟信号和负相位时钟信号;

所述第一放大调频单元分别与所述正相位输入端和所述负相位输出端电连接,所述第一放大调频单元用于对所述正相位时钟信号的幅值进行放大,以及对所述正相位时钟信号的相位进行延迟;

所述第二放大调频单元分别与所述负相位输入端和所述正相位输出端电连接,所述第二放大调频单元用于对所述负相位时钟信号的幅值进行放大,以及对所述负相位时钟信号的相位进行延迟。

根据一种可行的实施方式,所述延迟单元还包括固定电流源,所述第一放大调频单元还设置有第一MOS管,所述第二放大调频单元还设置有第二MOS管;

所述第一MOS管的栅电极与所述正相位输入端电连接,所述第一MOS管的漏电极与所述负相位输出端电连接,所述第一MOS管的的源电极用于与所述固定电流源电连接;所述第一放大调频单元对应的所述第一负载调节单元的一端与所述负相位输出端电连接,另一端用于接入高电平;

所述第二MOS管的栅电极与所述负相位输入端电连接,所述第二MOS管的漏电极与所述正相位输出端电连接,所述第二MOS管的源电极用于与所述固定电流源电连接;所述第二放大调频单元对应的所述第一负载调节单元的一端与所述正相位输出端电连接,另一端用于接入高电平;

所述第一负载调节单元包括串联负载调节单元。

根据一种可行的实施方式,所述第一放大调频单元和所述第二放大调频单元还分别设置有可调电流源单元,所述可调电流源单元与所述固定电流源并联。

根据一种可行的实施方式,所述可调电流源单元包括电流源和与所述电流源串联的开关,所述电流源与所述开关串联后与所述固定电流源并联。

根据一种可行的实施方式,所述串联负载调节单元包括:固定电阻和/或可调电阻,及与所述固定电阻和/或所述可调电阻串联的开关。

根据一种可行的实施方式,所述串联负载调节单元包括:可调电阻。

根据一种可行的实施方式,所述第一负载调节单元还包括并联负载调节单元,所述并联负载调节单元包括并联的所述串联负载调节单元。

根据一种可行的实施方式,所述第一负载调节单元还包括串联电容调节单元;

所述第一放大调频单元对应的所述串联电容调节单元的一端与所述负相位输出端电连接,另一端用于接地;

所述第二放大调频单元对应的所述串联电容调节单元的一端与所述正相位输出端电连接,另一端用于接地。

根据一种可行的实施方式,述第一负载调节单元还包括并联电容调节单元,所述并联电容调节单元包括并联的所述串联电容调节单元。

根据一种可行的实施方式,所述串联电容调节单元包括:固定电容和/或可调电容,及与所述固定电容和/或所述可调电容串联的开关。

根据一种可行的实施方式,所述串联电容调节单元包括:可调电容。

根据一种可行的实施方式,所述第二负载调节单元包括电阻。

第二方面,一种时钟树驱动电路,包括:时钟树网络电路、缓冲放大电路、DQs信号线和第一方面所述的有源谐振负载电路;

所述缓冲放大电路用于接收所述时钟树网络电路输出的时钟信号,所述有源谐振负载电路分别与所述缓冲放大电路和所述DQs信号线电连接。

本实施例提供的有源谐振负载电路及时钟树驱动电路,有源谐振负载电路中的每个差分环形振荡回路通过多个级联的延迟单元对时钟信号的幅值进行逐级放大,可以增大从时钟树网络电路输出的时钟信号的幅值,将从时钟树网络电路中衰减掉的时钟信号幅值恢复。另外,通过调节每个延迟单元的电路参数来实现调节差分环形振荡回路的振荡频率,以使差分环形振荡回路的振荡频率与输入的时钟信号的频率达到一致,容易理解的是实际应用中一致的情况可以看作无限接近,当差分环形振荡回路的振荡频率达到输入时钟信号的频率时,从时钟树网络电路输出的时钟信号再输入差分环形振荡回路,差分环形振荡回路不会产生由于电路振荡而发生的扰动和噪声;另外,差分环形振荡回路的振荡频率与输入的时钟信号的频率一致,还能够优化时钟信号波形的上升沿和下降沿,能够最大程度的优化噪声,对共模噪声的抑制能力更强,从而起到消除或减弱干扰和噪声的作用,还能够提高整个差分环形振荡回路的响应速度。

附图说明

图1为本申请实施例提供的一种有源谐振负载电路的示意图;

图2为本申请实施例提供的一种差分环形振荡回路的示意性电路图;

图3为本申请实施例提供的另一种差分环形振荡回路的示意性电路图;

图4为本申请实施例提供的一种延迟单元的示意性电路图;

图5为本申请实施例提供的另一种延迟单元的示意性电路图;

图6为本申请实施例提供的又一种延迟单元的示意性电路图;

图7为本申请实施例提供的再一种延迟单元的示意性电路图;

图8a为本申请实施例提供的一种未引入谐振负载电路的噪声模拟仿真时钟树网络电路输出波形的眼图;

图8b为本申请实施例提供的一种引入谐振负载电路后噪声模拟仿真时钟树网络电路输出波形的眼图;

图9为本申请实施例提供的一种延迟单元的示意性电路图;

图10为本申请实施例提供的另一种延迟单元的示意性电路图;

图11为本申请实施例提供的又一种延迟单元的示意性电路图;

图12a为本申请实施例提供的一种未引入谐振负载电路的噪声模拟仿真时钟树网络电路输出波形的眼图;

图12b为本申请实施例提供的一种引入谐振负载电路后噪声模拟仿真时钟树网络电路输出波形的眼图;

图13为本申请实施例提供的一种时钟树驱动电路的示意性结构框图。

具体实施方式

为了更好的理解本说明书实施例提供的技术方案,下面通过附图以及具体实施例对本说明书实施例的技术方案做详细的说明,应当理解本说明书实施例以及实施例中的具体特征是对本说明书实施例技术方案的详细的说明,而不是对本说明书技术方案的限定,在不冲突的情况下,本说明书实施例以及实施例中的技术特征可以相互组合。

在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。术语“两个以上”包括两个或大于两个的情况。

鉴于时钟信号沿着现有时钟树网络电路传输,时钟信号受电路扰动而产生噪声或者幅值衰减的问题,本申请实施例提供一种有源谐振负载电路,可以包括至少一个差分环形振荡回路。

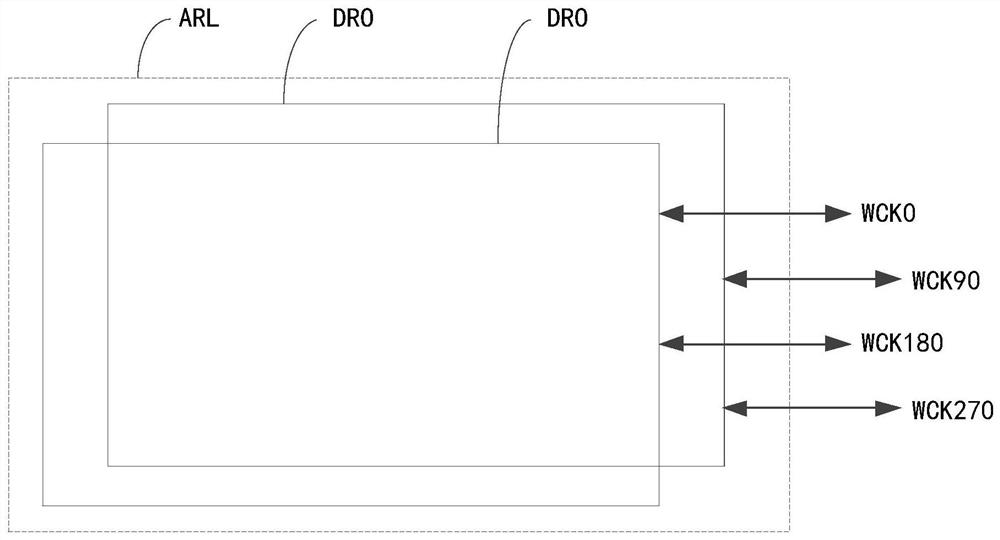

在一种可行的实施方式中,图1为本申请实施例提供的一种有源谐振负载电路的示意图。如图1所示,本实施例提供一种有源谐振负载电路ARL,包括2个差分环形振荡回路DRO。图1只是示意性的,有源谐振负载电路ARL包括差分环形振荡回路DRO的数量还可以是1个、3个或者更多,本申请不做具体限定。有源谐振负载电路ARL可以连接在时钟树网络电路之后,用于接收时钟树网络电路输出的时钟信号,不同的差分环形振荡回路DRO可以接收不同相位的时钟信号,以图1为例进行说明,每个差分环形振荡回路DRO包括两个相位的输入输出端,分别为正相位输入输出端和负相位输入输出端,正相位输入输出端和负相位输入输出端可以分别是WCK0(0°相位的时钟信号输入输出端)和WCK180(180°相位的时钟信号输入输出端),不同差分环形振荡回路DRO对应的正相位输入输出端和负相位输入输出端接收到的时钟信号相位可以是不同的,如图1所示,另外一个差分环形振荡回路DRO的正相位输入输出端WCK90和负相位输入输出端WCK270对应的时钟信号的相位分别为90°和270°。因此,可以根据时钟树网络电路输出时钟信号的引脚数量设定有源谐振负载电路ARL中差分环形振荡回路DRO的数量。

在一种可行的实施方式中,每个差分环形振荡回路可以包括三个或三个以上的奇数个首尾电连接的延迟单元,其中,延迟单元用于调整差分环形振荡回路的振荡频率至输入差分环形振荡回路的时钟信号的频率,以及,对时钟信号的幅值进行放大,前一个延迟单元的负相位输出端与后一个延迟单元的正相位输入端电连接,前一个延迟单元的正相位输出端与后一个延迟单元的负相位输入端电连接,正相位输入端和负相位输入端用于接收所述时钟信号。图2为本申请实施例提供的一种差分环形振荡回路的示意性电路图。如图2所示,上述实施方式中提到的差分环形振荡回路DRO包括3个延迟单元,分别是D1、D2和D3,延迟单元D1、D2和D3依次首尾电连接形成一个环形回路。

图3为本申请实施例提供的另一种差分环形振荡回路的示意性电路图。如图3所示,上述实施方式中提到的差分环形振荡回路DRO包括5个延迟单元,分别是D1、D2、D3、D4和D5,延迟单元D1、D2、D3、D4和D5依次首尾电连接形成一个环形回路。

图2和图3只是示意性的,差分环形振荡回路含有的延迟单元的数量只要满足是3个或者大于3个的奇数即可,本申请不作具体限定。

示例性的,结合图2和图3,每个延迟单元都设置有正相位输入端Vinp、负相位输入端Vinn、正相位输出端Voutp和负相位输出端Voutn。在差分环形振荡回路中,前一个延迟单元的负相位输出端Voutn与后一个延迟单元的正相位输入端Vinp电连接,前一个延迟单元的正相位输出端Voutp与后一个延迟单元的负相位输入端Vinn电连接。需要说明的是,前一个和后一个具有相对性,但必须是相邻的两个延迟单元之间。示例性的,如图2所示,相邻的D1和D2之间,D1属于前一个,D2属于后一个;相邻的D2和D3之间,D2属于前一个,D3属于后一个;相邻的D3和D1之间,D3属于前一个,D1属于后一个;图3与图2同理。结合图2和图3,任意相邻的负相位输出端Voutn与正相位输入端Vinp之间可以引出正相位输入输出端WCK0,任意相邻的正相位输出端Voutp与负相位输入端Vinn之间可以引出负相位输入输出端WCK180。每个延迟单元可以看作是等效的放大器,均可以对输入的时钟信号的幅值进行放大,多个延迟单元则对时钟信号的幅值进行逐级放大。奇数个延迟单元形成的差分环形振荡回路能够形成一个环形振荡器,每个延迟单元可以通过调节电路参数以达到调节差分环形振荡回路的振荡频率的目的。

本实施例提供的有源谐振负载电路,设置一个或者多个差分环形振荡回路,差分环形振荡回路通过多个级联的延迟单元形成,多个级联的延迟单元对时钟信号的幅值进行逐级放大,每个延迟单元可以通过调节电路参数来实现调节差分环形振荡回路的振荡频率。

差分环形振荡回路还包括第二负载调节单元,前一个延迟单元的负相位输出端与后一个延迟单元的正相位输入端之间,以及,前一个延迟单元的正相位输出端与后一个延迟单元的负相位输入端之间分别设置有第二负载调节单元。第二负载调节单元设置在相邻的两个延迟单元之间,能够进一步调节差分环形振荡回路的电路负载,进一步增大差分环形振荡回路的振荡频率可调宽度和调节精度,能够拓宽差分环形振荡回路的适用性。另外需要说明的是第二负载调节单元也会参与时钟信号的相位延迟,延迟相位等效在上述实施例提到的ΔP中。

在一种可行的实施方式中,第二负载调节单元可以包括电阻。示例性的,如图2所示,电阻R3可以是可调电阻,也可以是固定电阻,本申请不做具体限定。

由于时钟信号沿着现有时钟树网络电路传输,时钟信号受电路扰动而产生的噪声或者幅值衰减,引入本实施例提供的有源谐振负载电路,有源谐振负载电路中的每个差分环形振荡回路通过多个级联的延迟单元对时钟信号的幅值进行逐级放大,可以增大从时钟树网络电路输出的时钟信号的幅值,将从时钟树网络电路中衰减掉时钟信号的幅值恢复。另外,通过调节每个延迟单元的电路参数来实现调节差分环形振荡回路的振荡频率,以使差分环形振荡回路的振荡频率与输入的时钟信号的频率达到一致,容易理解的是实际应用中一致的情况可以看作无限接近,当差分环形振荡回路的振荡频率达到输入时钟信号的频率时,从时钟树网络电路输出的时钟信号再输入差分环形振荡回路,差分环形振荡回路不会产生由于电路振荡而发生的扰动和噪声;另外,差分环形振荡回路的振荡频率与输入的时钟信号的频率一致,还能够优化时钟信号波形的上升沿和下降沿,能够最大程度的优化噪声,对共模噪声的抑制能力更强,从而起到消除或减弱干扰和噪声的作用,还能够提高整个差分环形振荡回路的响应速度。

在另一种可行的实施方式中,延迟单元可以包括:对称设置的第一放大调频单元和第二放大调频单元,第一放大调频单元和第二放大调频单元分别设置有第一负载调节单元,其中,第一负载调节单元用于调节第一放大调频单元和第二放大调频单元的电路负载,以调整差分环形振荡回路的振荡频率;时钟信号包括正相位时钟信号和负相位时钟信号,正相位时钟信号和负相位时钟信号之间的相位差为180°,因此,同一个差分环形振荡回路的正相位输入输出端与负相位输入输出端之间的相位差为180°。第一放大调频单元分别与正相位输入端和负相位输出端电连接,第一放大调频单元用于对正相位时钟信号的幅值进行放大,以及对正相位时钟信号的相位进行延迟;第二放大调频单元分别与负相位输入端和正相位输出端电连接,第二放大调频单元用于对负相位时钟信号的幅值进行放大,以及对负相位时钟信号的相位进行延迟。示例性的,每个延迟单元对输入的时钟信号具有相位延迟的效果,每个延迟单元产生的相位延迟为180°+ΔP,ΔP可以看作是第一负载调节单元的等效相位延迟,3个或大于3的奇数个延迟单元的相位延迟能够满足是360°的整数倍,并且每个延迟单元的增益大于1,同时满足这两个条件,可以达到差分环形振荡回路的起振条件(所有延迟单元延迟相位的叠加是360°的整数倍)。具体的,以图2为例,每个延迟单元的相位延迟是180°+60°,3个延迟单元的相位延迟是720°(180°*3+60°*3)。如图3所示,每个延迟单元的相位延迟是180°+36°,5个延迟单元的相位延迟是1080°(180°*5+36°*5)。第一放大调频单元和第二放大调频单元对称设置,所以两者对于时钟信号相位的延迟是相同的,但是,两者输入的时钟信号相位相差180°。

本实施例提供的有源谐振负载电路,通过在延迟单元内设置相互对称的第一放大调频单元和第二放大调频单元,第一放大调频单元对正相位时钟信号的幅值进行放大以及对正相位时钟信号的相位进行延迟,第二放大调频单元对负相位时钟信号的幅值进行放大,以及对负相位时钟信号的相位进行延迟。第一放大调频单元和第二放大调频单元内分别设置有相同的第一负载调节单元,可以通过第一负载调节单元对第一放大调频单元和第二放大调频单元的电路负载进行调节,通过调节电路负载能够实现调节电路电流,进而能够调节差分环形振荡回路的振荡频率。

示例性的,在其余条件不变的情况下,通过调节第一负载调节单元中的参数,实现同步增大每个延迟单元中第一放大调频单元和第二放大调频单元的电路电阻,电路电流则会减小,振荡频率则会减小;在其余条件不变的情况下,通过调节第一负载调节单元中的参数,实现同步增大电路电容,振荡频率则会减小。当差分环形振荡回路的振荡频率高于输入的时钟信号的频率时,需要下调差分环形振荡回路的振荡频率,以使二者无限趋于一致;当差分环形振荡回路的振荡频率低于输入的时钟信号的频率时,需要上调差分环形振荡回路的振荡频率,以使二者无限趋于一致。第一负载调节单元的设置能够增大整个差分环形振荡回路的振荡频带宽度,能够拓宽差分环形振荡回路的适用性。

在一种可行的实施方式中,示例性的,图4为本申请实施例提供的一种延迟单元的示意性电路图。如图4所示,延迟单元还包括固定电流源i0,第一放大调频单元T1还设置有第一MOS管M1,第二放大调频单元T2还设置有第二MOS管M2。第一MOS管M1的栅电极与正相位输入端Vinp电连接,第一MOS管M1的漏电极与负相位输出端Voutn电连接,第一MOS管M1的源电极用于与固定电流源i0电连接,固定电流源i0的另一端接地;第一放大调频单元T1对应的第一负载调节单元L1的一端与负相位输出端Voutn电连接,另一端用于接入高电平。第二MOS管M2的栅电极与负相位输入端Vinn电连接,第二MOS管M2的漏电极与正相位输出端Voutp电连接,第二MOS管M2的源电极用于与固定电流源i0电连接;第二放大调频单元T2对应的第一负载调节单元L1的一端与正相位输出端Voutp电连接,另一端用于接入高电平。第一MOS管M1和第二MOS管M2用于对输入的时钟信号产生180°的相位延迟。固定电流源i0用于给第一MOS管M1和第二MOS管M2提供基础工作电流,能够使得第一MOS管M1和第二MOS管M2持续导通。第一MOS管M1和第二MOS管M2分别结合第一负载调节单元L1,可以对各自输入的时钟信号的幅值进行放大。第一负载调节单元L1的等效电阻可以对输入时钟信号的相位产生相位延迟ΔP,如此,每个延迟单元对于输入时钟信号的相位延迟为180°+ΔP。示例性的,第一负载调节单元L1可以包括串联负载调节单元。第一MOS管和第二MOS管可以采用NMOS管。

本实施例提供的有源谐振负载电路,采用MOS管结合负载的电路结构能够实现相位延迟和幅值放大的效果。第一负载调节单元采用串联负载调节单元能够实现负载的调节。

在一种可行的实施方式中,示例性的,图5为本申请实施例提供的另一种延迟单元的示意性电路图。如图5所示,第一放大调频单元T1和第二放大调频单元T2还分别设置有可调电流源单元A,可调电流源单元A与固定电流源i0可以并联。示例性的,可调电流源单元A可以包括电流源i1和与电流源i1串联的开关Si1,电流源i1与开关Si1串联后再与固定电流源i0并联。开关Si1的闭合或者断开可以控制电流源i1是否接入对应的MOS管,当开关Si1闭合,电流源i1导通,可以增加电路中的工作电流。图5所示的两个开关Si1的闭合和断开可以是不同步的,也可以是同步的,同步闭合,电路中的工作电流双倍增大,单独闭合电流只增大一倍。两个电流源i1的参数也可以相同或不同,本申请不作具体限定。

本实施例提供的有源谐振负载电路,增设可调电流源单元,控制可调电流源单元的通断能够实现调节对应电路的电流,从而能够辅助第一负载调节单元对于电路负载的调节,能够进一步增大整个差分环形振荡回路的振荡频带宽度,能够拓宽差分环形振荡回路的适用性。

在一种可行的实施方式中,上述实施例提到的串联负载调节单元可以包括:固定电阻和/或可调电阻,及与固定电阻和/或可调电阻串联的开关。示例性的,图6为本申请实施例提供的又一种延迟单元的示意性电路图。如图6所示,前述实施例所提到的串联负载调节单元可以包括电阻R1和开关SR1,电阻R1与开关SR1串联,电阻R1可采用调电阻也可以采用固定电阻。开关SR1的闭合和断开能够实现电阻R1是否接入第一放大调频单元或者第二放大调频单元。例如,当两个开关SR1同步闭合,两个电阻R1分别接入第一放大调频单元和第二放大调频单元,电路中的电阻值增大,电流值减小,振荡频率降低。另外,当电阻R1采用可调电阻时,可以在两个开关SR1同步闭合时,同步调节两个可调电阻R1的阻值以改变电路中的电阻值,实现对振荡频率的调节。图6所示只是示意性的示出连接一个固定电流源i0的情况,本申请不作具体限定。开关的闭合和通断,可调电阻阻值调节的幅度需要根据输入时钟信号的频率确定,例如,当输入时钟信号的频率大于差分环形振荡回路的振荡频率时,需要通过调节开关或者调节可调电阻的阻值,达到下调差分环形振荡回路的振荡频率的效果,以使输入时钟信号的频率与差分环形振荡回路的振荡频率趋于相同。具体的,振荡频率的下调需要减小电路中的负载,可以同步断开两个开关SR1或者同步下调两个可调电阻R1的阻值。可调电阻结合开关的使用能够增大第一负载调节单元的负载调节范围,进一步增大整个差分环形振荡回路的振荡频率可调宽度,能够拓宽差分环形振荡回路的适用性。

在一种可行的实施方式中,上述实施例提到的串联负载调节单元可以包括可调电阻。在可调电阻具有较大调节范围时,可调电阻可以单独实现调节电路负载的作用。

在一种可行的实施方式中,第一负载调节单元还可以包括并联负载调节单元,并联负载调节单元可以包括并联的串联负载调节单元。示例性的,图7为本申请实施例提供的再一种延迟单元的示意性电路图。如图7所示,电阻R1与开关SR1串联可视为一个串联负载调节单元,电阻R2与开关SR2串联可视为一个串联负载调节单元,两个串联负载调节单元相互并联,形成并联负载调节单元。图7只是示意性的,并联负载调节单元还可以包括更多串联负载调节单元,本申请不做具体限定。另外需要说明的是,电阻R1和电阻R2可以采用固定电阻,也可以采用可调电阻,两者的阻值可以相同也可以不同;可调电阻R1和可调电阻R2的可调阻值范围可以相同也可以不同,串联负载调节单元还可以只包括可调节电阻,不包括开关,本申请的各个实施例之间可做任意组合,此处不做一一例举。多个串联负载调节单元的并联,可以进一步增强第一负载调节单元的阻值调节范围和阻值调节精度,进一步增大差分环形振荡回路的振荡频率可调宽度和调节精度,能够拓宽差分环形振荡回路的适用性。

通过在时钟树网络电路的电源上额外附加一个干扰信号来模拟电路中的噪声,干扰信号可以为振幅50mA及频率为200HZ的正弦信号,对包括图7所示的延迟单元的有源谐振负载电路进行波形仿真。图8a为本申请实施例提供的一种未引入谐振负载电路的噪声模拟仿真时钟树网络电路输出波形的眼图;图8b为本申请实施例提供的一种引入谐振负载电路后噪声模拟仿真时钟树网络电路输出波形的眼图。图8a的眼图宽度为202p,图8b的眼图宽度为225p,眼图宽度增长了约11.4%。图8a的眼图skew为73.1p,图8b的眼图skew为52.3p,眼图skew改善了28.5%。因此,由图8a和图8b可以看出,本申请实施例提供的有源谐振负载电路能够明显的优化时钟信号的skew。需要说明的是眼图skew越小,时钟信号受到噪声的干扰越小,电路对噪声的抑制能力越强,眼图宽度越大,在数据读取过程中越不容易出错。

在一种可行的实施方式中,第一负载调节单元还可以包括串联电容调节单元。第一放大调频单元对应的串联电容调节单元的一端与负相位输出端电连接,另一端用于接地;第二放大调频单元对应的串联电容调节单元的一端与正相位输出端电连接,另一端用于接地。串联电容调节单元可以通过电容的调节实现对电路负载的调节,能够增大第一负载调节单元对电路负载的调节范围和精度,进而增大对差分环形振荡回路的振荡频率的调节范围和调节精度。

在一种可行的实施方式中,上述实施例所示提到的串联电容调节单元可以包括:固定电容和/或可调电容,及与固定电容和/或可调电容串联的开关。或者串联电容调节单元包括可调电容。示例性的,图9为本申请实施例提供的一种延迟单元的示意性电路图。如图9所示,串联电容调节可以包括可调电容C1。第一放大调频单元对应的可调电容C1的一端连接到串联负载调节单元与负相位输出端Voutn之间的等电位点V1上,可调电容C1的另一端接地。第二放大调频单元对应的可调电容C1的一端连接到串联负载调节单元与正相位输出端Voutp之间的等电位点V2上,可调电容C1的另一端接地。图9所示的是串联负载调节单元,串联负载调节单元包括串联的电阻R1和开关SR1。图10为本申请实施例提供的另一种延迟单元的示意性电路图。如图10所示,第一负载调节单元包括并联负载调节单元。可调电容C1还可以串联开关,C2还可以是固定电容,本申请保护范围内的其他实施例,此处不做一一列举,本申请实施例之间可做任意组合。串联电容调节单元的设置,可以进一步增强第一负载调节单元的电容调节范围,进一步增大差分环形振荡回路的负载调节范围和调节精度,进而增大振荡频率可调宽度,能够拓宽差分环形振荡回路的适用性。

在一种可行的实施方式中,第一负载调节单元还可以包括并联电容调节单元,并联电容调节单元包括并联的串联电容调节单元。示例性的,图11为本申请实施例提供的又一种延迟单元的示意性电路图。如图11所示,电容C1和电容C2分别串联有开关SC1和开关SC2,电容C1和电容C2可以采用可调电容或者固定电容。开关SC1和开关SC2的闭合和断开可以分别控制电容C1和电容C2的通断,设置多个串联电容调节单元相互并联,能够进一步增大电容调节单元的容值调节范围和容值调节精度,进一步增大差分环形振荡回路的振荡频率可调宽度和调节精度,能够拓宽差分环形振荡回路的适用性。

通过在时钟树网络电路的电源上附加一个干扰信号来模拟电路中的噪声,干扰信号可以为振幅50mA及频率为200HZ的正弦信号,对包括图11所示的延迟单元的有源谐振负载电路进行波形仿真。图12a为本申请实施例提供的一种未引入谐振负载电路的噪声模拟仿真时钟树网络电路输出波形的眼图;图12b为本申请实施例提供的一种引入谐振负载电路后噪声模拟仿真时钟树网络电路输出波形的眼图。图12a的眼图宽度为202p,图12b的眼图宽度为231p,眼图宽度增长了约14.4%。图12a的眼图skew为73.2p,图12b的眼图skew为44.3p,眼图skew改善了39.4%。因此,由图12a和图12b可以看出,本申请实施例提供的有源谐振负载电路能够明显的优化时钟信号的skew。需要说明的是眼图skew越小,时钟信号受到噪声的干扰越小,电路对噪声的抑制能力越强,眼图宽度越大,在数据读取过程中越不容易出错。

第二方面,本申请实施例提供一种时钟树驱动电路,包括:时钟树网络电路、缓冲放大电路、DQs(Bi-d i rect iona l Data strobe双向数据控制引脚)信号线和上述任一实施方式中的有源谐振负载电路;缓冲放大电路用于接收时钟树网络电路输出的时钟信号,有源谐振负载电路分别与缓冲放大电路和所述DQs信号线电连接。示例性的,图13为本申请实施例提供的一种时钟树驱动电路的示意性结构框图。如图13所示,本实施例的一种时钟树驱动电路,包括:时钟树网络电路WCKM、缓冲放大电路B、DQs信号线Q和上述任一实施方式的有源谐振负载电路ARL;时钟树网络电路WCKM与缓冲放大电路B电连接,有源谐振负载电路ARL包括两个差分环形振荡回路DRO,有源谐振负载电路ARL分别与缓冲放大电路B和DQs信号线Q电连接。时钟信号WCK从时钟树网络电路WCKM传输至缓冲放大电路B,缓冲放大电路B可以通过时钟通道WCK Lane将时钟信号WCK传输至有源谐振负载电路ARL,缓冲放大电路B可以采用CML Buffer电路。

本实施例提供的时钟树驱动电路,设置有源谐振负载电路,有源谐振负载电路包括至少一个差分环形振荡回路,差分环形振荡回路通过多个级联的延迟单元对时钟信号的幅值进行逐级放大,可以增大从时钟树网络电路输出的时钟信号的幅值,对经过时钟树网络电路衰减掉的时钟信号幅值进行一定程度的恢复,对时钟信号的边沿(上升沿和下降沿)进行优化。另外,通过调节每个延迟单元的电路参数来实现调节差分环形振荡回路的振荡频率,以使差分环形振荡回路的振荡频率与输入的时钟信号的频率达到一致,容易理解的是实际应用中一致的情况可以看作无限接近,当差分环形振荡回路的振荡频率达到输入时钟信号的频率时,从时钟树网络电路输出的时钟信号再输入差分环形振荡回路,差分环形振荡回路不会产生由于电路振荡而发生的扰动和噪声;另外,差分环形振荡回路的振荡频率与输入的时钟信号的频率一致,还能够优化时钟信号波形的上升沿和下降沿,能够消除或减弱干扰和噪声,还能够提高整个差分环形振荡回路的响应速度。

本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所附权利要求意欲解释为包括优选实施例以及落入本说明书范围的所有变更和修改。本领域的技术人员可以对本说明书进行各种改动和变型而不脱离本说明书的精神和范围。倘若这些修改和变型属于本说明书权利要求及其等同技术的范围之内,则本说明书也意图包含这些改动和变型在内。

- 一种有源谐振负载电路及时钟树驱动电路

- 一种延迟时间稳定的时钟树驱动电路