一种低硬件开销的分段线性函数的硬件实现方法

文献发布时间:2023-06-19 11:42:32

技术领域

本发明涉及人工智能及集成电路技术领域,具体为一种低硬件开销的分段线性函数的硬件实现方法。

背景技术

随着人工智能的蓬勃发展,很多行业和领域都开始运用人工智能来解决实际问题,人工智能技术被广泛地应用于图像识别,语音识别,医疗卫生以及自动驾驶等各个领域。人工智能的快速发展得益于各种学习算法的研究突破,其中脉冲神经网络(SNN)是一种基于离散神经脉冲进行信息处理的神经网络,它具有更高的生物学可信度和更有效的计算能力。

传统上,SNN以软件的方式实现为主,但软件实现无法充分利用神经网络高并行性的特点,处理速度慢、且功耗高。为了充分利用脉冲神经网络的优点,工业界和学术界开始对脉冲神经网络进行硬件实现:英国帝国理工大学的D.Goodman研发了脉冲神经网络的仿真平台Brian,目前已经进行到了第二代BRINA2;德国奥地利的W.Maass对脉冲神经元模型、网络拓扑结构,和相关应用进行了研究;日本东京大学N.kubota等将SNN应用到助力机器人以及行走机器人上。目前国内也开始重视脉冲神经网络的研究,在2019年末,清华大学的团队研发出了第一款可以同时支持脉冲神经网络和人工神经网络的“天机芯”,并且实时的演示其在无人驾驶领域的强大计算力,体现出了脉冲神经网络的应用潜力。

从网络的构成上来说,神经网络的主体由单个神经元构成,大量的神经元通过突触互连形成了神经网络。突触的权重会影响神经元之间的刺激程度,进而影响神经网络的判别结果。因此神经网络的学习,就是调整突触权重的过程,STDP就是一种最常见的权重调整规则,因此它是脉冲神经网络的重要组成部分,承担着训练网络,让网络进行学习的任务。STDP规则的硬件实现具有重要意义,为此,提出一种低硬件开销的分段线性函数的硬件实现方法。

发明内容

针对现有技术的不足,本发明提供了一种低硬件开销的分段线性函数的硬件实现方法,

一种低硬件开销的分段线性函数的硬件实现方法,分段线性函数实现方法包括以下步骤:

步骤一、确定指数函数的时间窗范围,范围之外的值近似为零;

步骤二、将STDP规则中的指数函数近似为分段线性函数,即各分段的表达式均为Y=a*Δt+b的形式;

步骤三、根据各分段的表达式,给每个分段设计对应的移位信号

步骤四、有Δt输入时,判断Δt所在的分段,用分段信号S表示Δt所在的分段;

步骤五、根据分段信号S,通过多路选择器选择相应的移位信号

步骤六、将Δt右移

步骤七、将第一次移位的结果右移

步骤八、利用加法器将寄存器1和2的值相加,得到a*Δt的值;

步骤九、利用加法器将a*Δt的值与b的值相加,得到分段线性函数的值,即指数函数的近似值;

步骤十、利用加法器,移位寄存器,乘法器,完成STDP规则中与参数相关的常规运算。

优选的,步骤二中a设置为2的幂或2的幂的线性组合。

优选的,该方法在有输入值时优先判断输入值所在分段,对处于任何分段的输入值,均利用信号控制完成两次移位运算和两次加法运算,得到函数计算结果,从而避免为函数的每个分段设计运算电路,低硬件开销的实现分段线性函数。

优选的,该方法利于硬件实现的STDP规则的近似模型,其特征在于:该近似模型将STDP规则中的指数函数近似为分段线性函数,每个线性分段的斜率均设置为2的指数次幂,并将STDP规则中的相关参数近似为2的指数次幂,使得乘法可被移位再相加代替,降低实现STDP规则实现的硬件开销。

优选的,利用低硬件开销的实现方法对分段线性函数进行实现,实现的STDP系统包含移位寄存器、加法器、多路选择器结构,系统对输入值进行移位相加代替分段函数的乘法运算,用加法器进行加法运算,利用移位代替突触参数的乘法运算,低硬件开销实现STDP规则。

优选的,STDP规则中,权重的调整量与前后两个神经元激活的时间差呈函数关系,典型的STDP学习窗函数如下所示:

优选的,Δw为要计算的权重修改量,Δt为神经元发出脉冲时间与接收到脉冲时间之差,

与现有技术相比,本发明具有如下有益效果:本发明为一种低硬件开销的分段线性函数的硬件实现方法,该实现方法设计的电路包括有移位寄存器,多路选择器,加法器等结构,该方法面向神经网络硬件加速,减少了电路资源的使用,提升了计算效率,具有低面积低功耗的特点,可减少指数函数实现的硬件规模,提升网络的计算效能。

附图说明

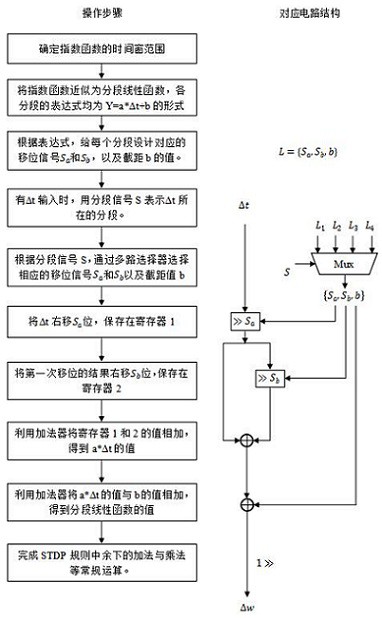

图1是本发明中设计的STDP规则实现结构具体实现步骤图。

具体实施方式

下面对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

如图1所示,本发明提供一种低硬件开销的分段线性函数的硬件实现方法,分段线性函数实现方法包括以下步骤:

步骤一、确定指数函数的时间窗范围,范围之外的值近似为零;

步骤二、将STDP规则中的指数函数近似为分段线性函数,即各分段的表达式均为Y=a*Δt+b的形式;

步骤三、根据各分段的表达式,给每个分段设计对应的移位信号

步骤四、有Δt输入时,判断Δt所在的分段,用分段信号S表示Δt所在的分段;

步骤五、根据分段信号S,通过多路选择器选择相应的移位信号

步骤六、将Δt右移

步骤七、将第一次移位的结果右移

步骤八、利用加法器将寄存器1和2的值相加,得到a*Δt的值;

步骤九、利用加法器将a*Δt的值与b的值相加,得到分段线性函数的值,即指数函数的近似值;

步骤十、利用加法器,移位寄存器,乘法器,完成STDP规则中与参数相关的常规运算。

步骤二中a设置为2的幂或2的幂的线性组合。

该方法在有输入值时优先判断输入值所在分段,对处于任何分段的输入值,均利用信号控制完成两次移位运算和两次加法运算,得到函数计算结果,从而避免为函数的每个分段设计运算电路,低硬件开销的实现分段线性函数。

该方法利于硬件实现的STDP规则的近似模型,其特征在于:该近似模型将STDP规则中的指数函数近似为分段线性函数,每个线性分段的斜率均设置为2的指数次幂,并将STDP规则中的相关参数近似为2的指数次幂,使得乘法可被移位再相加代替,降低实现STDP规则实现的硬件开销。

利用低硬件开销的实现方法对分段线性函数进行实现,实现的STDP系统包含移位寄存器、加法器、多路选择器结构,系统对输入值进行移位相加代替分段函数的乘法运算,用加法器进行加法运算,利用移位代替突触参数的乘法运算,低硬件开销实现STDP规则。

STDP规则中,权重的调整量与前后两个神经元激活的时间差呈函数关系,典型的STDP学习窗函数如下所示:

需要说明的是,Δw为要计算的权重修改量,Δt为神经元发出脉冲时间与接收到脉冲时间之差,

同时在传统的分段线性函数结构中,首先对所有分段代入计算,然后根据输入值所处的区间选择适用的结果。但一个输入值只会位于所有分段中的一个,所以计算值中只有一个是有意义的,这种设计使得电路结构必须付出几倍的开销。本发明的结构,先判断输入值属于哪个线性段,然后根据对应线性段的表达式计算结果。本发明的设计,将用于线性近似计算的数个电路分支减少为一个,从而减少了电路面积和计算能耗。

且降低复杂性对于硬件实现至关重要,在本发明的设计中,分段线性函数中每段的斜率都设置为2的幂或2的幂的线性组合。类似的,与乘法相关联的参数,都近似为2的幂。这样的设计使得乘法可以在单个时钟周期内,被简单的位移位操作运算代替。

实施例1

图1展示了本发明中设计的分段线性函数实现结构具体实现步骤图,具体的操作步骤包括:

操作步骤1:确定指数函数的时间窗范围,范围之外的值近似为零。

操作步骤2:将STDP规则中的指数函数近似为分段线性函数,即各分段的表达式均为Y=a*Δt+b的形式。其中a设置为2的幂或2的幂的线性组合。

操作步骤3:根据各分段的表达式,给每个分段设计对应的移位信号

操作步骤4:有Δt输入时,判断Δt所在的分段,用分段信号S表示Δt所在的分段。

操作步骤5:根据分段信号S,通过多路选择器选择相应的移位信号

操作步骤6:将Δt右移

操作步骤7:将第一次移位的结果右移

操作步骤8:利用加法器将寄存器1和2的值相加,得到a*Δt的值。

操作步骤9:利用加法器将a*Δt的值与b的值相加,得到分段线性函数的值,即指数函数的近似值。

操作步骤10:利用加法器,移位寄存器,乘法器等,完成STDP规则中与参数相关的常规运算。

在传统的结构中,假如指数函数被近似为四段,需在对四个分段都进行代入运算后,用多路选择器选择其中的一个结果。本发明的结构先判断输入值对应分段,如果该分段表达式为Δt×0.75+1.02时,则产生移位信号

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

- 一种低硬件开销的分段线性函数的硬件实现方法

- 一种捕获GPS卫星信号的低硬件开销方法及其实现