一种像素结构

文献发布时间:2023-06-19 13:45:04

技术领域

本发明涉及像素结构领域,具体涉及了一种触控屏的像素结构。

背景技术

对于TIC(Touch in Panel)的产品,即触控线(TP线)在面板上,为满足主动笔以及demux设计等一些产品的触控信号检测准确度要求,需要降低触控线的寄生电容。目前,为降低触控线的寄生电容,一般采用将触控线走线改用金属层,并走在像素电极中间,单对于MID COM架构(共通电极在像素电极下面)的像素,触控线的寄生电容仍然较大。

发明内容

针对现有技术的不足,本发明提供一种触控线寄生电容小的像素结构。

本发明的一种像素结构,采用以下技术方案:其包括:基板、数据线、扫描线、薄膜晶体管、像素电极、触控线以及共通电极;

所述基板上设有覆盖有绝缘层一;

所述数据线与所述扫描线交错在所述绝缘层上包围像素区,所述绝缘层上依次覆盖有绝缘层二和有机层;

所述像素电极设在有机层上方,具有多个狭缝;

所述触控线设在绝缘层一上,穿过所述像素区,具有一延伸方向与所述数据线的延伸方向相同;

所述薄膜晶体管包括源极、漏极和栅极,所述栅极电性连接所述扫描线,所述源极电性连接所述数据线,所述漏极电性连接所述像素电极;

所述共通电极设在有机层与像素电极之间,且与所述像素电极电性绝缘,共通电极一端电性连接所述薄膜晶体管,另一端电性连接所述触控线;

其特征在于:所述共通电极与触控线之间设有金属层,所述金属层的信号端连接在位于扫描线位置的的像素电极的上,或连接DUMMY或GND信号。

进一步,所述金属层设在有机层与共通电极之间。

进一步,所述触控线由金属成型。

进一步,所述薄膜晶体管为顶栅型薄膜晶体管。

进一步,所述绝缘层二由氮化硅成型。

进一步,所述共通电极由氧化铟锡成型。

进一步,所述像素电极由氧化铟锡成型。

与现有技术相比,本发明的有益效果如下:

1、采用金属层设在触控线与共通电极之间,减小触控线的寄生电容,提高触控信号检测准确度。

2、采用触控线的为金属走线方式,进一步减小触控线的寄生电容,提高触控信号检测准确度。

附图说明

此处所说明的附图用来提供对本申请的进一步理解,在附图中:

图1为本发明实施例一的像素俯视;

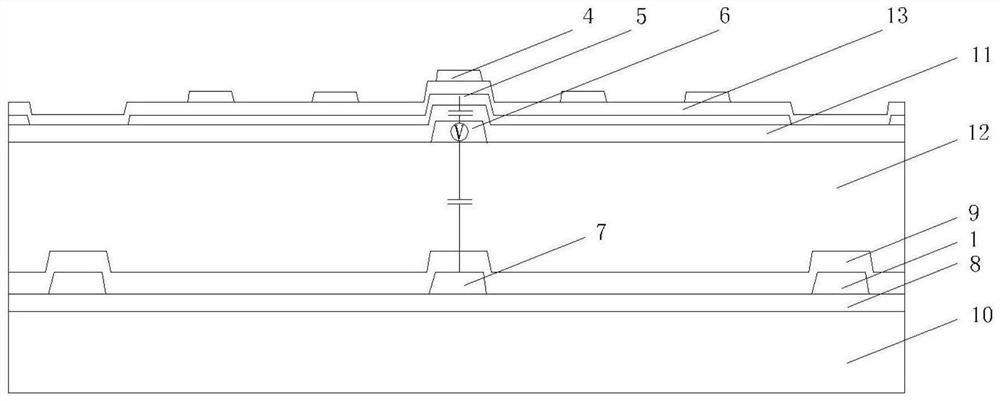

图2为图1中A-A剖视图;

图3为图1中实施例一的B-B剖视图;

图4为本发明实施例二的像素俯视;

图5为图4中A-A剖视图;

图6为图4中实施例二的B-B剖视图。

具体实施方式

参见图1-3之一所示,实施例一的一种像素结构,其包括:基板10、数据线1、扫描线2、薄膜晶体管3、像素电极4、触控线7以及共通电极5;

所述基板上设有覆盖有绝缘层一8;

所述数据线与所述扫描线交错在所述绝缘层上包围像素区,所述绝缘层上依次覆盖有绝缘层二9、有机层12、绝缘层三11和绝缘层四13;

所述像素电极4设在绝缘层四13上方,具有多个狭缝11;

所述触控线7设在绝缘层一8上,穿过所述像素区,具有一延伸方向与所述数据线1的延伸方向相同;

所述薄膜晶体3管包括源极、漏极和栅极,所述源极电性连接所述数据线1,所述漏极电性连接所述像素电极4,所述栅极电性连接所述扫描线2;

所述共通电极5设在像素电极4下方,且设在绝缘层三11和绝缘层四13之间,与所述像素电极电性绝缘,共通电极一端电性连接所述薄膜晶体管3,另一端电性连接所述触控线7;

其特征在于:所述共通电极5与触控线7之间设有金属层6,所述金属层6的信号端连接在位于扫描线2位置的的像素电极4的上。

本实施例一的进一步改进,所述金属层6设在有机层12与共通电极5之间。

本实施例一的进一步改进,所述触控线7由金属成型。

本实施例一的进一步改进,所述薄膜晶体管3为顶栅型薄膜晶体管。

本实施例一的进一步改进,所述绝缘层二9由氮化硅成型。

本实施例一的进一步改进,所述共通电极5由氧化铟锡成型。

本实施例一的进一步改进,所述像素电极4由氧化铟锡成型。

参加图4-图6所示,实施例二除金属层6的信号端连接处不同以外,其他均和实施例一相同,金属层6的信号端连接DUMMY或GND的信号端。

本发明的工作原理:

触控线的寄生电容主要来自触控线7与共通电极5之间的电容C

参见图2所示,在触控线7与共通电极5之间插入一层金属层6,会削弱触控线7与共通电极5之间的电场,使得触控线7与共通电极5之间的电容C

参见图3所示,实施例一中将金属层6的信号端连接到像素的像素电极上。此方式仿真下,实施例两条触控线7的C

参见图4所示,实施例二中将金属层6的信号端连接到DUMMY或GND信号。此方式仿真下,实施例两条触控线7的C

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。