显示装置及显示装置的制造方法

文献发布时间:2024-04-18 19:44:28

关联申请的交叉参照

本申请基于2022年3月30日提出的日本专利申请第2022-056358号主张优先权,并引用日本申请所记载的全部记载内容。

技术领域

本发明的实施方式涉及显示装置及显示装置的制造方法。

背景技术

近年来,应用有机发光二极管(OLED)作为显示元件的显示装置被实用化。该显示元件具备包含薄膜晶体管的像素电路、与像素电路连接的下电极、覆盖下电极的有机层和覆盖有机层的上电极。有机层除了发光层以外,还包含空穴传输层、电子传输层等功能层。

在制造这样的显示元件的过程中,需要抑制可靠性降低的技术。

发明内容

实施方式的目的在于提供能够抑制可靠性降低的显示装置及显示装置的制造方法。

根据一个实施方式,显示装置的制造方法包括:

准备处理基板,所述处理基板形成有第1子像素的第1下电极、第2子像素的第2下电极、及第3子像素的第3下电极,并形成有具有与所述第1下电极重叠的第1开口、与所述第2下电极重叠的第2开口、及与所述第3下电极重叠的第3开口的肋部;形成第1薄膜,所述第1薄膜包括:包含遍及所述第1子像素、所述第2子像素、及所述第3子像素的第1发光层的第1有机层;所述肋部及所述第1有机层之上的第1蚀刻阻止(etching stopper)层;和所述第1蚀刻阻止层之上的第1密封层;将所述第2子像素及所述第3子像素的所述第1薄膜除去,所述第1薄膜残留于所述第1子像素;形成第2薄膜,所述第2薄膜包括:包含遍及具有所述第1薄膜的所述第1子像素、所述第2子像素、及所述第3子像素的第2发光层的第2有机层;所述肋部及所述第2有机层之上的第2蚀刻阻止层;和所述第2蚀刻阻止层之上的第2密封层;将所述第1子像素及所述第3子像素的所述第2薄膜除去,所述第2薄膜残留于所述第2子像素;形成第3薄膜,所述第3薄膜包括:包含遍及具有所述第1薄膜的所述第1子像素、具有所述第2薄膜的所述第2子像素、及所述第3子像素的第3发光层的第3有机层;所述肋部及所述第3有机层之上的第3蚀刻阻止层;和所述第3蚀刻阻止层之上的第3密封层;将所述第1子像素及所述第2子像素的所述第3薄膜除去,所述第3薄膜残留于所述第3子像素;所述第1蚀刻阻止层的蚀刻速率小于所述第1密封层的蚀刻速率,所述第2蚀刻阻止层的蚀刻速率小于所述第2密封层的蚀刻速率,所述第3蚀刻阻止层的蚀刻速率小于所述第3密封层的蚀刻速率,所述第1蚀刻阻止层及所述第2蚀刻阻止层各自的厚度大于所述第3蚀刻阻止层的厚度。

根据一个实施方式,显示装置具备:

基板;配置在所述基板的上方的第1下电极、第2下电极、第3下电极;肋部,其具有与所述第1下电极重叠的第1开口、与所述第2下电极重叠的第2开口、及与所述第3下电极重叠的第3开口;隔壁,其具有配置在所述肋部之上的下部、和配置在所述下部之上并从所述下部的侧面突出的上部;第1有机层,其在所述第1开口中配置在所述第1下电极之上,并包含第1发光层;第1蚀刻阻止层,其配置在所述肋部及所述第1有机层之上,并与所述隔壁相接;第1密封层,其配置在所述第1蚀刻阻止层之上,并与所述隔壁相接;第2有机层,其在所述第2开口中配置在所述第2下电极之上,并包含第2发光层;第2蚀刻阻止层,其配置在所述肋部及所述第2有机层之上,并与所述隔壁相接;第2密封层,其配置在所述第2蚀刻阻止层之上,并与所述隔壁相接;第3有机层,其在所述第3开口中配置在所述第3下电极之上,并包含第3发光层;第3蚀刻阻止层,其配置在所述肋部及所述第3有机层之上,并与所述隔壁相接;和第3密封层,其配置在所述第3蚀刻阻止层之上,并与所述隔壁相接,所述第1蚀刻阻止层及所述第2蚀刻阻止层各自的厚度大于所述第3蚀刻阻止层的厚度。

根据实施方式,能够提供能够抑制可靠性的降低的显示装置及显示装置的制造方法。

附图说明

图1是示出显示装置DSP的构成例的图。

图2是示出子像素SP1、SP2、SP3的布局的一例的图。

图3是沿着图2中的A-B线的显示装置DSP的概略剖视图。

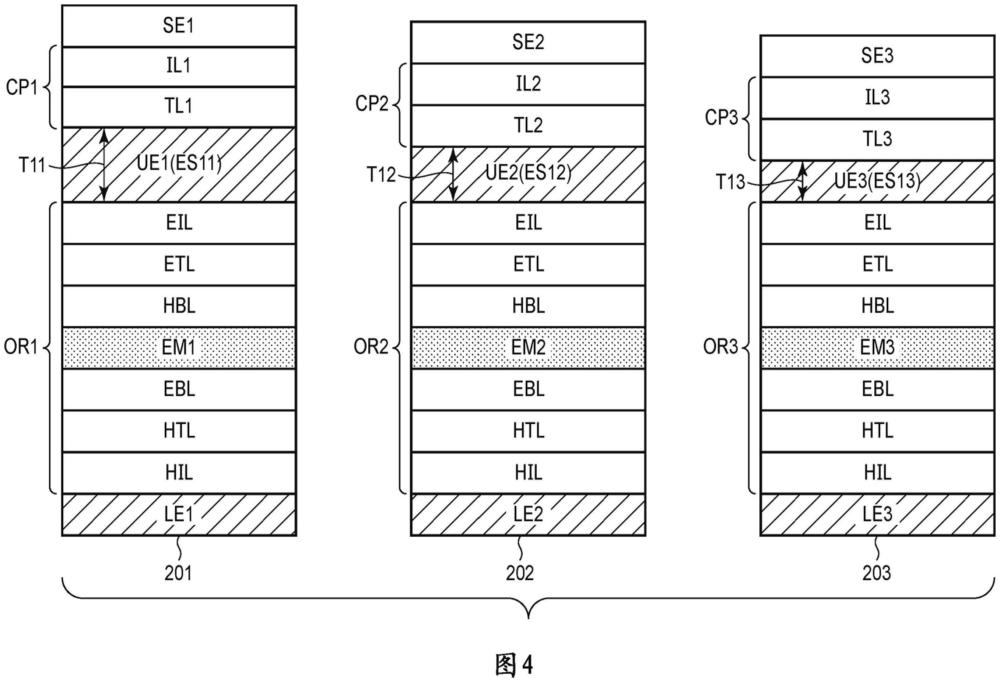

图4是示出显示元件201至203的构成的一例的图。

图5是示出图4所示的蚀刻阻止层的厚度与发光效率(efficiency)的关系的模拟结果的一例的图。

图6是示出显示元件201至203的构成的另一例的图。

图7是示出图6所示的蚀刻阻止层的厚度与发光效率的关系的模拟结果的一例的图。

图8是用于说明显示装置DSP的制造方法的一例的流程图。

图9是用于说明显示装置DSP的制造方法的图。

图10是用于说明显示装置DSP的制造方法的图。

图11是用于说明显示装置DSP的制造方法的图。

图12是用于说明子像素SP2中的第1薄膜31的除去过程的图。

图13是用于说明显示装置DSP的制造方法的图。

图14是用于说明显示装置DSP的制造方法的图。

图15是用于说明显示装置DSP的制造方法的图。

图16是用于说明显示装置DSP的制造方法的图。

图17是用于说明显示装置DSP的制造方法的图。

图18是用于说明显示装置DSP的制造方法的图。

具体实施方式

参照附图说明一个实施方式。

公开只不过是一例,本领域技术人员能够容易想到的未脱离发明主旨的适当变更当然包含在本发明范围内。另外,为了使说明更加明确,与实际方式相比,附图有时示意性表示各部分的宽度、厚度、形状等,但只不过是一例,并非限定本发明的解释。另外,在本说明书和各图中,对于与关于已出现的附图说明过的构成要素发挥相同或类似功能的构成要素,存在标注同一附图标记并适当省略重复的详细说明的情况。

需要说明的是,为了便于理解而根据需要在附图中记载有相互正交的X轴、Y轴及Z轴。将沿着X轴的方向称为第1方向,将沿着Y轴的方向称为第2方向,将沿着Z轴的方向称为第3方向。将与第3方向Z平行地观察各种要素的情形称为俯视观察。

本实施方式涉及的显示装置是具备有机发光二极管(OLED)作为显示元件的有机电致发光显示装置,能够搭载于电视、个人电脑、车载设备、平板电脑终端、智能手机、移动电话终端等。

图1是示出显示装置DSP的构成例的图。

显示装置DSP在绝缘性的基板10之上具有显示图像的显示区域DA和显示区域DA周边的周边区域SA。基板10可以是玻璃,也可以是具有挠性的树脂膜。

在本实施方式中,俯视观察的基板10的形状为长方形。但是,基板10的俯视观察的形状不限于长方形,也可以是正方形、圆形或椭圆形等其他形状。

显示区域DA具备在第1方向X及第2方向Y上以矩阵状排列的多个像素PX。像素PX包含多个子像素SP。在一例中,像素PX包含第1色的子像素SP1、第2色的子像素SP2及第3色的子像素SP3。第1色、第2色及第3色是相互不同的颜色。需要说明的是,像素PX也可以与子像素SP1、SP2、SP3一起或取代子像素SP1、SP2、SP3中的任一者而包含白色等其他颜色的子像素SP。

子像素SP具备像素电路1和由像素电路1驱动的显示元件20。像素电路1具备像素开关2、驱动晶体管3和电容器4。像素开关2及驱动晶体管3是例如由薄膜晶体管构成的开关元件。

像素开关2的栅电极与扫描线GL连接。像素开关2的源电极及漏电极中的一者与信号线SL连接,另一者与驱动晶体管3的栅电极及电容器4连接。在驱动晶体管3中,源电极及漏电极中的一者与电源线PL及电容器4连接,另一者与显示元件20的阳极连接。

需要说明的是,像素电路1的构成不限于图示的例子。例如,像素电路1也可以具备更多的薄膜晶体管及电容器。

显示元件20是作为发光元件的有机发光二极管(OLED),有时称为有机EL元件。

图2是示出子像素SP1、SP2、SP3的布局的一例的图。

在图2的例子中,子像素SP1与子像素SP2在第2方向Y上排列。此外,子像素SP1、SP2分别与子像素SP3在第1方向X上排列。

在子像素SP1、SP2、SP3为这种布局的情况下,在显示区域DA中形成有子像素SP1、SP2在第2方向Y上交替配置的列和多个子像素SP3在第2方向Y上配置的列。这些列在第1方向X上交替排列。

需要说明的是,子像素SP1、SP2、SP3的布局不限于图2的例子。作为另一例,各像素PX中的子像素SP1、SP2、SP3也可以在第1方向X上依次排列。

在显示区域DA中配置有肋部5及隔壁6。肋部5在子像素SP1、SP2、SP3处分别具有开口AP1、AP2、AP3。

隔壁6在俯视观察时与肋部5重叠。隔壁6具有沿第1方向X延伸的多个第1隔壁6x和沿第2方向Y延伸的多个第2隔壁6y。多个第1隔壁6x分别配置于在第2方向Y上相邻的开口AP1、AP2之间、及在第2方向Y上相邻的两个开口AP3之间。第2隔壁6y分别配置于在第1方向X上相邻的开口AP1、AP3之间、及在第1方向X上相邻的开口AP2、AP3之间。

在图2的例子中,第1隔壁6x与第2隔壁6y相互连接。由此,隔壁6作为整体形成为包围开口AP1、AP2、AP3的格子状。隔壁6也可以与肋部5同样地在子像素SP1、SP2、SP3中具有开口。

子像素SP1、SP2、SP3分别具备显示元件201、202、203作为显示元件20。

子像素SP1具备分别与开口AP1重叠的下电极LE1、上电极UE1及有机层OR1。子像素SP2具备分别与开口AP2重叠的下电极LE2、上电极UE2及有机层OR2。子像素SP3具备分别与开口AP3重叠的下电极LE3、上电极UE3及有机层OR3。

在图2的例子中,下电极LE1、LE2、LE3的外形以虚线表示,有机层OR1、OR2、OR3及上电极UE1、UE2、UE3的外形以单点划线表示。下电极LE1、LE2、LE3各自的周缘部与肋部5重叠。上电极UE1的外形与有机层OR1的外形大致一致,上电极UE1及有机层OR1各自的周缘部与隔壁6重叠。上电极UE2的外形与有机层OR2的外形大致一致,上电极UE2及有机层OR2各自的周缘部与隔壁6重叠。上电极UE3的外形与有机层OR3的外形大致一致,上电极UE3及有机层OR3各自的周缘部与隔壁6重叠。

下电极LE1、上电极UE1及有机层OR1构成子像素SP1的显示元件201。下电极LE2、上电极UE2及有机层OR2构成子像素SP2的显示元件202。下电极LE3、上电极UE3及有机层OR3构成子像素SP3的显示元件203。

下电极LE1、LE2、LE3例如相当于显示元件的阳极。上电极UE1、UE2、UE3相当于显示元件的阴极或公共电极。

下电极LE1通过接触孔CH1与子像素SP1的像素电路1(参见图1)连接。下电极LE2通过接触孔CH2与子像素SP2的像素电路1连接。下电极LE3通过接触孔CH3与子像素SP3的像素电路1连接。

在图2的例子中,开口AP3的面积大于开口AP2的面积、开口AP2的面积大于开口AP1的面积。换言之,从开口AP3露出的下电极LE3的面积大于从开口AP2露出的下电极LE2的面积,从开口AP2露出的下电极LE2的面积大于从开口AP1露出的下电极LE1的面积。

图3是沿着图2中的A-B线的显示装置DSP的概略剖视图。

在上述基板10之上配置有电路层11。电路层11包含图1所示的像素电路1、扫描线GL、信号线SL及电源线PL等各种电路、布线。电路层11由绝缘层12覆盖。绝缘层12作为使由电路层11产生的凹凸平坦化的平坦化膜发挥功能。

下电极LE1、LE2、LE3配置在绝缘层12之上。肋部5配置在绝缘层12及下电极LE1、LE2、LE3之上。下电极LE1、LE2、LE3的端部由肋部5覆盖。也就是说,下电极LE1、LE2、LE3的端部配置在绝缘层12与肋部5之间。在下电极LE1、LE2、LE3中的相互邻接的下电极之间,绝缘层12由肋部5覆盖。

隔壁6包含配置在肋部5之上的下部(杆部)61和配置在下部61之上的上部(伞部)62。在图的右侧示出的隔壁6的下部61位于开口AP1与开口AP2之间。在图的左侧示出的隔壁6的下部61位于开口AP2与开口AP3之间。上部62具有比下部61大的宽度。由此,在图3中,上部62的两端部比下部61的侧面突出。这样的隔壁6的形状也可以称为悬臂状。上部62中的比下部61突出的部分有时简称为突出部。

图2所示的有机层OR1如图3所示,包含相互分离的第1部分OR1a及第2部分OR1b。第1部分OR1a通过开口AP1与下电极LE1接触,覆盖下电极LE1,并与肋部5的一部分重叠。第2部分OR1b配置在上部62之上。

另外,图2所示的上电极UE1如图3所示,包含相互分离的第1部分UE1a及第2部分UE1b。第1部分UE1a与下电极LE1相对,并配置在第1部分OR1a之上。此外,第1部分UE1a与下部61的侧面接触。第2部分UE1b位于隔壁6的上方,并配置在第2部分OR1b之上。

第1部分OR1a及第1部分UE1a与上部62相比位于下方。

图2所示的有机层OR2如图3所示,包含相互分离的第1部分OR2a及第2部分OR2b。第1部分OR2a通过开口AP2与下电极LE2接触,覆盖下电极LE2,并与肋部5的一部分重叠。第2部分OR2b配置在上部62之上。

另外,如图3所示,图2所示的上电极UE2包含相互分离的第1部分UE2a及第2部分UE2b。第1部分UE2a与下电极LE2相对,并配置在第1部分OR2a之上。此外,第1部分UE2a与下部61的侧面接触。第2部分UE2b位于隔壁6的上方,并配置在第2部分OR2b之上。

第1部分OR2a及第1部分UE2a与上部62相比位于下方。

如图3所示,图2所示的有机层OR3包含相互分离的第1部分OR3a及第2部分OR3b。第1部分OR3a通过开口AP3与下电极LE3接触,覆盖下电极LE3,并与肋部5的一部分重叠。第2部分OR3b配置在上部62之上。

另外,如图3所示,图2所示的上电极UE3包含相互分离的第1部分UE3a及第2部分UE3b。第1部分UE3a与下电极LE3相对,并配置在第1部分OR3a之上。此外,第1部分UE3a与下部61的侧面接触。第2部分UE3b位于隔壁6的上方,并配置在第2部分OR3b之上。

第1部分OR3a及第1部分UE3a与上部62相比位于下方。

在图3所示的例子中,子像素SP1、SP2、SP3包含用于调整有机层OR1、OR2、OR3的发光层发出的光的光学特性的盖层(光学调整层)CP1、CP2、CP3。

盖层CP1包含相互分离的第1部分CP1a和第2部分CP1b。第1部分CP1a位于开口AP1,与上部62相比位于下方,并配置在第1部分UE1a之上。第2部分CP1b位于隔壁6的上方,并配置在第2部分UE1b之上。

盖层CP2包含相互分离的第1部分CP2a和第2部分CP2b。第1部分CP2a位于开口AP2,与上部62相比位于下方,并配置在第1部分UE2a之上。第2部分CP2b位于隔壁6的上方,并配置在第2部分UE2b之上。

盖层CP3包含相互分离的第1部分CP3a和第2部分CP3b。第1部分CP3a位于开口AP3,与上部62相比位于下方,并配置在第1部分UE3a之上。第2部分CP3b位于隔壁6的上方,并配置在第2部分UE3b之上。

在子像素SP1、SP2、SP3中分别配置有密封层SE1、SE2、SE3。

密封层SE1与第1部分CP1a、隔壁6的下部61及上部62、以及第2部分CP1b相接,并连续覆盖子像素SP1的各部件。需要说明的是,密封层SE1可能有在隔壁6的上部62的下方(突出部621的下方)具有空隙的情况,但此处省略图示。

密封层SE2与第1部分CP2a、隔壁6的下部61及上部62、以及第2部分CP2b相接,并连续覆盖子像素SP2的各部件。需要说明的是,密封层SE2可能有在隔壁6的上部62的下方(突出部622的下方)具有空隙的情况,但此处省略图示。

密封层SE3与第1部分CP3a、隔壁6的下部61及上部62、以及第2部分CP3b相接,并连续覆盖子像素SP3的各部件。需要说明的是,密封层SE3可能有在隔壁6的上部62的下方(突出部623的下方)具有空隙的情况,但此处省略图示。

密封层SE1、SE2、SE3由保护层13覆盖。

在图3的例子中,在子像素SP1、SP2之间的隔壁6上,有机层OR1的第2部分OR1b与有机层OR2的第2部分OR2b分离,上电极UE1的第2部分UE1b与上电极UE2的第2部分UE2b分离,盖层CP1的第2部分CP1b与盖层CP2的第2部分CP2b分离,密封层SE1与密封层SE2分离。保护层13分别配置在第2部分OR1b与第2部分OR2b之间、第2部分UE1b与第2部分UE2b之间、第2部分CP1b与第2部分CP2b之间、及密封层SE1与密封层SE2之间。

另外,在子像素SP2、SP3之间的隔壁6上,有机层OR2的第2部分OR2b与有机层OR3的第2部分OR3b分离,上电极UE2的第2部分UE2b与上电极UE3的第2部分UE3b分离,盖层CP2的第2部分CP2b与盖层CP3的第2部分CP3b分离,密封层SE2与密封层SE3分离。保护层13分别配置在第2部分OR2b与第2部分OR3b之间、第2部分UE2b与第2部分UE3b之间、第2部分CP2b与第2部分CP3b之间、及密封层SE2与密封层SE3之间。

绝缘层12是有机绝缘层。肋部5及密封层SE1、SE2、SE3是无机绝缘层。

密封层SE1、SE2、SE3例如由相同的无机绝缘材料形成。

肋部5由作为无机绝缘材料的一例的硅氮化物(SiNx)形成。需要说明的是,肋部5也可以形成为作为其他无机绝缘材料的硅氧化物(SiOx)、硅氧氮化物(SiON)或氧化铝(Al

密封层SE1、SE2、SE3由作为无机绝缘材料的一例的硅氮化物(SiNx)形成。需要说明的是,密封层SE1、SE2、SE3也可以形成为作为其他无机绝缘材料的硅氧化物(SiOx)、硅氧氮化物(SiON)或氧化铝(Al

隔壁6的下部61由导电材料形成,与各上电极的第1部分UE1a、UE2a、UE3a电连接。隔壁6的下部61及上部62也可以均具有导电性。

肋部5的厚度与隔壁6、绝缘层12的厚度相比足够小。在一例中,肋部5的厚度为200nm以上且400nm以下。

密封层SE1的厚度、密封层SE2的厚度及密封层SE3的厚度大致相同。

隔壁6的下部61的厚度(从肋部5的上表面到上部62的下表面为止的厚度)大于肋部5的厚度。

下电极LE1、LE2、LE3既可以由ITO等透明导电材料形成,也可以具有银(Ag)等金属材料与透明导电材料的层叠构造。上电极UE1、UE2、UE3由例如镁和银的合金(MgAg)等金属材料形成。上电极UE1、UE2、UE3也可以由ITO等透明导电材料形成。

在与上电极UE1、UE2、UE3的电位相比下电极LE1、LE2、LE3的电位相对高的情况下,下电极LE1、LE2、LE3相当于阳极,上电极UE1、UE2、UE3相当于阴极。另外,在与下电极LE1、LE2、LE3的电位相比上电极UE1、UE2、UE3的电位相对高的情况下,上电极UE1、UE2、UE3相当于阳极,下电极LE1、LE2、LE3相当于阴极。

有机层OR1、OR2、OR3包含多个功能层。另外,有机层OR1的第1部分OR1a及第2部分OR1b包含由相同材料形成的发光层EM1。有机层OR2的第1部分OR2a及第2部分OR2b包含由相同材料形成的包含发光层EM2。发光层EM2由与发光层EM1不同的材料形成。有机层OR3的第1部分OR3a及第2部分OR3b包含由相同材料形成的发光层EM3。发光层EM3由与发光层EM1及EM2不同的材料形成。

形成发光层EM1的材料、形成发光层EM2的材料及形成发光层EM3的材料是发出相互不同的波长区域的光的材料。

即,发光层EM1由发出第1波长区域的光的材料形成。另外,发光层EM2由发出与第1波长区域不同的第2波长区域的光的材料形成。另外,发光层EM3由发出与第1波长区域及第2波长区域不同的第3波长区域的光的材料形成。

盖层CP1、CP2、CP3例如由透明薄膜的多层体形成。多层体也可以包含由无机材料形成的薄膜及由有机材料形成的薄膜作为薄膜。另外,上述多个薄膜具有相互不同的折射率。构成多层体的薄膜的材料与上电极UE1、UE2、UE3的材料不同,另外,也与密封层SE1、SE2、SE3的材料不同。需要说明的是,盖层CP1、CP2、CP3也可以省略。

保护层13是透明的有机绝缘层。密封层14是透明的无机绝缘层,配置在保护层13之上。密封层14例如由硅氮化物(SiNx)形成。保护层(overcoat layer)15是透明的有机绝缘层,配置在密封层14之上。

对隔壁6供给公共电压。该公共电压被分别供给至与下部61的侧面接触的各上电极的第1部分UE1a、UE2a、UE3a。下电极LE1、LE2、LE3经由子像素SP1、SP2、SP3各自具有的像素电路1被供给像素电压。

若在下电极LE1与上电极UE1之间形成电位差,则有机层OR1中的第1部分OR1a的发光层EM1发出第1波长区域的光。若在下电极LE2与上电极UE2之间形成电位差,则有机层OR2中的第1部分OR2a的发光层EM2发出第2波长区域的光。若在下电极LE3与上电极UE3之间形成电位差,则有机层OR3中的第1部分OR3a的发光层EM3发出第3波长区域的光。

图4是示出显示元件201至203的构成的一例的图。需要说明的是,在此,以下电极相当于阳极、上电极相当于阴极的情况为例进行说明。

显示元件201在下电极LE1与上电极UE1之间包含有机层OR1。

在有机层OR1中,空穴注入层HIL、空穴传输层HTL、电子阻挡层EBL位于下电极LE1与发光层EM1之间。空穴注入层HIL配置在下电极LE1之上,空穴传输层HTL配置在空穴注入层HIL之上,电子阻挡层EBL配置在空穴传输层HTL之上,发光层EM1配置在电子阻挡层EBL之上。

另外,在有机层OR1中,空穴阻挡层HBL、电子传输层ETL、电子注入层EIL位于发光层EM1与上电极UE1之间。空穴阻挡层HBL配置在发光层EM1之上,电子传输层ETL配置在空穴阻挡层HBL之上,电子注入层EIL配置在电子传输层ETL之上,上电极UE1配置在电子注入层EIL之上。

需要说明的是,有机层OR1除了上述功能层以外,既可以根据需要包含载流子发生层等其他功能层,也可以省略上述功能层中的至少一个。

盖层CP1包含透明层TL1及无机层IL1。透明层TL1配置在上电极UE1之上。无机层IL1配置在透明层TL1之上。密封层SE1配置在无机层IL1之上。

透明层TL1是例如由有机材料形成的有机层,另外,是具有比上电极UE1大的折射率的高折射率层。无机层IL1是例如由氟化锂(LiF)或硅氧化物(SiO)形成的透明薄膜,是具有比透明层TL1小的折射率的低折射率层。

需要说明的是,在图4所示的例子中,盖层CP1是透明层TL1与无机层IL1的两层层叠体,但也可以是三层以上的层叠体。在盖层CP1中,无机层IL1位于最上层,并由密封层SE1覆盖。

就显示元件202而言,下电极LE2与上电极UE2之间的有机层OR2取代发光层EM1而包含发光层EM2,除了这一点以外,与显示元件201同样地构成。

盖层CP2的透明层TL2配置在上电极UE2之上,盖层CP2的无机层IL2由密封层SE2覆盖。

就显示元件203而言,下电极LE3与上电极UE3之间的有机层OR3取代发光层EM1而包含发光层EM3,除了这一点以外,与显示元件201同样地构成。

盖层CP3的透明层TL3配置在上电极UE3之上,盖层CP3的无机层IL3由密封层SE3覆盖。

图4所示的空穴注入层HIL、空穴传输层HTL、电子阻挡层EBL、空穴阻挡层HBL、电子传输层ETL、电子注入层EIL等各功能层共同地设置于显示元件201至203,按显示元件201至203分离,另外,按显示元件201至203而独立地形成。上述功能层各自的厚度有可能在每个显示元件201至203中不同。

另外,在着眼于上述多个功能层中的一个功能层时,可能存在显示元件201至203中的一个显示元件的功能层由与其他两个显示元件的功能层不同的材料形成的情况,也可能存在显示元件201至203的全部功能层由相互不同的材料形成的情况。

另外,可能存在显示元件201至203中的一个显示元件的层构成与其他两个显示元件的层构成不同的情况,与可能存在显示元件201至203的全部层构成相互不同的情况。例如,在着眼于一个功能层时,可能存在显示元件201至203中的一个显示元件未包含该功能层的情况,也可能存在仅显示元件201至203中的一个显示元件包含该功能层的情况。另外,在着眼于一个功能层时,可能存在在显示元件201至203中的一个显示元件中该功能层经多层化的情况等。

透明层TL1至TL3相互分离,分别独立地形成。因此,可能存在透明层TL1至TL3全部由相同材料形成的情况,也可能存在透明层TL1至TL3中的一个透明层由与其他两个透明层不同的材料形成的情况,或存在透明层TL1至TL3全部由相互不同的材料形成的情况。另外,透明层TL1至TL3各自的厚度可能存在全部相同的情况,也可能存在相互不同的情况。

无机层IL1至IL3相互分离,分别独立地形成。因此,可能存在无机层IL1至IL3全部由相同材料形成的情况,也可能存在无机层IL1至IL3中的一个无机层由与其他两个无机层不同的材料形成的情况在,或无机层IL1至IL3全部由相互不同的材料形成的情况。另外,无机层IL1至IL3各自的厚度可能存在全部相同的情况,也可能存在相互不同的情况。

另外,可能存在盖层CP1至CP3的全部层构成相同的情况,也可能存在盖层CP1至CP3中的一个盖层的层构成与其他两个盖层的层构成不同的情况,或盖层CP1至CP3的全部层构成相互不同的情况。

在图4所示的例子中,在显示元件201中,上电极UE1作为对密封层SE1进行干式蚀刻时的蚀刻阻止层ES11发挥功能。在显示元件202中,上电极UE2作为对密封层SE2进行干式蚀刻时的蚀刻阻止层ES12发挥功能。在显示元件203中,上电极UE3作为对密封层SE3进行干式蚀刻时的蚀刻阻止层ES13发挥功能。

将在同一条件下对蚀刻阻止层ES11和密封层SE1进行干式蚀刻时的蚀刻速率进行比较,蚀刻阻止层ES11(或上电极UE1)的蚀刻速率小于密封层SE1的蚀刻速率。

例如,针对在蚀刻阻止层ES11之上层叠密封层SE1而成的层叠体进行干式蚀刻的情况下,密封层SE1被除去,另一方面,能够在蚀刻阻止层ES11中停止蚀刻的进行。

同样地,蚀刻阻止层ES12(或上电极UE2)的蚀刻速率小于密封层SE2的蚀刻速率。另外,蚀刻阻止层ES13(或上电极UE3)的蚀刻速率小于密封层SE3的蚀刻速率。

蚀刻阻止层ES11至ES13由与肋部5不同的材料形成,另外,由与密封层SE1、SE2、SE3不同的材料形成。例如,肋部5及密封层SE1、SE2、SE3由硅氮化物形成,与此相对,蚀刻阻止层ES11至ES13由作为与硅氮化物相比对干式蚀刻具有高耐性的材料的镁和银的合金形成。

在图4所示的例子中,蚀刻阻止层ES11(或上电极UE1)的厚度T11大于蚀刻阻止层ES13(或上电极UE3)的厚度T13(T11>T13)。蚀刻阻止层ES12(或上电极UE2)的厚度T12大于蚀刻阻止层ES13(或上电极UE3)的厚度T13(T12>T13)。另外,在一例中,厚度T11大于T12(T11>T12)。需要说明的是,厚度T12也可以与厚度T11相同(T12≒T11),也可能存在厚度T11小于厚度T12的情况(T11<T12)。

蚀刻阻止层ES11至ES13各自的厚度与显示元件201至203的颜色的关系如下。

具有最薄的蚀刻阻止层ES13的显示元件203以作为第3波长区域发出蓝色波长区域的光的方式构成。也就是说,发光层EM3由发出蓝色波长区域的光的材料形成。

具有厚度T11的蚀刻阻止层ES11的显示元件201以作为第1波长区域发出红色波长区域的光的方式构成。发光层EM1由发出红色波长区域的光的材料形成。

具有厚度T12的蚀刻阻止层ES12的显示元件202以作为第2波长区域发出绿色波长区域的光的方式构成。发光层EM2由发出绿色波长区域的光的材料形成。

或者,也可能存在显示元件201以作为第1波长区域发出绿色波长区域的光的方式构成,显示元件202以作为第2波长区域发出红色波长区域的光的方式构成的情况。此时,发光层EM1由发出绿色波长区域的光的材料形成,发光层EM2由发出红色波长区域的光的材料形成。

图5是示出图4所示的蚀刻阻止层的厚度与发光效率的关系的模拟结果的一例的图。

在图5所示的各图中,横轴是蚀刻阻止层的厚度,纵轴是发光效率。此处的发光效率定义为显示元件发出的光的亮度(cd/m

图5的上部示出显示元件201中的蚀刻阻止层ES11的厚度T11与发光效率的关系的模拟结果。

图5的中部示出显示元件202中的蚀刻阻止层ES12的厚度T12与发光效率的关系的模拟结果。

图5的下部示出显示元件203中的蚀刻阻止层ES13的厚度T13与发光效率的关系的模拟结果。

在CIE表色系的色度图中,显示元件201发出的红色波长区域的光中的、应考虑发光效率的光的色度坐标的一例为(x=0.69,y=0.31)。另外,显示元件202发出的绿色波长区域的光中的、应考虑发光效率的光的色度坐标的一例为(x=0.25,y=0.72)。另外,显示元件203发出的蓝色波长区域的光中的、应考虑发光效率的光的色度坐标的一例为(x=0.14,y=0.05)。

因而,在此处的模拟中,显示元件201至203各自基于上述色度坐标的光的亮度来计算发光效率。

关于显示元件201确认到,随着厚度T11增加而发光效率上升,在厚度T11为25nm~28nm范围内发光效率达到峰值,然后,随着厚度T11增加至40nm左右而发光效率降低。

关于显示元件202确认到,随着厚度T12增加而发光效率上升,在厚度T12为25nm~30nm范围内发光效率达到峰值,然后,随着厚度T12增加至40nm左右而发光效率降低。

关于显示元件203确认到,随着厚度T13增加而发光效率上升,在厚度T13为15nm~18nm范围内发光效率达到峰值,然后,随着厚度T13增加至40nm左右而发光效率降低。

基于上述模拟结果,厚度T11至T13设定为发光效率达到峰值或其附近。并且,厚度T11及厚度T12设定得大于厚度T13。

蚀刻阻止层ES11至ES13相互分离,分别独立地形成。因此,蚀刻阻止层ES11至ES13各自的厚度能够自如设定,能够容易地优化。

图6是示出显示元件201至203的构成的另一例的图。图6所示的例子与无机层作为蚀刻阻止层发挥功能的例子相当。

即,在显示元件201中,无机层IL1作为对密封层SE1进行干式蚀刻时的蚀刻阻止层ES21发挥功能。在显示元件202中,无机层IL2作为对密封层SE2进行干式蚀刻时的蚀刻阻止层ES22发挥功能。在显示元件203中,无机层IL3作为对密封层SE3进行干式蚀刻时的蚀刻阻止层ES23发挥功能。

若将在同一条件下对蚀刻阻止层ES21与密封层SE1进行干式蚀刻时的蚀刻速率进行比较,则蚀刻阻止层ES21(或无机层IL1)的蚀刻速率小于密封层SE1的蚀刻速率。

同样地,蚀刻阻止层ES22(或无机层IL2)的蚀刻速率小于密封层SE2的蚀刻速率。另外,蚀刻阻止层ES23(或无机层IL3)的蚀刻速率小于密封层SE3的蚀刻速率。

蚀刻阻止层ES21至ES23由与肋部5不同的材料形成,另外,由与密封层SE1、SE2、SE3不同的材料形成。例如,肋部5及密封层SE1、SE2、SE3由硅氮化物形成,与此相对,蚀刻阻止层ES21至ES23由作为与硅氮化物相比对干式蚀刻具有高耐性的材料的氟化锂或硅氧化物形成。

在图6所示的例子中,蚀刻阻止层ES21(或无机层IL1)的厚度T21大于蚀刻阻止层ES23(或无机层IL3)的厚度T23(T21>T23)。蚀刻阻止层ES22(或无机层IL2)的厚度T22大于蚀刻阻止层ES23(或无机层IL3)的厚度T23(T22>T23)。另外,在一例中,厚度T21大于厚度T22(T21>T22)。需要说明的是,厚度T22也可以与厚度T21相同(T22≒T21),有可能存在厚度T21小于厚度T22的情况(T21<T22)。

蚀刻阻止层ES21至ES23各自的厚度与显示元件201至203的色的关系如下。

具有最薄蚀刻阻止层ES23的显示元件203以作为第3波长区域发出蓝色波长区域的光的方式构成。也就是说,发光层EM3由发出蓝色波长区域的光的材料形成。

具有厚度T21的蚀刻阻止层ES21的显示元件201以作为第1波长区域发出红色波长区域的光的方式构成。发光层EM1由发出红色波长区域的光的材料形成。

具有厚度T22的蚀刻阻止层ES22的显示元件202以作为第2波长区域发出绿色波长区域的光的方式构成。发光层EM2由发出绿色波长区域的光的材料形成。

或者,有可能存在显示元件201以作为第1波长区域发出绿色波长区域的光的方式构成,显示元件202以作为第2波长区域发出红色波长区域的光的情况的方式构成。此时,发光层EM1由发出绿色波长区域的光的材料形成,发光层EM2由发出红色波长区域的光的材料形成。

图7是示出图6所示的蚀刻阻止层的厚度与发光效率的关系的模拟结果的一例的图。

在图7所示的各图中,横轴是蚀刻阻止层的厚度,纵轴是发光效率。此处的发光效率的定义如参见图5所说明的那样。需要说明的是,纵轴的发光效率是将蚀刻阻止层的厚度为80nm的情况下的发光效率标准化为1的值。

图7的上部示出显示元件201中的蚀刻阻止层ES21的厚度T21与发光效率的关系的模拟结果。在此处的模拟中,基于显示元件201发出的红色波长区域的光中的、色度坐标(x=0.69,y=0.31)的光的亮度计算发光效率。

图7的中部示出显示元件202中的蚀刻阻止层ES22的厚度T22与发光效率的关系的模拟结果。在此处的模拟中,基于显示元件202发出的绿色波长区域的光中的、色度坐标(x=0.25,y=0.72)的光的亮度计算发光效率。

图7的下部示出显示元件203中的蚀刻阻止层ES23的厚度T23与发光效率的关系的模拟结果。在此处的模拟中,基于显示元件203发出的蓝色波长区域的光中的、色度坐标(x=0.14,y=0.05)的光的亮度计算发光效率。

关于显示元件201,确认到随着厚度T21增加而发光效率上升,在厚度T21约为140nm时发光效率达到峰值,然后,随着厚度T21增加至250nm左右而发光效率降低。

关于显示元件202,确认到随着厚度T22增加而发光效率上升,在厚度T22约为120nm时发光效率达到峰值,然后,随着厚度T22增加至250nm左右而发光效率降低。

关于显示元件203,确认到随着厚度T23增加而发光效率上升,在厚度T23约为100nm时发光效率达到峰值,然后,随着厚度T23增加至250nm左右而发光效率降低。

基于上述模拟结果,厚度T21至T23设定为发光效率达到峰值或其附近。并且,厚度T21及厚度T22设定为大于厚度T23。另外,厚度T21设定为大于厚度T22。

蚀刻阻止层ES21至ES23相互分离,分别独立地形成。因此,蚀刻阻止层ES21至ES23各自的厚度能够自如地设定,且能够容易地优化。

在参照图4及图5说明的例子中,上电极UE1至UE3作为蚀刻阻止层发挥功能,在参照图6及图7说明的例子中,盖层的无机层IL1至IL3作为蚀刻阻止层发挥作用,但也可以将其组合。

也就是说,也可以构成为,在显示元件201中,上电极UE1及无机层IL1中的至少一者作为蚀刻阻止层发挥功能,在显示元件202中,上电极UE2及无机层IL2中的至少一者作为蚀刻阻止层发挥功能,在显示元件203中,上电极UE3及无机层IL3中的至少一者作为蚀刻阻止层发挥功能。

接下来,说明显示装置DSP的制造方法的一例。

图8是用于说明显示装置DSP的制造方法的一例的流程图。

此处所示的制造方法大致包括:准备具有子像素SP1、子像素SP2及子像素SP3的处理基板SUB的工序(步骤ST1);形成子像素SP1的显示元件201的工序(步骤ST2);形成子像素SP2的显示元件202的工序(步骤ST3);和形成子像素SP3的显示元件203的工序(步骤ST4)。

关于形成显示元件201、202、203的工序的顺序,期望的是蚀刻阻止层越厚的显示元件越先形成。换言之,期望的是蚀刻阻止层越薄的显示元件越后形成。

参照图4至图7来说明,显示元件203的蚀刻阻止层(ES13或ES23)比显示元件201的蚀刻阻止层(ES11或ES21)薄,比显示元件202的蚀刻阻止层(ES12或ES22)薄。因此,在形成显示元件203之前形成显示元件201及202。另外,在显示元件202的蚀刻阻止层(ES12或ES22)比显示元件201的蚀刻阻止层(ES11或ES21)薄的情况下,在形成显示元件202之前形成显示元件201。因此,按照图8所示的顺序形成显示元件201至203。

在步骤ST1中,首先,准备在基板10之上形成有子像素SP1的下电极LE1、子像素SP2的下电极LE2、子像素SP3的下电极LE3、肋部5、及隔壁6的处理基板SUB。详细情况如后所述。

在步骤ST2中,首先,在处理基板SUB上形成包含发光层EM1的第1薄膜31(步骤ST21)。然后,在第1薄膜31之上形成图案化为规定形状的第1抗蚀剂41(步骤ST22)。然后,通过以第1抗蚀剂41为掩模的蚀刻将第1薄膜31的一部分除去(步骤ST23)。然后,将第1抗蚀剂41除去(步骤ST24)。由此形成子像素SP1。子像素SP1具备具有规定形状的第1薄膜31的显示元件201。

在步骤ST3中,首先,在处理基板SUB上形成包含发光层EM2的第2薄膜32(步骤ST31)。然后,在第2薄膜32之上形成图案化为规定形状的第2抗蚀剂42(步骤ST32)。然后,通过以第2抗蚀剂42为掩模的蚀刻将第2薄膜32的一部分除去(步骤ST33)。然后将第2抗蚀剂42除去(步骤ST34)。由此形成子像素SP2。子像素SP2具备具有规定形状的第2薄膜32的显示元件202。

在步骤ST4中,首先,在处理基板SUB上形成包含发光层EM3的第3薄膜33(步骤ST41)。然后,在第3薄膜33之上形成图案化为规定形状的第3抗蚀剂43(步骤ST42)。然后,通过以第3抗蚀剂43为掩模的蚀刻将第3薄膜33的一部分除去(步骤ST43)。然后,将第3抗蚀剂43除去(步骤ST44)。由此形成子像素SP3。子像素SP3具备具有规定形状的第3薄膜33的显示元件203。

以下,参照图9至图18,以上电极作为蚀刻阻止层发挥功能的情况为例来说明步骤ST1及步骤ST4。

首先,在步骤ST1中,如图9的上部所示,准备处理基板SUB。准备处理基板SUB的工序包括:在基板10之上形成电路层11的工序;在电路层11之上形成绝缘层12的工序;在绝缘层12之上形成子像素SP1的下电极LE1、子像素SP2的下电极LE2、子像素SP3的下电极LE3的工序;形成具有与下电极LE1、LE2、LE3的各自重叠的开口AP1、AP2、AP3的肋部5的工序;和形成包含配置在肋部5之上的下部61和配置在下部61之上并从下部61的侧面突出的上部62的隔壁6的工序。图9至图11、图13至图18所示的剖面与例如沿着图2中的A-B线的剖面相当。需要说明的是,在图10、图11、图13至图18中,省略与绝缘层12相比为下层的基板10及电路层11的图示。

接下来,在步骤ST21中,如图9的下部所示,遍及子像素SP1、子像素SP2及子像素SP3而形成第1薄膜31。形成第1薄膜31的工序包括:在处理基板SUB之上形成包含发出红色波长区域的光的发光层EM1的有机层OR1的工序;在有机层OR1之上作为蚀刻阻止层形成上电极UE1的工序;在上电极UE1之上形成盖层CP1的工序;和在盖层CP1之上形成密封层SE1的工序。

有机层OR1分别形成在下电极LE1、下电极LE2及下电极LE3之上,并且形成在隔壁6之上。有机层OR1中的形成在上部62之上的部分与形成在各下电极之上的部分分离。

在下电极LE1、下电极LE2及下电极LE3的正上方,上电极UE1分别形成在有机层OR1之上,覆盖肋部5,并与隔壁6的下部61相接。另外,在上部62的正上方,上电极UE1也形成在有机层OR1之上。上电极UE1中的在上部62的正上方形成的部分与在各下电极的正上方形成的部分分离。上电极UE1具有厚度T11。

盖层CP1包含省略图示的透明层TL1及无机层IL1。在下电极LE1、下电极LE2及下电极LE3的正上方,盖层CP1分别形成在上电极UE1之上,并且在上部62的正上方也形成在上电极UE1之上。盖层CP1中的在上部62的正上方形成的部分与在各下电极的正上方形成的部分分离。

密封层SE1以覆盖盖层CP1及隔壁6的方式形成。也就是说,在下电极LE1、下电极LE2、及下电极LE3的正上方,密封层SE1分别形成在盖层CP1之上,并且在上部62的正上方也形成在盖层CP1之上。在密封层SE1中,在上部62的正上方形成的部分与在各下电极的正上方形成的部分相连。

接下来,在步骤ST22中,如图10的上部所示,遍及密封层SE1之上的整个面而涂布第1抗蚀剂41。然后,如图10的下部所示,将第1抗蚀剂41图案化。第1抗蚀剂41覆盖子像素SP1的第1薄膜31,使子像素SP2及子像素SP3的第1薄膜31露出。也就是说,第1抗蚀剂41配置在下电极LE1的正上方。另外,第1抗蚀剂41从子像素SP1向隔壁6的上方延伸。在子像素SP1与子像素SP2之间的隔壁6上,第1抗蚀剂41配置在子像素SP1侧(图的右侧),在子像素SP2侧(图的左侧)使密封层SE1露出。另外,第1抗蚀剂41在子像素SP2及子像素SP3中使密封层SE1露出。

接下来,在步骤ST23中,如图11所示,以第1抗蚀剂41为掩模进行蚀刻,将从第1抗蚀剂41露出的子像素SP2及子像素SP3的第1薄膜31除去,第1薄膜31残留于子像素SP1。由此,在子像素SP2中,下电极LE2露出,另外,包围下电极LE2的肋部5露出。另外,在子像素SP3中,下电极LE3露出,另外,包围下电极LE3的肋部5露出。另外,在子像素SP1与子像素SP2之间的隔壁6中,子像素SP2侧露出。另外,子像素SP2与子像素SP3之间的隔壁6露出。

图12是用于说明子像素SP2中的第1薄膜31的除去过程的图。下电极LE2之上的第1薄膜31的剖面在图中从左向右按除去顺序排列。

首先,将第1抗蚀剂41用作掩模来进行干式蚀刻,将从第1抗蚀剂41露出的密封层SE1除去。

然后,将第1抗蚀剂41用作掩模进行湿式蚀刻,将从密封层SE1露出的盖层CP1的无机层IL1除去。

然后,将第1抗蚀剂41用作掩模进行干式蚀刻,将从无机层IL1露出的盖层CP1的透明层TL1除去。

然后,将第1抗蚀剂41用作掩模进行湿式蚀刻,将从透明层TL1露出的上电极UE1除去。

然后,将第1抗蚀剂41用作掩模进行干式蚀刻,将从上电极UE1露出的有机层OR1除去,使下电极LE2露出。

同样地,子像素SP3中的密封层SE1、盖层CP1、上电极UE1及有机层OR1也被除去。

如图10的下部所示,在进行密封层SE1的蚀刻之前,在子像素SP2及SP3中,肋部5与密封层SE1之间的上电极UE1在隔壁6与有机层OR1之间覆盖肋部5。因此,密封层SE1与肋部5不相接。上电极UE1作为蚀刻阻止层发挥功能,上电极UE1的蚀刻速率小于密封层SE1的蚀刻速率。因此,在密封层SE1进行干式蚀刻时,在密封层SE1被完全除去后,能够在上电极UE1中停止干式蚀刻的进行。由此,在密封层SE1的干式蚀刻时,肋部5几乎没有受到损伤。另外,能够抑制形成贯通肋部5至绝缘层12为止的不希望的孔(水分浸入路径)。进而能够抑制由不希望的水分引起的下电极变色。另外,能够抑制产生由于有机EL元件、阳极的损伤而引起的有机EL元件不发光的像素缺陷。

因此,能够抑制可靠性的降低。

接下来,在步骤ST24中,如图13所示,将第1抗蚀剂41除去。由此,子像素SP1的密封层SE1露出。经过上述步骤ST21至ST24,在子像素SP1中形成显示元件201。显示元件201由下电极LE1、包含发光层EM1的有机层OR1、上电极UE1及盖层CP1构成。另外,显示元件201由密封层SE1覆盖。

在子像素SP1与子像素SP2之间的隔壁6上形成包含发光层EM1的有机层OR1、上电极UE1、盖层CP1及密封层SE1的层叠体。另外,隔壁6中的子像素SP1的侧的部分由密封层SE1覆盖。

接下来,在步骤ST31中,如图14的上部所示,遍及子像素SP1、子像素SP2及子像素SP3而形成第2薄膜32。第2薄膜32在子像素SP1中覆盖第1薄膜31。形成第2薄膜32的工序包括:在处理基板SUB之上形成包含发出绿色波长区域的光的发光层EM2的有机层OR2的工序;在有机层OR2之上形成上电极UE2的工序;在上电极UE2之上形成盖层CP2的工序;和在盖层CP2之上形成密封层SE2的工序。

有机层OR2分别形成在下电极LE2及下电极LE3之上,并且形成在子像素SP1的密封层SE1之上。另外,有机层OR2也形成在隔壁6之上。有机层OR2中的形成在隔壁6之上的部分与形成在下电极LE2正上方的部分及形成在下电极LE3正上方的部分分离。

上电极UE2形成在有机层OR2之上。分别形成在下电极LE2及下电极LE3正上方的上电极UE2覆盖肋部5,并与隔壁6的下部61相接。另外,在隔壁6的正上方,上电极UE2也形成在有机层OR2之上。上电极UE2具有厚度T12。厚度T12等于厚度T11、或小于厚度T11。

在下电极LE1、下电极LE2及下电极LE3的正上方,盖层CP2分别形成在上电极UE2之上,并且在隔壁6的正上方也形成在上电极UE2之上。

密封层SE2以覆盖盖层CP2及隔壁6的方式形成。也就是说,在下电极LE1、下电极LE2及下电极LE3的正上方,密封层SE2分别形成在盖层CP2之上,并且在隔壁6的正上方也形成在盖层CP2之上。

接下来,在步骤ST32中,如图14的下部所示,遍及密封层SE2之上的整个面而涂布第2抗蚀剂42。然后,如图15的上部所示,将第2抗蚀剂42图案化。第2抗蚀剂42覆盖子像素SP2的第2薄膜32,使子像素SP1及子像素SP3的第2薄膜32露出。也就是说,第2抗蚀剂42配置在下电极LE2的正上方。另外,第2抗蚀剂42从子像素SP2向隔壁6的上方延伸。另外,第2抗蚀剂42在子像素SP1及子像素SP3中使密封层SE2露出。

接下来,在步骤ST33中,如图15的下部所示,以第2抗蚀剂42为掩模进行蚀刻,将从第2抗蚀剂42露出的子像素SP1及子像素SP3的第2薄膜32除去,第2薄膜32残留于子像素SP2。由此,子像素SP1的密封层SE1露出,并且在子像素SP3中,下电极LE3露出,另外,包围下电极LE3的肋部5也露出。

在子像素SP1与子像素SP2之间的隔壁6上,第1薄膜31与第2薄膜32分离。也就是说,残留在隔壁6之上的密封层SE2、盖层CP2、上电极UE2及有机层OR2与残留在隔壁6之上的密封层SE1、盖层CP1、上电极UE1及有机层OR1分离。另外,在子像素SP2与子像素SP3之间的隔壁6上,隔壁6的子像素SP3侧露出。

如图15的上部所示,在进行密封层SE2的蚀刻之前,在子像素SP3中,肋部5与密封层SE2之间的上电极UE2在隔壁6与有机层OR2之间覆盖肋部5。因此,密封层SE2与肋部5不相接。上电极UE2作为蚀刻阻止层发挥功能,上电极UE2的蚀刻速率小于密封层SE2的蚀刻速率。因此,在进行密封层SE2的干式蚀刻时,在密封层SE2被完全除去后,能够在上电极UE2中停止干式蚀刻的进行。由此,在进行密封层SE2的干式蚀刻时,肋部5几乎没有受到损伤。因此,能够抑制可靠性的降低。

接下来,在步骤ST34中,如图16的上部所示,将第2抗蚀剂42除去。由此,子像素SP2的密封层SE2露出。经过这些步骤ST31至ST34,在子像素SP2中形成显示元件202。显示元件202由下电极LE2、包含发光层EM2的有机层OR2、上电极UE2及盖层CP2构成。另外,显示元件202由密封层SE2覆盖。

在子像素SP1与子像素SP2之间的隔壁6上及子像素SP2与子像素SP3之间的隔壁6上,形成有包含发光层EM2的有机层OR2、上电极UE2、盖层CP2及密封层SE2的层叠体。另外,隔壁6中的子像素SP2的侧的部分由密封层SE2覆盖。

接下来,在步骤ST41中,如图16的下部所示,遍及子像素SP1、子像素SP2及子像素SP3而形成第3薄膜33。第3薄膜33在子像素SP1中覆盖第1薄膜31,并且在子像素SP2中覆盖第2薄膜32。形成第3薄膜33的工序包括:在处理基板SUB之上形成包含发出蓝色波长区域的光的发光层EM3的有机层OR3的工序;在有机层OR3之上形成上电极UE3的工序;在上电极UE3之上形成盖层CP3的工序;和在盖层CP3之上形成密封层SE3的工序;。

有机层OR3形成在下电极LE3之上,并且也形成在子像素SP1的密封层SE1之上,另外,也形成在子像素SP2的密封层SE2之上。另外,有机层OR3也形成在隔壁6之上。在子像素SP1与子像素SP2之间的隔壁6上,有机层OR3覆盖第1薄膜31及第2薄膜32。有机层OR3中的在子像素SP2与子像素SP3之间的隔壁6之上形成的部分与下电极LE3的正上方形成的部分分离。

上电极UE3形成在有机层OR3之上形成。在下电极LE3的正上方形成的上电极UE3覆盖肋部5,并与隔壁6的下部61相接。另外,在隔壁6的正上方,上电极UE3也形成在有机层OR3之上。上电极UE3具有厚度T13。厚度T13小于厚度T11及T12。

在下电极LE1、下电极LE2及下电极LE3的正上方,盖层CP3分别形成在上电极UE3之上,并且在隔壁6的正上方形成在上电极UE3之上。

密封层SE3以覆盖盖层CP3及隔壁6的方式形成。也就是说,在下电极LE1、下电极LE2及下电极LE3的正上方,密封层SE3分别形成在盖层CP3之上,在上部62的正上方也形成在盖层CP3之上。

接下来,在步骤ST42中,如图17的上部所示,遍及密封层SE3之上的整个面而涂布第3抗蚀剂43。然后,如图17的下部所示,将第3抗蚀剂43图案化。第3抗蚀剂43覆盖子像素SP3的第3薄膜33,使子像素SP1及子像素SP2的第3薄膜33露出。也就是说,第3抗蚀剂43配置在下电极LE3的正上方。另外,第3抗蚀剂43从子像素SP3向隔壁6的上方延伸。另外,第3抗蚀剂43在子像素SP1及子像素SP2中使密封层SE3露出。

接下来,在步骤ST43中,如图18的上部所示,以第3抗蚀剂43为掩模进行蚀刻,将从第3抗蚀剂43露出的子像素SP1及子像素SP2的第3薄膜33除去,第3薄膜33残留于子像素SP3。由此,子像素SP1的密封层SE1露出,并且子像素SP2的密封层SE2露出。

另外,在子像素SP1与子像素SP2之间的隔壁6上,将第3薄膜33除去,第1薄膜31的一部分及第2薄膜32的一部分露出。

另外,在子像素SP2与子像素SP3之间的隔壁6上,第2薄膜32与第3薄膜33分离。也就是说,残留在隔壁6之上的密封层SE3、盖层CP3、上电极UE3及有机层OR3与残留在隔壁6之上的密封层SE2、盖层CP2、上电极UE2及有机层OR2分离。

接下来,在步骤ST44中,如图18的下部所示,将第3抗蚀剂43除去。由此,子像素SP3的密封层SE3露出。经过这些步骤ST41至ST44,在子像素SP3中形成显示元件203。显示元件203由下电极LE3、包含发光层EM3的有机层OR3、上电极UE3及盖层CP3构成。另外,显示元件203由密封层SE3覆盖。

在子像素SP2与子像素SP3之间的隔壁6上,形成包含发光层EM3的有机层OR3、上电极UE3、盖层CP3及密封层SE3的层叠体。

通过上述工序,在子像素SP1中形成显示元件201,在子像素SP2中形成显示元件202,在子像素SP3中形成显示元件203。

需要说明的是,也可能存在下述情况:在上述工序中的步骤ST21的形成第1薄膜31的工序中,发光层EM1由发出绿色波长区域的光的材料形成,另外,在步骤ST31的形成第2薄膜32形成的工序中,发光层EM2由发出红色波长区域的光的材料形成。

在上述例子中,子像素SP1与第1子像素相当,开口AP1与第1开口相当,下电极LE1与第1下电极相当,有机层OR1与第1有机层相当,发光层EM1与第1发光层相当,上电极UE1与第1上电极相当,盖层CP1与第1盖层相当,透明层TL1与第1透明层相当,无机层IL1与第1无机层相当,密封层SE1与第1密封层相当。另外,上电极UE1及无机层IL1中的至少一者作为第1蚀刻阻止层发挥功能。

另外,子像素SP2与第2子像素相当,开口AP2与第2开口相当,下电极LE2与第2下电极相当,有机层OR2与第2有机层相当,发光层EM2与第2发光层相当,上电极UE2与第2上电极相当,盖层CP2与第2盖层相当,密封层SE2与第2密封层相当。另外,上电极UE2及无机层IL2中的至少一者作为第2蚀刻阻止层发挥功能。

另外,子像素SP3与第3子像素相当,开口AP3与第3开口相当,下电极LE3与第3下电极相当,有机层OR3与第3有机层相当,发光层EM3与第3发光层相当,上电极UE3与第3上电极相当,盖层CP3与第3盖层相当,密封层SE3与第3密封层相当。另外,上电极UE3及无机层IL3中的至少一者作为第3蚀刻阻止层发挥功能。

如以上说明,根据本实施方式,能够提供能够抑制可靠性的降低、提高制造成品率的显示装置及其制造方法。

只要包含本发明的要旨,本领域技术人员基于以上本发明的实施方式说明的显示装置及其制造方法能够适当设计变更并实施的全部显示装置及其制造方法也属于本发明的范围。。

应知本领域技术人员在本发明的思想范畴内能够想到的各种变形例及其变形例也属于本发明的范围。例如,只要具备本发明的要旨,本领域技术人员针对上述实施方式、适当进行构成要素的追加、删除、或设计变更得到的技术方案或进行工序增加、省略或条件变更得到的技术方案也包含在本发明的范围内。

另外,就上述实施方式中说明的方式所带来的其他作用效果而言,根据本说明书的记载所能明确的或本领域技术人员能够适当想到的作用效果当然应视为本发明带来的作用效果。