一种用于高压供电控制系统和控制方法

文献发布时间:2023-06-19 13:26:15

技术领域

本发明涉及开关电源技术领域,尤其涉及一种用于高压供电控制系统和控制方法。

背景技术

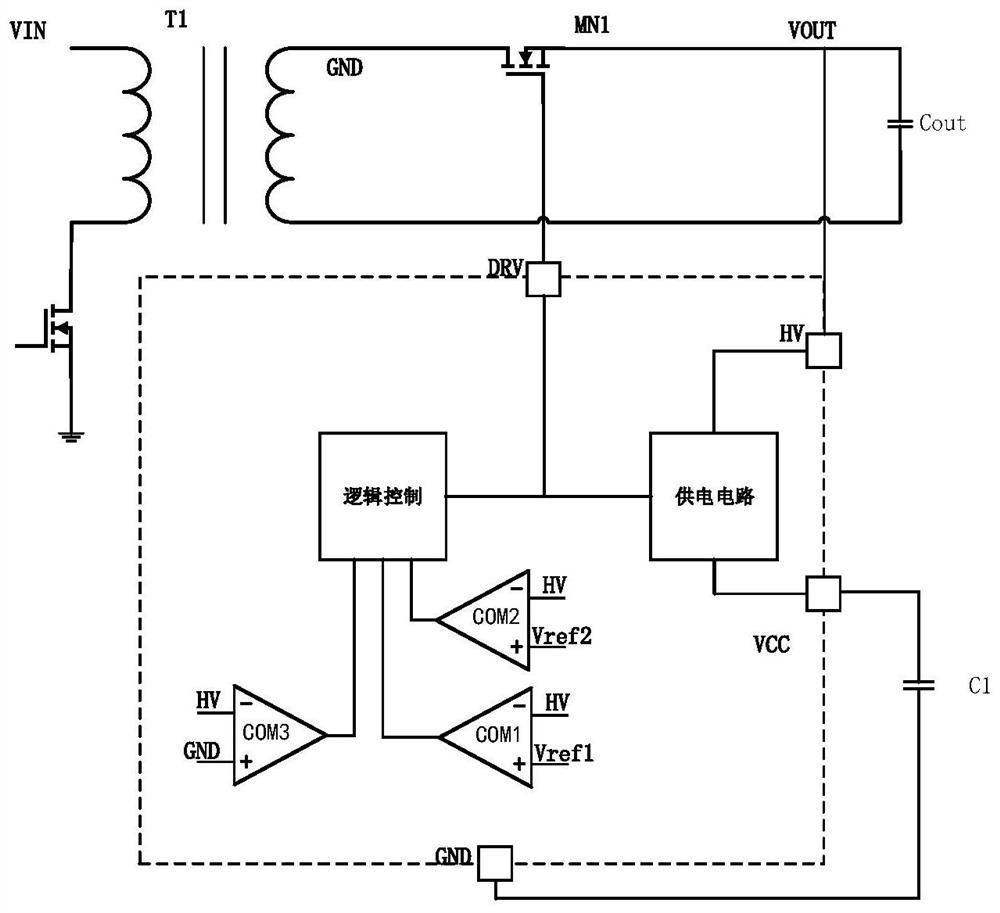

同步整流芯片在ACDC开关电源领域应用的越来越广泛,为了减少外围器件,降低成本现其供电都采用高压供电。如图1所示,当同步整流管打开时,功率管MN1两端的电压接近为0。当同步整流管NM1关闭时,原边芯片导通时功率管两端的电压会有很高的压降。在此器件芯片的HV和GND有相同的高电压,可以利用此压差来给VCC进行蓄电和供电。

现有的高压供电电路如CN106376145,采用JFET和两个NMOS管串联控制供电。但存在以下缺点:1.JFET在工艺上实现需要特殊工艺要求同时可能会增加mask成本。2.充电时NMOS的Vgs电压为较低,限制充电电流在短时间内无法完成快速的充电。特别大功率(驱动耗电较多),在小占空比下(充电时间较短)导致供电不足无法工作的问题。3.当充电电流较大时,需要增加JFEF和两个串联NMOS的面积来满足电流需求。另一高压供电电路CN109510484,采用JFET和二极管来控制实现:同样存在上述第一个缺点,同时若JFET的夹断电压高于VCC电压,则存在无法关闭的问题。此电路无法正常工作。

如何解决上述技术问题为本发明面临的课题。

发明内容

本发明的目的在于提供一种用于高压供电控制系统和控制方法,解决了现有的高压供电控制系统结构复杂需要特殊器件JFET,面积较大成本较高,原边导通时间较短时,供电需求不足的问题。

本发明的思想为:本发明通过高压LDMOS管NM1进行对VCC的充电控制,为了驱动NM1管,通过电阻R1、Zener管Z1和高压管NM2,产生驱动电压VPOW,电容C2同于功率管NM1的自举驱动,D2防止C2上电容倒灌HV引脚,或门OR1和反相器INV1用于VCC充电的逻辑控制,UVLO比较器用于欠压前的控制,Vclamp比较器控制VCC的电压大小,DRV信号,控制只有在副边关断时,HV电压较高才能进行充电。

本发明是通过如下措施实现的:一种用于同步整流的高压供电控制系统,其中,包括变压器T1、同步整流MOS管NM1、输出电容Cout、以及同步整流控制芯片;

所述同步整流控制芯片由高压供电电路,开启关断检测电路和逻辑控制驱动电路组成;

所述开启关断检测电路由比较器COM1、COM2和COM3组成,COM1和COM2比较器两端分别接HV和第一基准以及第二基准,用于判断功率管两端电压的开启斜率;COM3比较器两端分别接HV和GND,用于检测功率管开始时两端电压随着电流下降接近于0时,用于判断功率管两端的关断电压;

所述逻辑控制驱动电路输入为COM1、COM2和COM3,通过逻辑组合输出功率管的控制信号DRV,输入高压供电电路,同步控制供电电路的充电管理;

所述高压供电电路通过HV引脚连接VOUT,当MN1关闭时,VOUT-GND的压差,通过高压供电电路给VCC供电;当MN1打开时,VOUT-GND压差接近0V,此时通过高压供电电路切断与VCC的连接,内部模块通过VCC的电容上存储能量供电。

作为本发明提供的一种用于同步整流的高压供电控制系统进一步优化方案,所述充电NMOS管NM2用充电控制,其源端连接单向导通二极管D1,外接稳压电容C1,并连接内部电路,给其供电,比较器COM通过检测VCC电压和基准进行比较,当VCC电压较高时,通过逻辑控制驱动电路控制充电管MN2的导通。

作为本发明提供的一种用于同步整流的高压供电控制系统进一步优化方案,所述电阻R1和钳位管Z1组成的钳位电路,驱动供电管NM2以及单向导通二极管D1,驱动电容C1,迟滞比较器COM4和COM5,检测VCC电压,通过逻辑门OR1和INV1控制gate的打开和关闭。

为了更好地实现本发明目的,本发明还提供一种用于同步整流的高压供电控制系统的控制方法,所述控制方法包括以下步骤:

步骤一,启动时,由于VCC电压较低,同时C1上电容需要一定时间达到钳位点,通过UVLO比较器将C1下级板拉至0V,VCC随着Vgate电压充电上升;

步骤二,在启动接近完成时,电阻R1和钳位管Z1组成的钳位电路,通过NMOS管NM2将gate电压控制在5V左右;此时NM1的GATE电压充电接近5V,内部基准开始建立,UVLO比较器开始工作;

步骤三,UVLO之后,当VCC电压低于钳位点需要充电,同时原边芯片开启同步整流管关闭时HV电压为高电平,比较器COM5翻转,此时将电容C1的下级板电压高至VCC,故NM1的gate电压为VCC+VPOW,此时NM1的Vgs电压为VPOW,充电管NM1打开开始进行VCC充电。

步骤四,当VCC电压充高至VCC钳位电压时,比较器COM5翻转将电容C1的下级板电压降低为0V,此时GATE电压为VCC,NM1的Vgs为0V关闭停止对VCC充电;

步骤五,当VCC电压未冲到VCC钳位电压,但是原边芯片关闭副边芯片打开,此时HV接近0V,DRV为高电平,同样将电容C1的下级板电压降低为0V,GATE电压为VCC关闭充电,此时二极管D1防止电容C1电荷通过NM2的体二极管泄放,保证下次打开时能够快速的建立,二极管D2可以防止VCC电压通过NM1的体二极管泄放。

与现有技术相比,本发明的有益效果为:

1.本发明专利无需使用JFET,通过高压LDMOS管NM1,就可以实现动态的充电控制。通过控制高压管NM1的GATE电压实现充电路径的打开和关断。当VCC电压由于内部电路消耗而降低时,开启NM1进行充电,其GATE电压为VCC+5V;当VCC电压高于设定电压时控制GATE电压关闭NM1,其GATE电压为接近VCC,实现对VCC电压的钳位,防止VCC下器件击穿。通过此动态控制,实现原电路高压JFET和中压NMOS两个器件的功能。

2.本发明通过电容C1,将NM1的GATE电压控制在VCC和VCC+5V,故Vgs电压关闭时为0V,打开时为5V。打开充电时NM1可以完全的打开,电流能力释放。原电路M0其充电时,由于GATE和漏端接一起,Vgs电压受其流过电流和rdson限制。同时当输入电压较低时,其漏端电压受到压制,导致充电电流较小无法保证VCC有足够的电压,芯片存在无法正常工作的风险。尤其当芯片进入空载模式时,原边芯片打开时间短关闭时间长,导致HV电压保持高电平的时间较短,若此时充电电流受到限制,无法保证芯片在此工作状态下的供电,导致系统无法正常工作。

3.本发明通过将驱动信号和VCC充电阈值电压组合进行控制充电路径,简化电路无需额外的电荷泵控制电路。若充分打开NMOS管需要提供高于源端电压5V的电位来实现,但是在输入电压较低时,NM1的源端电压接近芯片的最高电压HV,所以无法直接通过HV产生电压来控制NM1的打开。一般做法想要得到高于输入电压的电源,需要电荷泵将电压升上去,此电路结构较为复杂。本发明结合电路,由于在NM1打开时,其GATE电压几乎不耗电,所以在需要打开NM1,通过较小的电容C1将GATE抬高至VCC+5V,同时二极管D1可以防止C1上电压通过NM2向HV放电。

附图说明

附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。

图1为本发明同步整流的高压供电控制系统的同步整流工作框图。

图2为本发明同步整流的高压供电控制系统的VCC供电内部结构框图。

图3为本发明同步整流的高压供电控制系统的电路工作时序图。

具体实施方式

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。当然,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

参见图1至图3,本发明提供其技术方案为,一种高压供电控制系统,其中,包括变压器T1、同步整流MOS管NM1、输出电容Cout、以及同步整流控制芯片;

所述同步整流控制芯片由高压供电电路,开启关断检测电路和逻辑控制驱动电路组成;

所述开启关断检测电路由比较器COM1、COM2和COM3组成,COM1和COM2比较器两端分别接HV和第一基准以及第二基准,用于判断功率管两端电压的开启斜率;COM3比较器两端分别接HV和GND,用于检测功率管开始时两端电压随着电流下降接近于0时,用于判断功率管两端的关断电压;

所述逻辑控制驱动电路输入为COM1、COM2和COM3,通过逻辑组合输出功率管的控制信号DRV,输入高压供电电路,同步控制供电电路的充电管理;

所述高压供电电路通过HV引脚连接VOUT,当MN1关闭时,VOUT-GND的压差,通过高压供电电路给VCC供电;当MN1打开时,VOUT-GND压差接近0V,此时通过高压供电电路切断与VCC的连接,内部模块通过VCC的电容上存储能量供电。

优选地,所述充电NMOS管NM2用充电控制,其源端连接单向导通二极管D1,外接稳压电容C1,并连接内部电路,给其供电,比较器COM通过检测VCC电压和基准进行比较,当VCC电压较高时,通过逻辑控制驱动电路控制充电管MN2的导通。

优选地,所述电阻R1和钳位管Z1组成的钳位电路,驱动供电管NM2以及单向导通二极管D1,驱动电容C1,迟滞比较器COM4和COM5,检测VCC电压,通过逻辑门OR1和INV1控制gate的打开和关闭。

为了更好地实现本发明目的,本发明还提供一种用于高压供电控制系统的控制方法,具体包括以下步骤:

步骤一,启动时,由于VCC电压较低,同时C1上电容需要一定时间达到钳位点,通过UVLO比较器将C1下级板拉至0V,VCC随着Vgate电压充电上升;

步骤二,在启动接近完成时,电阻R1和钳位管Z1组成的钳位电路,通过NMOS管NM2将gate电压控制在5V左右;此时NM1的GATE电压充电接近5V,内部基准开始建立,UVLO比较器开始工作;

步骤三,UVLO之后,当VCC电压低于钳位点需要充电,同时原边芯片开启同步整流管关闭时HV电压为高电平,比较器COM5翻转,此时将电容C1的下级板电压高至VCC,故NM1的gate电压为VCC+VPOW,此时NM1的Vgs电压为VPOW,充电管NM1打开开始进行VCC充电;

步骤四,当VCC电压充高至VCC钳位电压时,比较器COM5翻转将电容C1的下级板电压降低为0V,此时GATE电压为VCC,NM1的Vgs为0V关闭停止对VCC充电;

步骤五,当VCC电压未冲到VCC钳位电压,但是原边芯片关闭副边芯片打开,此时HV接近0V,DRV为高电平,同样将电容C1的下级板电压降低为0V,GATE电压为VCC关闭充电,此时二极管D1防止电容C1电荷通过NM2的体二极管泄放,保证下次打开时能够快速的建立,二极管D2可以防止VCC电压通过NM1的体二极管泄放。

如图1所示,为同步整流的内部控制框图。当原边功率管关闭,功率管MN1的源端电压GND开始升高。芯片通过检测HV和GND压差判断其电压电压升高至vout,当比较器COM1和COM2同时翻转时,开始打开功率管MN1,此时HV和GND压差为-Iout*Rdson。电流开始给负载供电。当原边功率管打开时,功率管源端电压开始下降,同样芯片通过检测HV和GND压差判断其电压电压降低至vout,当比较器COM3翻转时,关闭MN1防止输出负载电流导管,此时HV-GND压差为Vout+Vin/n,其中n为变压器的匝比。在此工作过程中,当MN1关闭时,HV和GND电压为正值;MN1打开时其压差为负值。故需要在MN1关闭时,对VCC进行充电,同时通过外部电容存储能量,在MN1打开时通过电容上的能量保证芯片的继续工作。

图2为本供电系统的具体实施,其中DRV信号为副边功率管的驱动信号,给VCC的充电只能在副边功率管关闭时进行,因为此时HV的电压相对于GND为高电平。COM4为UVLO比较器,启动时VCC电压较低,此时GATE电压接近Z1的钳位电压5V,高于VCC有足够的压差来打开充电NM1,不需要控制C1对GATE电压进行升压。当达到UVLO之后,通过COM5来进行对VCC电压的钳位功能,低于Vref2时将C1下极板电压抬高VCC,此时Vgate=VCC+5V,故NM1的Vgs电压为5V,打开NM1进行充电。当VCC电压达到设定值Vref2时,C1的下极板电压为0V,Vgate为5V,vgs接近0V,NM1关闭停止充电。其中二极管D1防止电容C1电荷通过NM2的体二极管泄放,保证下次打开时能够快速的建立。二极管D2可以防止VCC电压通过NM1的体二极管泄放。

图3为本实例的实际工作波形,从图中可以看出,启动时由于VCC电压较低在GATE为电平的整个时间内,全部给VCC充电,使其电压快速上升到目标值,保证芯片能够正常工作。当电压到达目标钳位值时,随着芯片工作电流的消耗VCC电压降低,此时在副边芯片关闭时仅需要很短的时间内就可以将VCC电压充值目标值,达到目标值Vref2后通过比较器COM2将充电路径关闭。同时整个充电过程,只能在副边功率管关闭时HV电压为高电平时进行。

由上可以得到:VCC的充电时间为原边功率管打开,HV和GND的压差为高电平的时段。但是当负载为轻载或者输入电压较高时芯片占空比较小,原边功率管打开的时间较短,关闭时间较长;意味着VCC的充电时间比较短,而芯片在整个周期内都会一直耗电。若在较短的时间内充电电流不能满足整个周期内的消耗,将会导致VCC电压逐渐的降低,最终导致芯片无法正常工作。此时由于HV和VCC的压差很大,充电管NM1工作在饱和区,其充电电流大小在NM1面积一定下与Vgs的平方成正比例关系。本发明在充电管打开时,充电管Vgs的电压为5V处于完全打开状态,电流能力可以完全释放,在不增加其面积的前提下能够满足在较小的时间内对VCC充电。

由上同样可以得到:当充电时HV与GND的压差为Vout+Vin/n,在Vin和Vout较低时,HV的电压较低导致充电路径上HV到VCC的压差较低,此时充电管的Vds电压较低其工作于线性区,流经NM1的电流大小同Vgs和Vds都成正比例关系。本发明不仅提高了Vgs电压,同时在充电路径上用一个NMOS管代替JFET和NMOS的串联,增大了MOS管的Vds电压,同样提高在低压时的充电电流。

综上可知,本发明通过充分提高充电管NM1无论工作与饱和区或者线性区的电流能力,可以适用于较为严苛的工作条件,包括输入电压较高和负载轻载时,在充电时间较短的情况下;或者输入输出电压较低时,充电压差很小的情况;在不增加NM1的面积前提下,都能保证VCC的充足供电,使芯片能够稳定的工作,具有更高的效率和成本优势。同时通过电路设计使电路结构更加精简,无需JFET,进一步增加成本优势。以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。