基板和半导体装置

文献发布时间:2024-01-17 01:14:25

技术领域

本发明涉及半导体技术领域,尤其涉及一种基板和半导体装置。

背景技术

电子元件、手持设备和通信设备的技术和小型化不断进步,需要卓越的热电性能和微型封装。先进而复杂的集成电路(Integrated Circuit,IC)设备通常需要增加I/O(输入/输出,input/output)的数量,同时保持其小尺寸、占用空间和重量。双排QFN(Quad FlatNo-leads Package,四方扁平无引脚封装)是此类要求苛刻应用的理想解决方案。

多排QFN封装是一种塑料包封封装(plastic-encapsulated package),带有铜引脚框架(leadframe)基板。底部裸露的晶粒贴装焊盘(die attach paddle)有效地将热量传导至PCB,并通过向下接合(bond)或通过导电晶粒贴装材料(conductive die attachmaterial)的电气连接提供稳定的接地。多排QFN封装的设计允许灵活性并增强电气性能以达到非常高速的工作频率。

如本领域已知的,差分信号已被用于多排QFN封装的PCB布线,其使用两个互补信号来传输一个数据信号,但第二信号与第一信号相反。信号接收器使用反相信号和非反相信号之间的差异来解密信息。使用差分对(differential pair)路由(routing)传输信号具有降低噪声和EMI等优势。但是缺点是比较占地方。

此外,为了获得差分对布线的最佳性能,线(line)的长度必须相等,线对必须布线在一起并以相同的宽度布线,这在绕过电路板上的障碍物(例如过孔或较小的组件)布线时可能会出现问题。

发明内容

有鉴于此,本发明提供一种基板和半导体装置,涉及基底基板的球垫(ball pad)(或指垫(finger pad))布局,用于多排四方扁平无引线(Quad Flat No-leads Package,QFN)封装的具有差分对(differential pair)布线的板级球焊盘(或焊球焊盘)图案(或布局)。

根据本发明的第一方面,公开一种基板,包括:

焊球焊盘,具有多个并交错排列,并且设置在用于安装多排QFN封装的表面安装区域内,其中,该焊球焊盘包括排列在第一排中的第一焊球焊盘和排列在第二排中的第二焊球焊盘,其中,该第一排的该第一焊球焊盘以两个不同的间距排列,该第二排的该第二焊球焊盘以固定的间距排列。

根据本发明的第二方面,公开一种基板,包括:

焊球焊盘,具有多个并交错排列,并且设置在用于安装多排QFN封装的表面安装区域内,其中,该焊球焊盘包括排列在第一排中的第一焊球焊盘和排列在第二排中的第二焊球焊盘,其中,该第一排的该第一焊球焊盘以两个不同的间距P1和间距P2排列,该第二排的该第二焊球焊盘以固定的间距P3排列;以及

至少两个差分对走线,设置于第一排中相邻的两个第一焊球焊盘之间。

根据本发明的第三方面,公开一种半导体装置,包括:

基底基板,包括:焊球焊盘,具有多个并交错排列,并且设置在用于安装多排QFN封装的表面安装区域内,其中,该焊球焊盘包括排列在第一排中的第一焊球焊盘和排列在第二排中的第二焊球焊盘,其中,该第一排的该第一焊球焊盘以两个不同的间距排列,该第二排的该第二焊球焊盘以固定的间距排列;

基本焊盘单元,由该第一排的两个第一焊球焊盘和该第二排的三个第二焊球焊盘组成的五个焊盘组成;

其中,该多排QFN的表面贴装区域内的该焊球焊盘由该基本焊盘单元重复构成。

本发明的基板由于包括:焊球焊盘,具有多个并交错排列,并且设置在用于安装多排QFN封装的表面安装区域内,其中,该焊球焊盘包括排列在第一排中的第一焊球焊盘和排列在第二排中的第二焊球焊盘,其中,该第一排的该第一焊球焊盘以两个不同的间距排列,该第二排的该第二焊球焊盘以固定的间距排列。第一排的焊球焊盘与第二排的焊球焊盘交错排列,并且第一排的焊球焊盘以两个不同的间距排列,第二排的焊球焊盘以固定的间距排列,因此,位于第一排的具有较大间距的相邻的两个焊球焊盘之间留出了足够的空间,以使对应的位于第二排的相邻的两个的焊球焊盘的走线可以同时穿过,从而容易形成差分对,这样布线或走线将更加容易布局,避免了先前技术中布线或走线容易出现的问题。

附图说明

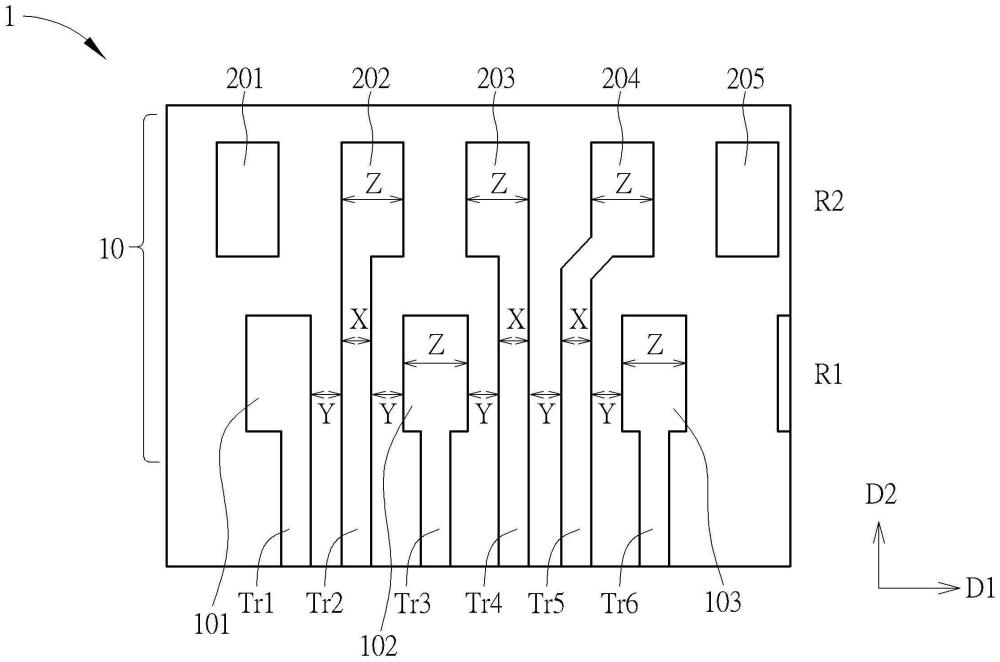

图1示出了根据本发明一个实施例的用于多排QFN封装的球焊盘或焊球焊盘(ballpad)布局的示例性基底顶层(top layer)的相关部分;

图2为多排QFN封装组装后沿图1中I-I'线的剖视示意图;

图3示意性地示出了根据本发明实施例的用于多行(多排)QFN封装的部分焊盘布局和焊盘间距(pad pitch)。

具体实施方式

在下面对本发明的实施例的详细描述中,参考了附图,这些附图构成了本发明的一部分,并且在附图中通过图示的方式示出了可以实践本发明的特定的优选实施例。对这些实施例进行了足够详细的描述,以使本领域技术人员能够实践它们,并且应当理解,在不脱离本发明的精神和范围的情况下,可以利用其他实施例,并且可以进行机械,结构和程序上的改变。本发明。因此,以下详细描述不应被理解为限制性的,并且本发明的实施例的范围仅由所附权利要求限定。

将理解的是,尽管术语“第一”、“第二”、“第三”、“主要”、“次要”等在本文中可用于描述各种组件、组件、区域、层和/或部分,但是这些组件、组件、区域、这些层和/或部分不应受到这些术语的限制。这些术语仅用于区分一个组件、组件、区域、层或部分与另一区域、层或部分。因此,在不脱离本发明构思的教导的情况下,下面讨论的第一或主要组件、组件、区域、层或部分可以称为第二或次要组件、组件、区域、层或部分。

此外,为了便于描述,本文中可以使用诸如“在...下方”、“在...之下”、“在...下”、“在...上方”、“在...之上”之类的空间相对术语,以便于描述一个组件或特征与之的关系。如图所示的另一组件或特征。除了在图中描述的方位之外,空间相对术语还意图涵盖设备在使用或运行中的不同方位。该设备可以以其他方式定向(旋转90度或以其他定向),并且在此使用的空间相对描述语可以同样地被相应地解释。另外,还将理解的是,当“层”被称为在两层“之间”时,它可以是两层之间的唯一层,或者也可以存在一个或多个中间层。

术语“大约”、“大致”和“约”通常表示规定值的±20%、或所述规定值的±10%、或所述规定值的±5%、或所述规定值的±3%、或规定值的±2%、或规定值的±1%、或规定值的±0.5%的范围内。本发明的规定值是近似值。当没有具体描述时,所述规定值包括“大约”、“大致”和“约”的含义。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明。如本文所使用的,单数术语“一”,“一个”和“该”也旨在包括复数形式,除非上下文另外明确指出。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明构思。如本文所使用的,单数形式“一个”、“一种”和“该”也旨在包括复数形式,除非上下文另外明确指出。

将理解的是,当将“组件”或“层”称为在另一组件或层“上”、“连接至”、“耦接至”或“邻近”时,它可以直接在其他组件或层上、与其连接、耦接或相邻、或者可以存在中间组件或层。相反,当组件称为“直接在”另一组件或层“上”、“直接连接至”、“直接耦接至”或“紧邻”另一组件或层时,则不存在中间组件或层。

注意:(i)在整个附图中相同的特征将由相同的附图标记表示,并且不一定在它们出现的每个附图中都进行详细描述,并且(ii)一系列附图可能显示单个项目的不同方面,每个方面都与各种参考标签相关联,这些参考标签可能会出现在整个序列中,或者可能只出现在序列的选定图中。

图1是示出根据本发明的一个实施例的用于多排QFN封装的球焊盘(或焊球焊盘)布局1的示例性基底顶层的相关部分的示意图。图2为多排QFN封装组装后沿图1中I-I’线的剖面示意图。如图1和图2所示,在基底基板PB的顶层TL中制作的球垫(或焊球焊盘)布局1(或基板1)包括交错排列的球垫(或指状垫),例如包括排列在第一行(或第一排)R1中的球垫(或焊球焊盘)101-103和排列在第二排R2球垫中的(或焊球焊盘)201-205。根据本发明的一个实施例,例如,球垫(或焊球焊盘)101-103与201-205可为铜垫(或铜焊盘),但不以此为限。因此本发明实施例中的焊球焊盘(例如焊球焊盘101-103与201-205)具有多个并交错排列。基底基板(base substrate)PB可包括印刷电路板或封装基板,但不限于此,其中基底基板PB也可以简称为基板PB(例如可为印刷电路板或封装基板等)。本发明实施例中,涉及在基板PB上布置的焊球焊盘的布局,该基板PB可以用于安装IC或半导体封装(例如图2所示的多排QFN封装50等)。在本发明一个实施例中,IC或半导体封装(例如图2所示的多排QFN封装50等)上的引脚的布局可以与本发明实施例的焊球焊盘的布局相同或相对应。在一个实施例中,本发明实施例中的基板上包括板级焊盘图案(board-level pad pattern),板级焊盘图案例如为如下描述的交错排列的第一排的焊球焊盘和第二排的焊球焊盘。在本发明另一个实施例中,基底基板PB或基板PB也可以称为半导体装置,或半导体结构,或基板结构等等。本发明实施例中,可以将QFN封装等半导体封装安装在基板上,形成半导体装置。因此本发明实施例中半导体装置可以包括基板(例如PCB或封装基板等)以及安装在基板之上的IC或半导体封装(半导体封装中可以包括晶粒等部件)等。

根据本发明的实施例,球焊盘(或焊球焊盘)101-103和201-205设置在表面安装区域10内,用于使用本领域已知的表面安装技术安装多排QFN封装50(如图2所示)。如图2所示,多排QFN封装50底侧(bottom side)的引脚(lead)511-513可以通过焊点SN接合到对应的球垫(或焊球焊盘)101-103和201-205以形成电连接路径。根据本发明的一个实施例,例如,球焊盘(或焊球焊盘)101-103和201-205可以是非阻焊层限定(NSMD,non-solder maskdefined)焊盘。为了简单起见,图1中省略了阻焊层。

如图1所示,在本发明的一个实施例中,排列于第一排R1的焊球焊盘101~103大致沿第一方向D1对齐。在本发明的一个实施例中,排列于第二排R2的焊球焊盘201~205大致沿第一方向D1对齐。根据本发明的一个实施例,焊球焊盘101-103和201-205可以在与第一方向D1正交(垂直)的第二方向D2上交错排列。本发明实施例中,焊球焊盘101-103与焊球焊盘201-205例如可以在第一方向D1上交错排列,焊球焊盘101-103与焊球焊盘201-205例如还可以在第二方向D2上交错排列。

根据本发明的实施例,例如,焊球焊盘101可以连接到走线(trace)Tr1,焊球焊盘202可以连接到走线(或迹线)Tr2,焊球焊盘102可以连接到走线Tr3,焊球焊盘202可以连接到走线Tr2。焊球焊盘203可以连接到走线Tr4,焊球焊盘204可以连接到走线Tr5,焊球焊盘103可以连接到走线Tr6。在本发明的一个实施例中,例如走线Tr1~Tr6可沿第二方向D2延伸。

在本发明的一个实施例中,举例而言,仅走线Tr2穿过第一排R1的焊球焊盘101与焊球焊盘102之间的走线空间。在本发明的一个实施例中,例如相邻的两条走线Tr4、Tr5穿过第一排R1中的焊球焊盘102与焊球焊盘103之间的走线空间。根据本发明的一个实施例,例如,走线Tr4和Tr5被指定为差分对(differential pair),相邻的焊球焊盘103和103被指定为接地焊盘,从而构成接地-信号-信号-接地(ground-signal-signal-ground,GSSG)路由配置。在图1中,每个焊球焊盘101-103和201-205的宽度被标记为Z,每个走线Tr1-Tr6的宽度被标记为X,以及走线Tr2、Tr4、Tr5与焊球焊盘101-103之间的空间用Y表示。

图3示意性地示出了根据本发明实施例的焊球焊盘的局部布局和焊盘间距。为了简单起见,图3中省略了阻焊层和走线。如图3所示,根据本发明的一个实施例,第一排R1中的焊球焊盘101-105以两个不同的间距P1和P2排列,例如P1=0.5mm,P2=0.7mm。根据本发明的一个实施例,P1=X+2Y+Z且P2=2X+3Y+Z。根据本发明的实施例,例如,第二排R2中的焊球焊盘201-205以约0.4mm的恒定间距P3排列,其等于每个焊球焊盘101-105的宽度Z加上两个相邻焊球焊盘的间距约为0.18-0.2mm(P3=Z+V,其中V=0.18-0.2mm)。在本发明的一个实施例中,例如,各个焊球焊盘101~105的宽度Z为0.2mm。第一排R1和第二排R2以间距P2排列。因此,本发明实施例中,基板上的焊球焊盘以交错排列的方式来布局,从而更加合理和科学的利用布局空间,可以在相同的面积的区域内布置更多的焊球焊盘数量(相对应的,可以在相同的面积的区域内布置更多的引脚数量),或者/和,在设置相同数量的焊球焊盘(或对应的,相同数量的引脚)时采用本发明实施例的方案可以使得基板的尺寸更小。因此,本发明实施例提供的布局方式也可以对应的应用到半导体封装(例如多排QFN封装50)上的焊球布局或引脚布局。

图3还示出了由五个焊盘组成的基本焊盘单元PU。例如,基本焊盘单元PU1由第一排R1的两个焊球焊盘101和102以及第二排R2的三个球焊盘201-203组成,下一个基本焊盘单元PU2由第一排R1的两个球焊盘103、104和第二排R2的三个焊球焊盘204-206组成。多行(多排)QFN的焊盘阵列是通过重复基本焊盘单元PU构成的。通过使用这种由五个焊盘组成的基本焊盘单元PU,可以在形成焊球焊盘布局之后,让相邻的基本焊盘单元之间并且位于第一排R1的焊球焊盘的间距保持为P2(例如焊球焊盘102和103的间距为P2),让相邻的基本焊盘单元之间并且位于第二排R1的焊球焊盘的间距保持为P3(例如焊球焊盘203和204的间距为P3)。这样形成焊球焊盘布局之后,所有位于第一排R1的焊球焊盘均以不同的间距(P1和P2)排列,所有位于第二排R2的焊球焊盘均以相同的间距(P3)排列。本发明实施例中,通过基本焊盘单元PU的设置,可以方便设计和制造,并且布局设计更加合理。基本焊盘单元PU中的焊球焊盘可以是具有相同或不同功能的焊球焊盘,或者基本焊盘单元PU中可以至少有两个焊球焊盘的功能/连接目的相同或不同。本发明实施例中基本焊盘单元PU是一种布局设计,其中的功能需求可以根据需求自由设计和组合,本发明不作限制。其中第一排R1可以更靠近基板的外边缘,第二排R2可以更靠近基板的晶粒安装区域。

使用本发明是有利的,因为对于12.7mmx12.7mm双排QFN封装(从176引脚增加到186引脚),焊球焊盘的数量可以增加4.5%。或者,对于176引脚双排QFN封装,双排QFN封装的尺寸可以减少7.7%(从12.7mmx12.7mm到12.2mmx12.2mm)。此外,在为多排QFN封装布线时更容易分配差分对。具体来说,例如本发明实施例中,第一排R1的焊球焊盘(例如焊球焊盘101-103)与第二排R2的焊球焊盘(例如焊球焊盘201-205)交错排列,并且第一排R1的焊球焊盘具有P2的间距,第二排R2的焊球焊盘具有P3的间距,因此,位于第一排R1的具有间距P2的相邻的两个焊球焊盘之间留出了足够的空间,以使对应的位于第二排R2的相邻的两个的焊球焊盘的走线可以同时穿过,从而形成差分对。例如如图1和3所示,可以使用位于第二排R2的焊球焊盘203和204作为差分对,连接到焊球焊盘203和204的走线(Tr4和Tr5)将穿过位于第一排R1的焊球焊盘102和103之间的间距空间(焊球焊盘102和103之间的间距为P2,P2较大,例如大于P1),从而得到差分对及其走线。采用本发明上述方案,得到差分对的焊球焊盘位于同一排(例如均位于第二排R2的焊球焊盘203和204),差分对的布置更加合理和方便设计。作为对比,先前技术中,第一排的焊球焊盘例如仅仅为间距P1进行排列,这样导致位于第一排的两个相邻的焊球焊盘之间间距仅能穿过一条走线,因此先前技术中在形成差分对时,需要使用比特于第一排的一个焊球焊盘和位于第二排的一个焊球焊盘,例如焊球焊盘102和202(两者位于不同的排)。因此先前技术中形成的差分对更容易存在各种问题。如上所述,本发明的上述方案可以解决先前技术中形成的差分对存在的问题,并且还可以优化焊盘布局,节省空间。使用本发明实施例的方案容易形成差分对,这样布线或走线将更加容易布局,避免了先前技术中布线或走线容易出现的问题。

本领域的技术人员将容易地观察到,在保持本发明教导的同时,可以做出许多该设备和方法的修改和改变。因此,上述公开内容应被解释为仅由所附权利要求书的界限和范围所限制。