信号处理电路、信号处理设备以及信号处理方法

文献发布时间:2023-06-19 10:00:31

技术领域

本公开涉及一种信号处理电路、信号处理设备以及信号处理方法。

背景技术

专利文献1描述了通过使用两个信号之间的时间差而表示运算结果信息的乘积累加运算设备。专利文献1中所描述的乘积累加运算设备可应用于神经网络电路。神经网络电路具有包括多层的相互连接的多层配置,每层包括多个乘积累加的运算电路。此外,将执行各种类型的信号处理的信号处理电路设置在一层与另一层之间。各种类型的信号处理的实例包括激活函数算术处理和最大池化处理(最大池化)。

通过数字信号处理电路执行上述各种类型的信号处理。因此,在执行上述各种类型的信号处理之前,需要使用将表示具有时间差的信息的两个信号转换成数字信号的时间-数字转换器电路。该时间-数字转换器电路与模数(A/D)转换器电路对应。进一步地,在执行上述各种类型的信号处理之后,需要使用将数字信号转换成表示具有时间差的信息的两个信号的数字-时间转换器电路。该数字-时间转换器电路与数字-模拟(D/A)转换器电路对应。

引用列表

专利文献

专利文献1:WO 2018/034163 A

发明内容

技术问题

然而,不幸的是,时间-数字转换器电路与数字-时间转换器电路消耗大量的功率。

鉴于此,本公开提议一种能够抑制功耗的信号处理电路、信号处理设备以及信号处理方法。

问题的解决方案

根据本公开,提供一种信号处理电路:在第一输入信号改变的第一定时早于或与第二输入信号改变的第二定时相同的情况下,在第一定时输出第一输出信号并且在第二定时输出第二输出信号,并且在第一定时晚于第二定时的情况下,在第二定时输出第一输出信号和第二输出信号。

而且,根据本公开,提供一种信号处理设备,包括:乘积累加运算电路,执行分别使多个信号与第一组的系数相乘并且相加的第一乘积累加运算并且输出第一信号,并且执行分别使多个信号与第二组的系数相乘并且相加的第二乘积累加运算并且输出第二信号;和信号处理电路,在第一信号改变的第一定时早于或与第二信号改变的第二定时相同的情况下,在第一定时输出第一输出信号并且在第二定时输出第二输出信号,并且在第一定时晚于第二定时的情况下,在第二定时输出第一输出信号和第二输出信号。

发明的有利效果

根据本公开,可以抑制功耗。应注意,此处所述的效果不一定必须受限制并且可以是本公开中所描述的任意效果。

附图说明

图1是示出根据本公开的第一实施方式的神经网络设备的配置的示图。

图2是示出根据本公开的第一实施方式的神经网络设备的乘积累加运算电路的配置的示图。

图3是示出ReLU的输入/输出特征的示图。

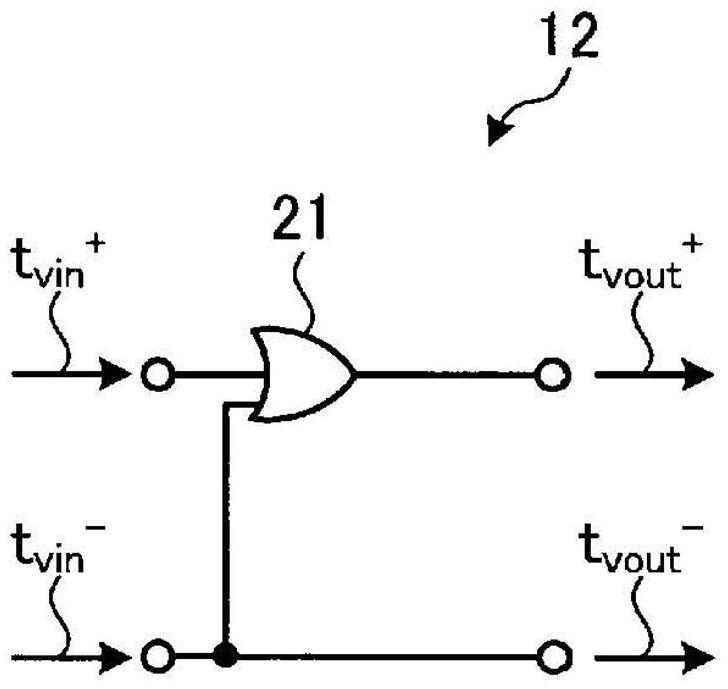

图4是示出根据本公开的第一实施方式的神经网络设备的激活函数电路(activation function circuit)的配置的示图。

图5是示出根据本公开的第一实施方式的神经网络设备的激活函数电路的操作定时的时序图。

图6是示出根据本公开的第一实施方式的神经网络设备的激活函数电路的操作定时的时序图。

图7是示出根据本公开的第一实施方式的神经网络设备的激活函数电路的输入定时与输出定时之间的关系的示图。

图8是示出根据本公开的第一实施方式的神经网络设备的最大池化电路(MaxPooling circuit)的配置的示图。

图9是示出根据本公开的第一实施方式的神经网络设备的最大池化电路的操作定时的时序图。

图10是示出根据本公开的第二实施方式的激活函数电路的配置的示图。

图11是示出根据本公开的第三实施方式的激活函数电路的配置的示图。

图12是示出根据本公开的第四实施方式的激活函数电路的配置的示图。

图13是示出根据本公开的第五实施方式的最大池化电路的配置的示图。

图14是示出根据本公开的第六实施方式的最大池化电路的配置的示图。

图15是示出根据本公开的第七实施方式的最大池化电路的比较器的配置的示图。

具体实施方式

下面将参考附图对本公开的实施方式进行详细描述。在下列的各个实施方式中,以相同参考符号表示相同的部件,并且将省去其重复性描述。

(第一实施方式)

[根据第一实施方式的神经网络设备的配置]

图1是示出根据本公开的第一实施方式的神经网络设备的配置的示图。神经网络设备1包括第一层电路2、第一层间电路3、第二层电路4以及第二层间电路5。

神经网络设备1是本公开的信号处理设备的实例。

在第一实施方式中,神经网络设备1包括两层,即,第一层电路2和第二层电路4。然而,本公开并不局限于该配置。神经网络设备1可以包括三层或多层。进一步地,神经网络设备1可以形成在半导体芯片(裸片)上。

第一层电路2对多个输入信号x

第一层电路2包括多个乘积累加运算电路11。第一层间电路3包括多个激活函数电路12和多个最大池化电路13。第二层电路4包括多个乘积累加运算电路11。第二层间电路5包括多个激活函数电路12和多个最大池化电路13。

激活函数电路12是本公开的信号处理电路的实例。最大池化电路13是本公开的第二信号处理电路的实例。乘积累加运算电路11是本公开的乘积累加运算电路的实例。

[乘积累加运算电路的配置与操作]

图2是示出根据本公开的第一实施方式的神经网络设备的乘积累加运算电路的配置的示图。乘积累加运算电路11包括第一乘积累加运算电路11p和第二乘积累加运算电路11m。

乘积累加运算电路11是通过正绝对值信号t

第一乘积累加运算电路11p包括一端电连接至标准电位的电容器Cp。标准电位的实例是接地电位,但本公开并不局限于此。进一步地,电容器Cp可以是另一存储设备(例如,MOS晶体管)的栅极电容。

第一乘积累加运算电路11p包括电阻器Rp

第一乘积累加运算电路11p包括多个电阻器Rp

因此,第一乘积累加运算电路11p执行下列式子(1)的乘积累加运算。在式子(1)中,w

电阻器Rp

第一乘积累加运算电路11p包括比较器CMPp。当电容器Cp的电压低于阈电压Vth时,比较器CMPp输出低电平信号t

乘积累加运算结果越大,电容器Cp的电压上升越快,导致第一乘积累加运算电路11p输出高电平信号t

第二乘积累加运算电路11m包括一端电连接至标准电位的电容器Cm。电容器Cm可以是另一存储设备(例如,MOS晶体管)的栅极电容。

第二乘积累加运算电路11m包括电阻器Rm

第二乘积累加运算电路11m包括多个电阻器Rm

因此,第二乘积累加运算电路11m执行上述式子(1)的乘积累加运算。在第二乘积累加运算电路11m中,w

电阻器Rm

第二乘积累加运算电路11m包括比较器CMPm。当电容器Cm的电压低于阈电压Vth时,比较器CMPm输出低电平信号t

乘积累加运算结果越大,电容器Cm的电压上升越快,导致第二乘积累加运算电路11m输出高电平信号t

乘积累加运算电路11通过信号t

[激活函数电路的配置与操作]

激活函数电路12是对信号t

图3是示出ReLU的输入/输出特征的示图。如图3的图表101中示出的,当输入值小于0时,输出值是0。当输入值是0或更大时,输出值等于输入值。

图4是示出根据本公开的第一实施方式的神经网络设备的激活函数电路的配置的示图。激活函数电路12包括逻辑电路。

将逻辑电路粗略地分类成组合电路和时序电路。组合电路是其中当前输出信号仅取决于当前输入信号并且并不取决于之前输入信号的电路。组合电路的实例包括逻辑或电路(或门电路)和逻辑与电路(与门电路)。时序电路(sequential circuit)是其中当前输出信号取决于当前输入信号和之前输入信号两者的电路。时序电路的实例包括D型触发器和RS型触发器。

如图4中示出的,激活函数电路12包括逻辑或电路(或门电路)21,其为组合电路。

逻辑或电路21是本公开的第一逻辑电路的实例。

逻辑或电路21对信号t

激活函数电路12将信号t

图5是示出根据本公开的第一实施方式的神经网络设备的激活函数电路的操作定时的时序图。具体地,图5是示出当信号t

信号t

信号t

此外,乘积累加运算电路11通过定时t

因为信号t

因为信号t

因此,信号t

图6是示出根据本公开的第一实施方式的神经网络设备的激活函数电路的操作定时的时序图。具体地,图6是示出当信号t

信号t

信号t

此外,乘积累加运算电路11通过定时t

因为信号t

因为信号t

因此,在同一定时输出信号t

图7是示出根据本公开的第一实施方式的神经网络设备的激活函数电路的输入定时与输出定时之间的关系的示图。

在信号t

在其中信号t

如上所述,激活函数电路12能够在不需要使用时间-数字转换器电路的情况下执行激活函数处理。进一步地,激活函数电路12能够在不需要使用数字-时间转换器电路的情况下将由激活函数运算产生的信号输出至时序电路。以这种方式,激活函数电路12能够消除对时间-数字转换器电路和数字-时间转换器电路的需求。相应地,激活函数电路12能够抑制时间-数字转换器电路和数字-时间转换器电路的功耗。

进一步地,激活函数电路12能够消除对时间-数字转换器电路和数字-时间转换器电路的需求。相应地,激活函数电路12能够使得神经网络设备1的电路缩小由时间-数字转换器电路和数字-时间转换器电路占据的面积。

进一步地,通过组合电路(第一实施方式中的逻辑或电路21)能够获得激活函数电路12。相应地,与经过时间-数字转换之后通过数字信号处理电路实现非线性函数处理的情况相比较,激活函数电路12能够使得电路减小尺寸并且抑制功耗。

进一步地,激活函数电路12能够抑制功耗并且使得电路减小尺寸。相应地,激活函数电路12能够使得神经网络设备1的层数增加。

[最大池化电路的配置与操作]

最大池化电路13是执行提取并且输出两个激活函数电路12的输出信号中的较大信号的最大池化处理的电路。

图8是示出根据本公开的第一实施方式的神经网络设备的最大池化电路的配置的示图。

最大池化电路13包括两个第一电路41-1和41-2以及第二电路42。

一个电路,即,第一电路41-1包括输出信号S

进一步地,第一电路41-1包括第二时间长度信号输出电路52,第二时间长度信号输出电路52在基于作为使能控制信号的信号S

信号S

第一时间长度信号输出电路51是异或电路(XOR门电路),其是对信号S

第二时间长度信号输出电路52包括基于信号S

充电/放电电路53包括输出参考电位Vref的第一恒定电压源61。进一步地,充电/放电电路53包括具有电连接至第一恒定电压源61的一端和电连接至节点N的另一端的电容器62。

进一步地,充电/放电电路53包括一端电连接至高电位侧的电源电位VDD的第一恒定电流源64。进一步地,充电/放电电路53包括第一开关65,其中,输入/输出路径连接在第一恒定电流源64的另一端与节点N之间,而信号S

进一步地,充电/放电电路53进一步包括第二恒定电流源66,其一端连接至标准电位。进一步地,充电/放电电路53包括第二开关67,其中,输入/输出路径连接在节点N与第二恒定电流源66的另一端之间,而信号S

进一步地,充电/放电电路53包括第三开关63,其中,输入/输出路径连接至电容器62的两端,而作为重置信号的信号S

第二时间长度信号输出电路52包括比较器69,其中,反相输入端子电连接至输出参考电位Vref的第二恒定电压源68,而非反相输入端子电连接至节点N。

比较器69将信号S

另一电路,即,第一电路41-2包括输出信号S

进一步地,第一电路41-2包括第二时间长度信号输出电路52,第二时间长度信号输出电路52在基于信号S

信号S

因为第一电路41-2的电路配置与第一电路41-1的电路配置相似,所以将省去其描述。

第二电路42包括逻辑或电路(或门电路)71,其为对信号S

进一步地,第二电路42包括D型第一触发器72,其为在作为逻辑或电路71的输出信号的信号S

进一步地,第二电路42包括反相电路(非门电路)73,其为使得信号S

在第一实施方式中,第二电路42提取并且输出两个第一电路41-1和41-2的输出信号中的较大信号。然而,本公开并不局限于此。第二电路42可以提取并且输出三个或多个第一电路的输出信号之中的最大信号。例如,逻辑或电路71可以是3-输入逻辑或电路,并且三个第一电路可以电连接至逻辑或电路71的三个输入部。

图9是示出根据本公开的第一实施方式的神经网络设备的最大池化电路的操作定时的时序图。

从定时0至预定定时T的时间段是重置时间段。在从定时t

当信号S

类似地,第一电路41-2中的第三开关63接通,从而使得电容器62的两端发生短路。相应地,作为节点N的电位的信号S

从定时T至预定定时2T的时间段与充电周期对应。

在定时t

在定时t

在定时t

此处,当第一恒定电流源64的电流值是Icharge时,电容器62的电容值是C,并且从定时t

Vc=(Icharge/C)*ΔTcharge+Vref (3)

在定时t

此时,通过上述式子(3)表达第一电路41-2的电容器62的电压Vc。

将从定时2T至预定定时3T的时间段定义为输出时间段。

在定时2T,作为使能控制信号的信号S

在第一电路41-1中,信号S

类似地,在第一电路41-2中,信号S

在第二电路42中,因为信号S

在定时t

此处,当第二恒定电流源66的电流值是Idischarge时,通过下列式子(4)表达从定时2T至定时t

ΔTdischarge

=(Vc-Vref)/(Idischarge/C)

=(Icharge/Idischarge)*ΔTcharge (4)

因此,时间长度ΔTdischarge与时间长度ΔTcharge直接成比例。即,放电时间与充电时间直接成比例。

当Idischrage=Icharge时,充电/放电电路53能够将时间长度ΔTdischarge设置为等于时间长度ΔTcharge。即,充电/放电电路53能够将放电时间设置为等于充电时间。

当Idischrage 在定时t 此时,通过上述式子(4)表达从定时2T至定时t 在第二电路42中,因为信号S 因为信号S 因为信号S 在脉冲信号(信号S 如上所述,当将作为一个激活函数电路12的输出信号的信号S 最大池化电路13能够在不需要使用时间-数字转换器电路的情况下执行最大池化处理。进一步地,最大池化电路13能够在不需要使用数字-时间转换器电路的情况下将最大池化结果信号输出至时序电路。同样,最大池化电路13能够消除对时间-数字转换器电路和数字-时间转换器电路的需求。相应地,最大池化电路13能够抑制时间-数字转换器电路和数字-时间转换器电路的功耗。 此外,最大池化电路13能够消除对时间-数字转换器电路和数字-时间转换器电路的需求。相应地,最大池化电路13能够使得神经网络设备1的电路缩小由时间-数字转换器电路和数字-时间转换器电路占据的面积。 进一步地,最大池化电路13能够抑制功耗并且减小电路尺寸。相应地,最大池化电路13能够使得神经网络设备1的层数增加。 进一步地,当最大池化电路13进行调整以实现Idischrage [总结] 如上所述,激活函数电路12能够在不需要使用时间-数字转换器电路的情况下执行激活函数处理。进一步地,激活函数电路12能够在不需要使用数字-时间转换器电路的情况下将由激活函数运算产生的信号输出至时序电路。以这种方式,激活函数电路12能够消除对时间-数字转换器电路和数字-时间转换器电路的需求。相应地,激活函数电路12能够抑制时间-数字转换器电路和数字-时间转换器电路的功耗。 进一步地,激活函数电路12能够消除对时间-数字转换器电路和数字-时间转换器电路的需求。相应地,激活函数电路12能够使得神经网络设备1的电路缩小由时间-数字转换器电路和数字-时间转换器电路占据的面积。 进一步地,通过组合电路(第一实施方式中的逻辑或电路21)能够获得激活函数电路12。相应地,与在时间-数字转换之后通过数字信号处理实现非线性函数处理的情况相比较,激活函数电路12能够减小电路尺寸并且抑制功耗。 进一步地,激活函数电路12能够抑制功耗并且减小电路尺寸。相应地,激活函数电路12能够使得神经网络设备1的层数增加。 (第二实施方式) 图10是示出根据本公开的第二实施方式的激活函数电路的配置的示图。 与第一实施方式的激活函数电路12(参考图4)相比较,激活函数电路12A进一步包括逻辑或电路(或门电路)22。 逻辑或电路22是本公开的第二逻辑电路的实例。 逻辑或电路22对信号t 在激活函数电路12A中,信号t 因此,激活函数电路12A能够抑制信号t 应注意,激活函数电路12A可以包括另一组合电路,例如,缓冲器电路,而非逻辑或电路22。然而,就抑制与逻辑或电路21的延迟时间的差的观点而言,激活函数电路12A优选为包括延迟时间与逻辑或电路21的延迟时间相同的逻辑或电路22。 (第三实施方式) 图11是示出根据本公开的第三实施方式的激活函数电路的配置的示图。 与第一实施方式的激活函数电路12(参考图4)相比较,激活函数电路12B进一步包括组合电路23、第一触发器24、以及第二触发器25。 组合电路23是本公开的第三逻辑电路的实例。第一触发器24是本公开的第一时序电路的实施例。第二触发器25是本公开的第二时序电路的实施例。 组合电路23包括具有以多级连接的多个缓冲器电路(延迟电路)的第一缓冲器电路组26、具有以多级连接的多个缓冲器电路(延迟电路)的第二缓冲器电路组27以及异或电路28。 第一缓冲器电路组26对逻辑或电路21的输出信号进行延迟并且将信号输出至异或电路28的一个输入端子。第二缓冲器电路组27对信号t D型第一触发器24保持逻辑或电路21的输出信号处于组合电路23的输出信号S的上升边缘和下降边缘,并且输出信号t D型第二触发器25保持信号t 组合电路23包括第一缓冲器电路组26和第二缓冲器电路组27,以确保第一触发器24和第二触发器25的设置时间。 第一缓冲器电路组26对逻辑或电路21的输出信号进行延迟,而第二缓冲器电路组27对信号t 这确保了第一触发器24的设置时间,使得可以可靠地保持逻辑或电路21的输出信号。同样,确保了第二触发器25的设置时间,使得可以可靠地保持信号t 应注意,信号t 在激活函数电路12B中,第一触发器24保持逻辑或电路21的输出信号并且输出信号t 这能够使得激活函数电路12B实现高速神经运算。 (第四实施方式) 图12是示出根据本公开的第四实施方式的激活函数电路的配置的示图。 与第三实施方式的激活函数电路12B(参考图11)相比较,激活函数电路12C进一步包括逻辑或电路22(参考第二实施方式的图10)。与第三实施方式的激活函数电路12B相比较,激活函数电路12C包括组合电路23A、而非组合电路23。 与第三实施方式的组合电路23(参考图11)相比较,组合电路23A包括第二缓冲器电路组27A、而非第二缓冲器电路组27。 在激活函数电路12C中,信号t 因此,优选为将第二缓冲器电路组27A中的缓冲器电路的数量设置为等于第一缓冲器电路组26中的缓冲器电路的数量。如实例中示出的,第一缓冲器电路组26包括三个缓冲器电路,且第二缓冲器电路组27A包括三个缓冲器电路。 激活函数电路12C在操作方面与激活函数电路12B类似。 在第四实施方式中,组合电路23A包括位于异或电路28的输入端子侧的第一缓冲器电路组26和第二缓冲器电路组27A。然而,本公开并不局限于此。组合电路23A可以包括位于异或电路28的输出端子侧的一个缓冲器电路组,而非第一缓冲器电路组26和第二缓冲器电路组27A。这使得可以抑制缓冲器电路的数量。 (第五实施方式) 图13是示出根据本公开的第五实施方式的最大池化电路的配置的示图。 与第一实施方式的最大池化电路13(参考图8)相比较,最大池化电路13A包括第一电路41-1A和41-2A,而非第一电路41-1和41-2。 与第一电路41-1(参考图8)相比较,第一电路41-1A包括第二时间长度信号输出电路52A,而非第二时间长度信号输出电路52。 与第二时间长度信号输出电路52(参考图8)相比较,第二时间长度信号输出电路52A包括充电/放电电路53A,而非充电/放电电路53。 与充电/放电电路53(参考图8)相比较,充电/放电电路53A包括电阻器64A,而非第一恒定电流源64。与充电/放电电路53相比较,充电/放电电路53A包括电阻器66A,而非第二恒定电流源66。 因为第一电路41-2A的电路配置与第一电路41-1A的电路配置相似,所以将省去其描述。 当第一开关65接通时,经由电阻器64A从电源电位VDD对电容器62进行充电。进一步地,当第二开关67接通时,经由电阻器66A对电容器62进行放电。 此处,电阻器64A的电阻值是Rcharge,电阻器66A的电阻值是Rdischarge,并且电容器62的电容值是C。由电阻器64A和电容器62形成的RC串联电路的时间常数是(Rcharge*C)。由电阻器66A和电容器62形成的RC串联电路的时间常数是(Rdischarge*C)。当充电时间充分短于时间常数(Rcharge*C)并且放电时间充分短于时间常数(Rdischarge*C)时,下列式子(5)和(6)保持为近似方程式。 Vc≈((VDD/Rcharge)/C)*ΔTcharge+Vref (5) ΔTdischarge ≈(Vc-Vref)/(VDD/Rdischarge/C) =(Rdischarge/Rcharge)*ΔTcharge (6) 以这种方式,最大池化电路13A能够执行与最大池化电路13相似的运算。 进一步地,当调整为Rcharge (第六实施方式) 图14是示出根据本公开的第六实施方式的最大池化电路的配置的示图。 与第一实施方式的最大池化电路13(参考图8)相比较,最大池化电路13B包括第一电路41-1B和41-2B,而非第一电路41-1和41-2。 与第一电路41-1(参考图8)相比较,第一电路41-1B包括第二时间长度信号输出电路52B,而非第二时间长度信号输出电路52。 与第二时间长度信号输出电路52(参考图8)相比较,第二时间长度信号输出电路52B包括充电/放电电路53B,而非充电/放电电路53。 与充电/放电电路53(参考图8)相比较,充电/放电电路53B不包括第一恒定电压源61或第二恒定电压源68。 在第一电路41-1B和第一电路中41-2B两者中,从一个第一恒定电压源61向充电/放电电路53B的电容器62的一端和比较器69的反相端子供应参考电位Vref。 因此,与最大池化电路13相比较,最大池化电路13B能够减少恒定电压源的数量。 (第七实施方式) 图15是示出根据本公开的第七实施方式的最大池化电路的比较器的配置的示图。 在上述各个实施方式中,在能够容忍由于比较器69的偏差而产生的时间长度误差的情况下,比较器69不需要具有偏差去除功能。然而,如图15中示出的,在不可容忍由于比较器69的偏差而产生的时间长度误差的情况下,优选为比较器69具有偏差去除功能。 比较器69包括第一电路91、第二电路92以及第三电路93。 为差分对电路的第一电路91包括电容器121。第一电路91进一步包括N沟道晶体管122、123以及125。第一电路91进一步包括P沟道晶体管124和126。 晶体管122的源极连接至标准电位。将预定偏置电位Vbias输入至晶体管122的栅极。晶体管122的漏极电连接至晶体管123的源极和晶体管125的源极。 经由作为输入电容器的电容器121将信号S 晶体管124的源极电连接至电源电位VDD。 将参考电位Vref输入至晶体管125的栅极。晶体管125的漏极电连接至节点N 晶体管126的漏极电连接至节点N 第二电路92包括N沟道晶体管127、P沟道晶体管129以及电容器128。 晶体管127的源极电连接至标准电位。将偏置电位Vbias输入至晶体管127的栅极。晶体管127的漏极电连接至节点N 晶体管129的漏极电连接至节点N 电容器128的一端电连接至节点N 开关136电连接在晶体管123的栅极与节点N 第三电路93包括开关130、133以及135、N沟道晶体管131、P沟道晶体管132以及反相电路(反相器电路)134。 晶体管131的源极经由开关130电连接至标准电位。将作为使能控制信号的信号S 晶体管132的漏极连接至节点N 反相电路134使信号S 第三电路93从节点N 在信号S 在从第二电路92的节点N 在第三电路93中,当作为使能控制信号的信号S 在第三电路93中,当作为使能控制信号的信号S 当作为使能控制信号的信号S 进一步地,比较器69使用作为重置信号的信号S 由此,比较器69先将表示比较器69的偏差信息的电荷保存在电容器121中。之后,比较器69执行信号S 本说明书中描述的效果仅是实施例,并且由此,可以存在其他效果,并不局限于所例证的效果。 应注意,本技术还能够具有下列配置。 (1)一种信号处理电路, 在第一输入信号改变的第一定时早于或与第二输入信号改变的第二定时相同的情况下,在第一定时输出第一输出信号并且在第二定时输出第二输出信号,并且在第一定时晚于第二定时的情况下,在第二定时输出第一输出信号和第二输出信号。 (2)根据(1)所述的信号处理电路,包括: 第一逻辑电路,对第一输入信号和第二输入信号执行逻辑运算并且输出第一输出信号。 (3)根据(2)所述的信号处理电路, 其中,第一逻辑电路是对第一输入信号和第二输入信号执行逻辑或运算并且输出第一输出信号的逻辑或电路。 (4)根据(2)或(3)所述的信号处理电路, 其中,输出第二输入信号作为第二输出信号。 (5)根据(2)或(3)所述的信号处理电路,进一步包括: 第二逻辑电路,对第二输入信号执行逻辑运算并且输出第二输出信号。 (6)根据(5)所述的信号处理电路, 其中,第二逻辑电路的电路延迟时间与第一逻辑电路的电路延迟时间相同。 (7)根据(5)或(6)所述的信号处理电路, 其中,第二逻辑电路是对第二输入信号和第二输入信号执行逻辑或运算并且输出第二输出信号的逻辑或电路。 (8)根据(2)至(7)中任一项所述的信号处理电路,进一步包括: 第三逻辑电路,对第一输出信号和第二输出信号执行逻辑运算并且输出指示保持第一输出信号和第二输出信号的定时的定时信号; 第一时序电路,基于定时信号保持并且输出第一输出信号;以及 第二时序电路,基于定时信号保持并且输出第二输出信号。 (9)根据(8)所述的信号处理电路, 其中,第一时序电路和第二时序电路中的每个时序电路是触发器。 (10)一种信号处理设备,包括: 乘积累加运算电路,执行分别使多个信号与第一组的系数相乘并且相加的第一乘积累加运算并且输出第一信号,并且执行分别使多个信号与第二组的系数相乘并且相加的第二乘积累加运算并且输出第二信号;和 信号处理电路,在第一信号改变的第一定时早于或与第二信号改变的第二定时相同的情况下,在第一定时输出第一输出信号并且在第二定时输出第二输出信号,并且在第一定时晚于第二定时的情况下,在第二定时输出第一输出信号和第二输出信号。 (11)根据(10)所述的信号处理电路,进一步包括: 第二信号处理电路,电连接至多个信号处理电路并且输出第一输出信号和第二输出信号,第一输出信号和第二输出信号在第一输出信号改变的第一定时和第二输出信号改变的第二定时之间具有最长时间长度。 (12)根据(10)或(11)所述的信号处理设备, 其中,第一组的系数是分别表示正负载的系数;并且 第二组的系数是分别表示负负载的绝对值的系数。 (13)一种信号处理方法,包括: 在第一输入信号改变的第一定时早于或与第二输入信号改变的第二定时相同的情况下,在第一定时输出第一输出信号并且在第二定时输出第二输出信号;并且 在第一定时晚于第二定时的情况下,在第二定时输出第一输出信号和第二输出信号。 参考标号列表 1 神经网络设备 2 第一层电路 3 第一层间电路 4 第二层电路 5 第二层间电路 11 乘积累加运算电路 11p 第一乘积累加运算电路 11m 第二乘积累加运算电路 12 激活函数电路 12A 激活函数电路 12B激活函数电路 12C 激活函数电路 13 最大池化电路 13A 最大池化电路 13B 最大池化电路 21 逻辑或电路 22 逻辑或电路 23 组合电路 23A 组合电路 24 第一触发器 25第二触发器 26 第一缓冲器电路组 27 第二缓冲器电路组 27A 第二缓冲器电路组 28 异或电路 41-1 第一电路 41-1A第一电路 41-1B 第一电路 41-2 第一电路 41-2A 第一电路 41-2B 第一电路 42 第二电路 51 第一时间长度信号输出电路 52 第二时间长度信号输出电路 52A 第二时间长度信号输出电路 52B 第二时间长度信号输出电路 53 充电/放大电路 53A 充电/放大电路 53B 充电/放大电路 69 比较器 91 第一电路 92 第二电路 93 第三电路。

- 信号处理电路、信号处理设备以及信号处理方法

- 一种信号处理电路、终端设备及信号处理方法