具有裸片特定信息图案的半导体封装

文献发布时间:2023-06-19 10:00:31

技术领域

本技术针对具有裸片特定信息图案的半导体封装。更特定地,本技术的一些实施例涉及一种在其上具有机器可读图案的半导体封装,所述机器可读图案用于指示位于所述半导体封装中的半导体裸片的合适信息(例如操作参数)。

背景技术

包含存储器芯片、微处理器芯片、逻辑芯片及成像器芯片的封装式半导体裸片通常包含安装在衬底上且包封于塑料保护覆盖中的半导体裸片。单个半导体裸片可包含功能特征,例如存储器单元、处理器电路、成像器装置及其它电路系统,以及电连接到功能特征的接合垫。为了恰当地操作半导体裸片,例如,必须在裸片级别优化用于操作半导体裸片的某些裸片特定参数,例如电流、电压、电阻参考值等,以解决工艺变化。传统上,此类特定于芯片的参数存储在实现特殊非易失性元件中,例如熔丝或反熔丝,所述非易失性元件在芯片本身中实现。此可能为昂贵且不可靠的。

发明内容

本申请案的一个方面是针对一种半导体装置封装,其包括:第一表面及与所述第一表面相对的第二表面;半导体裸片,其定位于所述第一表面与所述第二表面之间;及图案,其在所述第一表面的指定区域中,所述图案包含多个位区域,所述位区域中的每一个表示第一位信息或第二位信息,所述图案呈现用于操作所述半导体裸片的信息,所述图案经配置以由图案扫描器读取。

本申请案的另一方面是针对一种提供与半导体裸片相关联的信息的方法,其包括:将所述半导体裸片定位在半导体装置封装中,所述半导体装置封装具有第一表面;在所述第一表面上确定指定区域;及在所述指定区域中形成图案,所述图案包含多个位区域,所述位区域中的每一个表示第一位信息或第二位信息,所述图案呈现关于操作所述半导体裸片的信息,所述图案经配置以由图案扫描器读取。

附图说明

参考以下图式可更好地理解本技术的许多方面。图式中的组件不一定按比例缩放。相反,重点在于说明本技术的原理。

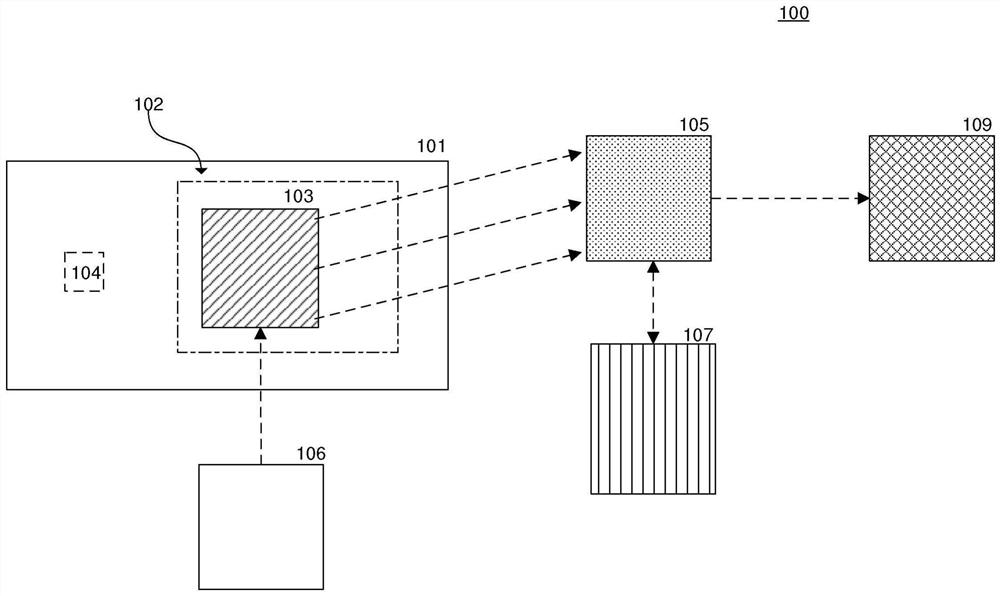

图1为根据本技术的实施例的用于通过使用半导体装置封装上的图案递送信息的系统100的示意图。

图2为根据本技术的实施例的示出图案中的元素的图像。

图3A到3E为说明根据本技术的实施例的用于编码/解码的方法的示意图。

图4A到4C为说明根据本技术的实施例的用于通过使用区段进行编码/解码的方法的示意图。

图5A到5D为说明根据本技术的实施例的用于通过使用区段进行编码/解码的方法的示意图。

图6A到6B为说明根据本技术的实施例的用于编码/解码的方法的示意图。

图7A到7C为说明根据本技术的实施例的用于编码/解码的方法的示意图。

图8为说明根据本发明技术的实施例的并入有半导体组合件的系统的框图。

图9为说明根据本技术的实施例的方法的流程图。

具体实施方式

下文描述堆叠式半导体裸片封装的几个实施例的具体细节以及制造此类裸片封装的方法。术语“半导体装置”通常是指包含一或多种半导体材料的固态装置。半导体装置可包含例如从晶片或衬底分离的半导体衬底、晶片或裸片。在整个本发明中,一般在半导体装置的上下文中描述半导体裸片,但不限于此。

术语“半导体装置封装”可是指将一或多个半导体装置并入到共用封装中的布置。半导体封装可包含部分或完全囊封至少一个半导体装置的外壳或壳体。半导体装置封装还可包含插入衬底,所述插入衬底承载一或多个半导体装置且附接到壳体或以其它方式并入到壳体中。术语“半导体装置封装组合件”可是指包含多个堆叠式半导体装置封装的组合件。如本文中所使用,术语“垂直”、“侧向”、“上部”及“下部”可指代半导体装置或封装中的特征鉴于图中所展示的定向的相对方向或位置。然而,这些术语应被广义地解释为包含具有其它定向(例如,倒置或倾斜定向)的半导体装置。

图1为根据本技术的实施例的用于通过使用半导体装置封装上的图案递送信息的系统100的示意图。如所展示,系统100包含半导体装置封装101、半导体装置封装101中的半导体裸片104、半导体装置封装101的外表面(例如,可从外部接达的表面)上的图案103、图案读取器105(例如,光学读取器、相机、激光扫描器等)、控制器107及数据存储装置109。在一些实施例中,半导体装置封装101可为半导体装置封装组合件的一部分(例如,最上部分),其包含多个堆叠式半导体装置封装。

如在图1中所展示,半导体装置封装101具有用于显示图案103的指定区域102。在一些实施例中,指定区域102位于半导体装置封装101的顶表面处。在一些实施例中,指定区域102可位于半导体装置封装101的底表面处。在一些实施例中,指定区域102可位于半导体装置封装101的侧表面处。在一些实施例中,半导体装置封装101可具有在不同位置处(例如,在顶表面处的两个不同位置;在侧表面处的一个位置及在底表面处的另一位置;在顶表面处的一个位置及在底表面处的另一位置)的多于一个指定区域102。

图案103经配置以呈现或递送合适信息,例如与半导体装置封装101中的半导体裸片104相关联的信息。与半导体裸片104相关联的信息可包含例如用于操作半导体裸片104的合适的电流、电压、电压调整、延迟、冗余信息、固件指令、通电/断电指令等。与半导体裸片104相关联的信息可用于实现半导体裸片的最优功能性。例如,所述信息可包含电压范围V

在一些实施例中,图案103可包含点与间隔的组合(例如,参见图2)。点与间隔可各自表示位信息“1”或“0”,使得点与间隔的组合可以用于载运信息。在一些实施例中,可通过施加到半导体装置封装101的表面的激光束来形成点。可通过相邻点的空闲区来定义间隔。在一些实施例中,点可彼此重叠(例如,参见图3A、3D、4A、4B、4C及5A到6A)。

在一些实施例中,点可具有(通常)圆形形状。在一些实施例中,点可具有其它合适形状,例如正方形、矩形、三角形、椭圆形或不规则形状。在一些实施例中,可对准点,使得图案读取器105可沿特定方向或沿着特定路径或路线(例如,蛇形线)读取点(并辨识其之间的间隔)。在一些实施例中,可通过印刷工艺(例如,激光印刷工艺)将图案103定位或形成在半导体装置封装101上。在一些实施例中,可通过冲压、蚀刻、雕刻、激光、热成型、施加粘合剂等在半导体装置封装101上定位或形成图案103。

图案读取器105经配置以扫描、读取及/或辨识图案103的点及间隔。在一些实施例中,图案读取器105可为光学扫描器(例如,使用可见光、红外辐射(IR)或其它合适的波长)。在一些实施例中,图案读取器105可为相机。在一些实施例中,图案读取器105可为激光扫描器。图案读取器105可耦合到控制器107并由其控制。例如,控制器107可指示图案读取器105起始读取/辨识过程以读取及分析图案103,且因此获得与图案103相关联的信息。可将与半导体裸片104相关联的信息发送到数据存储装置109以供将来使用。

在一些实施例中,数据存储装置109可为耦合到图案读取器105的存储装置或磁盘驱动器。在一些实施例中,数据存储装置109可为可通信地耦合到图案读取器105(例如,经由例如因特网或内联网的有线或无线网络)的数据库。

在一些实施例中,可将与图案103相关联的信息的至少一部分存储在半导体装置封装101的非易失性组件(例如,熔丝、非易失性存储器等)中。在信息存储在熔丝中的实施例中,半导体装置封装101在通电过程期间将通过从熔丝读取信息来检索信息并将其拷贝到半导体装置封装101的组件(例如,配置锁存器,其提供安全存取)。

在一些实施例中,与图案103相关联的信息可出于安全目的被加密。在一些实施例中,为了解码与图案103相关联的加密信息,可需要关于如何读取/辨识图案103(例如,逐行、逐列、连续路径、点与间隔的大小,等)的指令集。通过此布置,本技术提供通过图案103递送合适信息的安全方式,使得仅经授权操作员/用户/顾客才能存取与图案103相关联的加密信息。

在一些实施例中,可例如在电晶片分选(EWS)测试期间测试半导体裸片104的功能性。在测试期间,可确定一组最优操作/工作参数,例如电压/电流发生器及调节器的修正参数,用于存储器单元冗余的地址等。所述组最优操作/工作参数可存储在数据存储装置109及/或由控制器107控制。在一些实施例中,写入设备106可经配置以在半导体装置封装101已被包装之后在半导体装置封装101的指定区域102中形成图案103。例如,图案103可包含一或多个一维及/或二维码。换句话说,如上文所描述,与半导体裸片104相关联的芯片特定信息可经编码并写入在其封装上以供将来使用。

在一些实施例中,与图案103相关联的信息可包含用户所请求的定制信息。例如,用户可请求半导体装置封装101的制造商在图案103中添加信息,且此类信息可包含例如用户所提供的内部批号/参考号,关于如何操作由用户形成的半导体装置封装101的技术注释,半导体裸片中的固件版本等。通过此布置,本技术使得用户能够在图案103中添加固有的、定制信息。

图2展示根据本技术的实施例的图案201的元件的图像。如所展示,图案201包含矩阵,所述矩阵包含多个点203及没有点203的多个间隔205(例如,仅具有空闲区)。例如,间隔205可在点203中间或由点203界定。在所说明实施例中,图案读取器可将点203辨识为位信息“1”,且将间隔205识别为位信息“0”。图案201还包含水平参考线207及垂直参考线209,所述水平参考线及垂直参考线经配置以指示图案201的边界。例如,当图案读取器读取图案201的每一行中的点203/间隔205时,垂直参考线209可指示图案201的每一行的开始位置。在一些实施例中,当图案读取器读取图案201的每一列中的点203/间隔205时,水平参考线207可指示图案201的每一列的结束位置。通过读取图案201,图案读取器可获得图案201载运的信息。

在图2中所说明的实施例中,点203及间隔205(没有点203)中的每一个表示裸片特定信息的一个位。例如,其可表示半导体裸片中某一位置处需要用不同位置处的正常工作存储器单元替换的故障存储器单元的地址的一个位(例如,所述位可为用于冗余的地址的一部分)。在另一实施例中,点203及间隔205可表示用于调整/微调半导体裸片的内部电路的操作的修整参数位。

图3A到3E为说明根据本技术的实施例的用于编码/解码的方法的示意图。图3A展示具有第一位区域302a及第二位区域302b的图案30。在所说明实施例中,每一位区域302a到302b具有正方形。在其它实施例中,位区域302a到302b可具有其它合适的形状。如所展示,第一位区域302a可包含彼此重叠的多个点303,且第二位区域302b为无点303的间隔305。具有点303的第一位区域302a表示位信息“1”,且界定间隔305的第二位区域302b表示位信息“0”。因此,图案30的第一行(从左到右)表示“11001111”,图案30的第二行(从左到右)表示“01011110”,依此类推。在所说明实施例中,点303具有直径D,且因此具有九个点303的第一位区域302a的长度L可为“2D”(在图3A中,相邻点部分重叠以大体上填充第一位区域302a,在相邻点形成有更多重叠的实施例中,可存在多于9个点以形成具有相同长度L的第一位区域302a)。在所说明实施例中,图案30的有效位区域“L

图3B展示具有多个第一位区域302a及第二位区域302b的图案31。在所说明实施例中,位区域302a到302b具有正方形。然而,在其它实施例中,位区域302a到302b可具有其它合适的形状。如所展示,第一位区域302a可在一个区中包含一个点303(例如,一个象限),而在一起形成正方形位区域的其它部分中包含空闲区(例如,三个象限)。在第二位区域302b中,位区域中的所有区可为空闲的(例如,四个空闲的或空的象限)以界定间隔305。具有点303的第一位区域302a表示位信息“1”,且由间隔305界定的第二位区域302b表示位信息“0”。因此,图案31的第一行(从左到右)表示“00101101”。在所说明实施例中,图案读取器可遵循以下顺序读取图案31:方向D

图3C展示具有平行四边形(例如,菱形)位区域302a到302b的图案32。在所说明实施例中,每一点303具有直径D,且因此每一位区域302a到302b的长度L可为“2D”。位区域302a到302b的高度H为

图案32具有比图案30(图3A)及图案31(图3B)的有效位区域小的有效位区域,且因此具有更高的数据密度。类似于图3A及3B中所论述的实施例,具有点303的第一位区域302a表示位信息“1”,且具有间隔305的第二位区域302b表示位信息“0”。因此,图案32的第一行(从左到右)表示“01011001”。在所说明实施例中,第二、第三及第四行中的位区域302a到302b各自表示位信息“0”。

图3D和3E说明在表示位信息“1”于位信息“0”之间“切换”的图案。在图3D中,图案33具有沿着两个线L

在图3E中,图案34具有多个线303(例如,由多个点形成)及间隔305。图案读取器可以上文关于图3D所描述的方式在D1方向上一次读取两个线L

图4A到4C为说明根据本技术的实施例的用于通过使用区段进行编码/解码的方法的示意图。在图4A中,图案41具有多个点303及间隔305。图案读取器可沿方向LL

在图4B中,图案42具有多个点303及间隔305。图案读取器可沿方向LL

参考图4B,图案读取器可进一步沿方向HH

在图4B的实施例中,位区域402具有正方形。每一点303具有直径D,且因此图案42中的有效位区域为“2D×2D/2”或“2D

图5A到5D为说明根据本技术的实施例的用于通过使用区段进行编码/解码的方法的示意图。在图5A中,图案51可包含多个区段501a到501b(由多个点303形成)及间隔305。区段501a到501b可为垂直区段501a或水平区段501b。垂直区段501a及水平区段501b对应于图案51的每一位区域402中的一对数据“b1、b2”(其具有两个“数据维度”)。更特定地,当图案读取器辨识位区域402中的垂直区段501a时,其在“b1”处表示位信息“1”。当图案读取器未在位区域402中读取垂直区段501a时,其在“b1”处表示位信息“0”。

类似地,当图案读取器辨识位区域402中的水平区段501b时,其在“b2”处表示位信息“1”。当图案读取器未在位区域402中读取水平区段501b时,其在“b2”处表示位信息“0”。通过此布置,与仅使用一个“数据维度”(例如,其仅具有“b1”或“b2”,但不具有两者)的实施例相比,图案51的数据密度可加倍。

在图5B中,图案52可包含多个区段501a(由多个点303形成)及间隔305。在所说明实施例中,区段501可为(第一)对角线区段501x、垂直区段501y或水平区段501z。区段501x、501y及501z对应于图案52的每一位区域402中的数据集“b1、b2、b3”(其具有三个数据维度)。当图案读取器辨识位区域402中的对角线区段501x时,其在“b1”处表示位信息“1”。当图案读取器未在位区域402中读取对角线区段501x时,其在“b1”处表示位信息“0”。

类似地,当图案读取器辨识位区域402中的垂直区段501y时,其在“b2”处表示位信息“1”。当图案读取器未在位区域402中读取垂直区段501y时,其在“b2”处表示位信息“0”。同样地,当图案读取器辨识位区域402中的水平区段501z时,其在“b3”处表示位信息“1”。当图案读取器未在位区域402中读取水平区段501z时,其在“b3”处表示位信息“0”。通过此布置,与仅使用单个数据维度的实施例相比,图案52的数据密度可增加三倍。

参考图5B,在一些实施例中,数据集可具有四个数据维度。即,数据集在图案52的每一位区域402中可为“b1、b2、b3、b4”。可将第二对角线区段501zz添加到山纹所论述的实施例。第二对角线区段501zz对应于第四数据维度“b4”。当图案读取器辨识位区域402中的第二对角线区段501zz时,其在“b4”处表示位信息“1”。当图案读取器未在位区域402中读取第二对角线区段501zz时,其在“b4”处表示位信息“0”。通过此布置,与仅使用单个数据维度的实施例相比,图案52的数据密度可增加四倍。

图5C说明涉及三个数据维度的图案53。图案53具有平行四边形形状的位区域402。因此,图案53的区段501可为部分垂直区段501a,对角线区段501b或水平区段501c。区段501a、501b及501c对应于图案53的每一位区域402中的数据集“b1、b2、b3”(例如,三个数据维度)。

图5D说明涉及流个数据维度的图案54。例如,图案53具有正方形的位区域402。每一位区域402可包含六个区段(四个侧面及两个对角线)。此六个区段对应于具有六个数据维度的数据集“b0、b1、b2、b3、b4、b5”。通过此布置,与仅使用单个数据维度的实施例相比,图案54的数据密度可增加六倍(6倍)。

图6A展示根据本技术的实施例的用于编码/解码的方法的示意图。在图6A中,图案61具有具有六个数据维度(b0到b5)的位区域402。在一些实施例中,图案61可经配置以提供两组垂直值(例如,a、b或c)。通过此布置,图案61可提供9个值组合,例如“aa”、“ab”、“ac”、“ba”、“bb”、“bc”、“ca”、“cb”及“cc”。可通过连续线601(例如,由多个激光点制成)方便地形成图案61。

图6B为说明根据本技术的实施例的用于编码/解码的方法的示意图。如在图6B中所展示,点603的大小以及点603的存在可皆用作表示图案中不同值的因素。例如,两个空闲区可表示值“a”,一个小点及一个大点可表示值“b”或“c”(例如,当小点在顶部时,值为“b”,且当小点在底部时,值为“c”),两个大点可表示值“d”,一个小点及间隔可表示值“e”,依此类推。尽管图6B中的实施例仅展示具有两个不同大小的点,但在其它实施例中,这些点可具有多于两个的不同大小,从而允许增加数目个排列及符号组合。

图7A到7C为说明根据本技术的实施例的用于编码/解码的方法的示意图。在图7A到7C所论述的实施例中,图案71(图7A)、72(图7B)或73(图7C)的位区域701可包含多于一个的点703及/或空闲区705。例如,位区域701可具有总共三个点703及/或空闲区705。如果在位区域701中存在至少两个点703,那么位区域701表示位信息“1”。在其它方面,如果在位区域701中存在少于两个点703,那么位区域701表示位信息“0”。此布置可减少或至少减轻误读点703的风险。

在图7A中,图案71的位区域701可包含在一行中的三个点703及/或空闲区705。在图7B中,图案72的位区域701可包含形成拐角形状的三个点703及/或空区域705。在图7C中,图案73的位区域701可具有三角形形状。在其它实施例中,位区域701可包含其它数目个点703及/或空闲区705,且位区域701可具有其它合适的形状。尽管在图7A到C中位区域701已被描绘为封闭区,但在一些实施例中,位区域701可包括两个或多于两个经间隔分离的区。例如,每一经间隔分离的区可包含一个点703或空闲区705。

图8为说明根据本发明技术的实施例的并入有半导体组合件的系统的框图。上文参考图1到7C描述的半导体装置中的任何一个可并入到大量更大及/或更复杂的系统中的任何一个中,其代表性实例为图8中示意性展示的系统800。系统800可包含处理器801、存储器803(例如,SRAM、DRAM、快闪存储器及/或其它存储器装置),输入/输出装置805及/或其它子系统或组件807。上文参考图1到7C所描述的半导体组合件、装置及装置封装可包含在图8中所展示的任何元件中。在一些实施例中,系统800可包含非易失性存储器,用于存储关于系统800中至少一些组件的裸片特定信息。例如,配置参数(例如,电压、电流、延迟及/或电阻修整参数、冗余地址等)可存储在非易失性存储器中,且在系统800的通电过程处上传到对应组件。所得系统800可经配置以执行多种合适的计算、处理、存储、感测、成像及/或其它功能中的任何一个。因此,系统800的代表实例包含(而不限于)计算机及/或其它数据处理器,例如桌上型计算机、膝上型计算机、因特网器具、手持式装置(例如,掌上型计算机、可佩带式计算机、蜂窝式或移动电话、个人数字助理、音乐播放器等)、平板、多处理器系统、基于处理器或可编程消费性电子装置、网络计算机及小型计算机。系统800的其它代表性实例包含灯、相机、车辆等。关于这些及其它实例,系统800可容纳在单个单元中或分布在多个互连单元上方,例如通过通信网络。因此,系统800的组件可包含本地及/或远程存储器存储装置以及各种各样的合适的计算机可读媒体中的任何一个。

图9为说明根据本技术的实施例的方法的流程图。方法900可由系统(例如,上文所论述的系统100)实施。方法900用于提供或传递关于半导体裸片的裸片特定信息。在框901处,方法900通过将半导体裸片定位在半导体装置封装中而开始。半导体装置封装具有第一表面。在框903处,方法900通过确定第一表面上的指定区域来继续。在框905处,方法900包含在指定区域中形成图案。图案包含多个位区域,且位区域中的每一个表示第一位信息(例如“1”)或第二位信息(例如“0”)。在一些实施例中,图案可与关于操作半导体裸片的信息相关联。在一些实施例中,图案可经配置以由图案扫描器(例如,图案读取器105)读取。

在一些实施例中,位区域中的每一个可包含正方形、三角形或平行四边形。在一些实施例中,位区域中的每一个包含至少一个点或至少一个间隔。

在一些实施例中,图案可包含由多个点形成的至少一个蛇形线。蛇形线可包含(1)表示第一位信息的至少一个第一区段(例如,水平区段);及(2)表示第二位信息的至少一个蛇形线的至少第二区段(例如,垂直区段)。在一些实施例中,位区域中的每一个包含表示第三位信息的第三区段(例如,对角线区段)。

本发明并非意欲为穷尽的或将本技术限制于本文中所揭示的精确形式。尽管本文中出于说明性目的揭示特定实施例,但如所属相关领域的普通技术人员将认识到的,在不脱离本技术的情况下,各种等效修改为可能的。在一些状况下,尚未展示或详细描述众所周知的结构及功能,以避免不必要地使本技术的实施例的描述不清楚。尽管本文中以特定次序呈现方法的步骤时,替代实施例可以不同次序执行步骤。另外,在特定实施例的上下文中所揭示的本技术的某些方面可在其它实施例中组合或消除。此外,虽然在那些实施例的上下文中已揭示与本技术的某些实施例相关联的优点,但其它实施例也可展现出此类优点,且并非所有实施例都必须展现此类优点或本文中揭示属于本技术范围内的其它优点。因此,本发明及相关联技术可囊括未在本文中明确展示或描述的其它实施例。

贯穿本发明,除非上下文另有清楚地指示,否则单数术语“一(a)”、“一(an)”及“所述”包含复数对象。类似地,除非单词“或”在参考两个或多于两个项目的列表时清楚地限于仅意指排斥其它项目的单个项目,否则在此列表中使用“或”将被解释为包含(a)所述列表中的任一单个项目,(b)所述列表中的所有项目或(c)所述列表中的项目的任一组合。另外,通篇中使用术语“包括”以意指至少包含(若干)所叙述的特征,使得不排除任何较大数目个相同特征及/或额外类型的其它特征。本文中对“一个实施例”、“一些实施例”或类似表述的提及意指结合实施例描述的特定特征、结构、操作或特性可包含于本技术的至少一个实施例中。因此,本文中的此类短语或表述的出现未必均指同一实施例。此外,在一或多个实施例中,可以任何适合方式来组合各种特定特征、结构、操作或特性。

从先前内容,可了解,出于说明的目的,本文中已描述本技术的特定实施例,但在不脱离本发明的范围的情况下可进行各种修改。除所附权利要求书之外,本技术不受限制。

- 具有裸片特定信息图案的半导体封装

- 具有取决于在裸片上的位置的定向或几何形状或在支柱与裸片垫片之间形成有图案化结构以用于减少热应力的顺应互连支柱